Near Field Communication (NFC) SmartConnect Module in a single package

Rev. 1.3 — 20 October 2006

**Objective short data sheet**

### 1. General description

PN65K combines in a single package a Near Field Communication (NFC) controller PN531 and a Secure Smart Card controller. They are tied together by the means of external connections for the S<sup>2</sup>C interface and the PN531 is supplying the Smart card controller by the means of a specific internal regulator. The embedded PN531 firmware drives the supply to the Smart*MX* device when required in order to optimize the overall current consumption of the SmartConnect device.

The PN65K can behave as an NFC initiator, working in active or passive mode and when operating in passive mode it can operate as a reader/writer for Mifare or FeliCa contactless smart cards. The Peer to peer functionality is also supported in both active and passive modes.

The PN65K can also operate as a card mode and specially when the combined Smart*MX* device is enabled it can operate as a pure Mifare card or as a fully compliant ISO14443A 3&4 contactless smart card.

| P65xyy(y)z    | SmartConnect Module                                                                               |

|---------------|---------------------------------------------------------------------------------------------------|

| PN65          | SmartConnect module based on the Smard Card IC P5CNaabb plus NFC IC                               |

| x             | defines the NFC IC Pn5xx, e.g. A for PN511, B for PN512, K for PN531, L for PN532                 |

| <b>yy(y</b> ) | Package Type: HN for HVQFN                                                                        |

| Z             | Optional parameter for discrete components in the integrated in the MCM or version identification |

| Example:      |                                                                                                   |

| PN65KHN1      | K: module with PN531, HN: HVQFN package, 1: pure MCM version                                      |

#### **1.1 Naming conventions**

### 2. Features

### 2.1 General

- SmartConnect module integrating NFC controller PN531 device and SmartMX (P5CN072) secure smart card controller in a single package.

- Single package solution for size optimization; needs external antenna matching circuitry, uncoupling capacitors and crystal oscillator.

- Fully NFC IP-1 (ISO18092) compliant

### 2.2 NFC controller

- 80C51 microcontroller core with 32 Kbyte ROM and 1 Kbyte RAM

- Highly integrated analog circuitry to demodulate and decode responses

- Buffered output drivers to connect an antenna with minimum number of external components

- Integrated RF Level detector

- Integrated data mode detector

- Supports ISO 14443A/Mifare

- Typical operating distance in reader/writer mode for communication to a ISO 14443A/Mifare or FeliCa card up to 50 mm depending on the antenna size and tuning

- Typical operating distance in NFCIP-1 mode up to 50 mm depending on the antenna size and tuning and power supply

- Typical operating distance in ISO 14443A/Mifare card or FeliCa card interface mode of about 100 mm depending on the antenna size and tuning and the external field strength

- Supports Mifare Classic encryption in reader/writer mode and Mifare higher transfer speed communication at 212 kbit/s and 424 kbit/s

- Supports contactless communication according to the FeliCa scheme at 212 kBaud and 424 kBaud

- Integrated RF interface for NFCIP-1 up to 424 kBaud

- Possibility to communicate on the RF interface above 424 kBaud using external analog circuitry

- Supported host interfaces

- SPI interface

- I<sup>2</sup>C interface

- High Speed Serial UART (similar to RS232 with 0 and PVDD voltage levels)

- Flexible interrupt using IRQ pin

- Hard reset with low power function

- Power-down mode per embedded firmware

- Programmable timer

- Internal oscillator to connect 27.12 MHz crystal

- 3.3 V power supply when not USB bus powered

- Power Switch for external secure component

- Specific IO ports for external devices control

### 2.3 Secure smart card controller

The device used in this module is the P5CN072 Secure Dual Interface PKI Smart Card Controller which has the following features:

- 72 Kbytes EEPROM

- 160 Kbytes User ROM

- 4608 bytes RAM

- PKI (Public Key Infrastructure) co-processor

- Dual Triple DES Key co-processor

- S<sup>2</sup>C interface to enable secure contact-less communication via NFC (Near Field Communication)

- EEPROM data retention time: 20 years minimum

The P5CN072 is a Secure Dual interface PKI Smart Card Controller of the Smart*MX* platform featuring 160 Kbytes of user ROM, 4608 bytes of RAM and 72 Kbytes of EEPROM which can be used as data memory or as program memory. The non-volatile memory consists of high reliability memory cells to guaranty data integrity which is important especially when EEPROM memory is used as program memory.

Operated both in contact mode (ISO IEC 7816) or S<sup>2</sup>C mode, the user defines the final function of the chip with his chip operating system (COS). This allows the same level of security, functionality and flexibility for the contact interface as well for the S<sup>2</sup>C interface.

The S<sup>2</sup>C technology provides reliable digital communication to the PN531 NFC device to enable secure contactless communication for NFC enabled devices.

The S<sup>2</sup>C interface is connected internally to the internal ISO 14443 CIU. The CIU handles the modulation and demodulation of the S<sup>2</sup>C signals so that a full contact-less communication should be enabled using this interface. The supply VDD is provided by the PN531 voltage regulator.

The P5CN072 offers the same features of contact and contact-less mode handling as the other members of the Smart*MX* family.

Connected via the S<sup>2</sup>C interface to the PN531 NFC controller, P5CN072 is compatible with Mifare reader infrastructure and the optional free of charge emulation mode of Mifare 1K and Mifare 4K enable fast system integration and backward compatibility of standard Mifare and ProX family based cards. The communication on the S<sup>2</sup>C interface support ISO IEC 14443A-3 and ISO IEC 14443A-4 parts.

The on chip hardware is software controlled through special function registers (SFRs). Their function and usage is described in the P5CN072 data sheet.

The P5CN072 is powered by the PN531 device.

# 3. Applications

- mobile phones

- portable equipments (Personal Digital Assistants, notebooks)

- accessories (keyfobs, memory cards)

- consumer devices

# 4. Quick reference data

#### Table 1: Quick reference data

| 0                                                        | Demonstration                                      | O and dition a                                                                                  |                 | <b>T</b> | M    | 11   |

|----------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------|----------|------|------|

| Symbol                                                   | Parameter                                          | Conditions                                                                                      | Min             | Тур      | Max  | Unit |

| V <sub>BUS</sub>                                         | Supply Voltage (non USB mode)                      | $V_{BUS} = D_{VDD}$<br>$V_{SS} = 0 V$                                                           | 2.5             | 3.3      | 3.6  | V    |

| TV <sub>DD</sub> ,<br>AV <sub>DD</sub> , DV <sub>D</sub> | Supply Voltage                                     | $TV_{DD} = AV_{DD} = DV_{DD}$<br>$V_{SS} = 0 V$                                                 | [ <u>1]</u> 2.5 | 3.3      | 3.6  | V    |

| $PV_{DD}$                                                | Supply Voltage for host interface                  | $V_{SS} = 0 V$                                                                                  | 1.6             |          | 3.6  | V    |

| SV <sub>DD</sub>                                         | Supply Voltage for SAM interface                   | V <sub>SS</sub> = 0 V (SV <sub>DD</sub><br>Switch Enabled)                                      | 2.4             |          | 3.6  | V    |

| IH <sub>PD</sub>                                         | Hard Power Down Current<br>(Not powered from USB)  | $AV_{DD} = DV_{DD} =$<br>$TV_{DD} = PV_{DD} = 3 V$ ,<br>RF level detector off                   |                 |          | 10   | μΑ   |

| IS <sub>PD</sub>                                         | Soft Power down Current<br>(Not powered from USB)  | $AV_{DD} = DV_{DD} =$<br>$TV_{DD} = PV_{DD} = 3 V$ ,<br>RF level detector on                    |                 |          | 30   | μΑ   |

| IDV <sub>DD</sub>                                        | Digital Supply Current                             | $AV_{DD} = DV_{DD} =$<br>$TV_{DD} = PV_{DD} = 3 V,R$<br>F level detector on,<br>SVDD switch off | [1]             | 15       |      | mA   |

| ISV <sub>DD</sub>                                        | SV <sub>DD</sub> Supply Current                    | $SV_{DD} = 3 V, SV_{DD}$<br>switch On                                                           |                 |          | 30   | mA   |

| IAV <sub>DD</sub>                                        | Analog Supply Current                              | $AV_{DD} = DV_{DD} =$<br>$TV_{DD} = PV_{DD} = 3 V$ ,<br>RF level detector on                    |                 | 6        |      | mA   |

| ITV <sub>DD</sub>                                        | Transmitter Supply Current                         | During RF<br>Transmission,<br>TV <sub>DD</sub> = 3 V                                            |                 | 60       | 100  | mA   |

| P <sub>tot</sub>                                         | continuous total power dissipation in non USB mode | $T_{amb}$ = -30 to +85 °C                                                                       |                 |          | 0.15 | W    |

| T <sub>amb</sub>                                         | operating ambient temperature                      |                                                                                                 | -30             |          | +85  | °C   |

[1]  $DV_{DD}$ ,  $AV_{DD}$  and  $TV_{DD}$  shall always be at the same supply voltage.

# 5. Ordering information

| Table 2: Ordering | information |                                                                                                                  |         |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------|---------|

| Type number       | Package     |                                                                                                                  |         |

|                   | Name        | Description                                                                                                      | Version |

| PN65KHN1/C2xxyyy  | HVQFN48     | Plastic thermal enhanced very thin package quad flat package; no leads 48 terminals; $7 \times 7 \times 0.85$ mm | SOT619  |

# 6. Block diagram

<u>11111</u>3

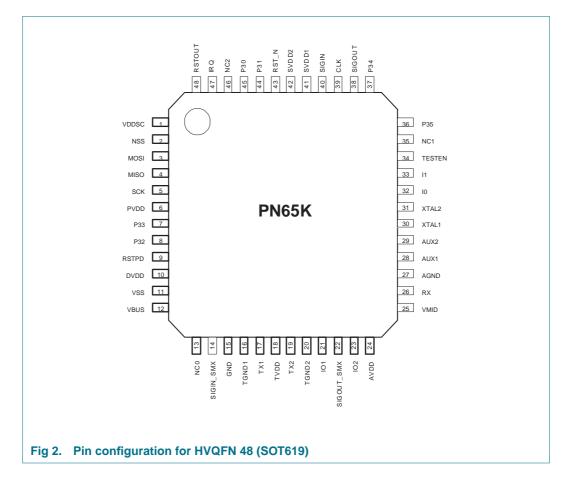

### 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

| Table 3: | Pin descri | ption |                    |                                                                                          |

|----------|------------|-------|--------------------|------------------------------------------------------------------------------------------|

| Symbol   | Pin        | Туре  | Pad Ref<br>Voltage | Description                                                                              |

| VDDSC    | 1          | PWR   |                    | SmartMX supply; to be connected to pins SVDD1 and SVDD2                                  |

| NSS      | 2          | IO    | PVDD               | Not Slave Select.<br>In test mode this signal is used as input and output test signal.   |

| MOSI     | 3          | Ю     | PVDD               | Master Out Slave In.                                                                     |

|          |            |       |                    | In test mode this signal is used as input and output test signal                         |

| MISO     | 4          | IO    | PVDD               | Master In Slave Out.<br>In test mode this signal is used as input and output test signal |

| SCK      | 5          | IO    | PVDD               | Serial interface clock.                                                                  |

|          |            |       |                    | In test mode this signal is used as input and output test signal                         |

| PVDD     | 6          | PWR   |                    | Pad power supply                                                                         |

| Symbol     | Pin | Туре | Pad Ref<br>Voltage | Description                                                                                                                                                                                                                                                                                |

|------------|-----|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P33        | 7   | IO   | PVDD               | General purpose IO signal. Can be used to generate an HZ state on the output of the selected interface for the Host communication and to enter PN531 into Power-down mode without resetting the internal state of PN531. In test mode this signal is used as input and output test signal. |

| P32        | 8   | Ю    | PVDD               | General purpose IO signal. Can also be used as an interrupt source<br>In test mode this signal is used as input and output test signal.                                                                                                                                                    |

| RSTPD      | 9   | I    | PVDD               | Reset and Power Down: When High, internal current sources are switched<br>off, the oscillator is inhibited, and the input pads are disconnected from the<br>outside world.<br>With a positive edge on this pin the internal reset phase starts.                                            |

| DVDD       | 10  | PWR  |                    | Digital Power Supply                                                                                                                                                                                                                                                                       |

| VSS        | 11  | PWR  |                    | Ground for SmartMX                                                                                                                                                                                                                                                                         |

| VBUS       | 12  | PWR  | DVDD               | Supply voltage                                                                                                                                                                                                                                                                             |

| NC0        | 13  |      |                    | Do not connect                                                                                                                                                                                                                                                                             |

| SIGIN_SMX  | 14  | IO   | VDDSC              | S <sup>2</sup> C signal to PN531                                                                                                                                                                                                                                                           |

| GND        | 15  | PWR  |                    | Ground                                                                                                                                                                                                                                                                                     |

| TGND1      | 16  | PWR  |                    | Transmitter ground                                                                                                                                                                                                                                                                         |

| TX1        | 17  | 0    | TVDD               | Transmitter 1: delivers the modulated 13.56 MHZ energy carrier                                                                                                                                                                                                                             |

| TVDD       | 18  | PWR  |                    | Transmitter supply voltage; supply the output stage of TX1 TX2                                                                                                                                                                                                                             |

| TX2        | 19  | 0    | TVDD               | Transmitter 2: delivers the modulated 13.56 MHZ energy carrier                                                                                                                                                                                                                             |

| TGND2      | 20  | PWR  |                    | Transmitter ground                                                                                                                                                                                                                                                                         |

| IO1        | 21  | IO   | VDDSC              | SmartMX: Input/Output 1 for serial data                                                                                                                                                                                                                                                    |

| SIGOUT_SMX | 22  | I    | VDDSC              | S <sup>2</sup> C signal from the PN531                                                                                                                                                                                                                                                     |

| 102        | 23  | IO   | VDDSC              | SmartMX: Input/Output 2for serial data                                                                                                                                                                                                                                                     |

| AVDD       | 24  | PWR  |                    | Analog power supply                                                                                                                                                                                                                                                                        |

| VMID       | 25  | PWR  | AVDD               | Internal Reference Voltage: This pin delivers the internal reference voltage.                                                                                                                                                                                                              |

| RX         | 26  | I    | AVDD               | Receiver Input: Input pin for the reception signal, which is the load modulated 13.56 MHZ energy carrier from the antenna circuit.                                                                                                                                                         |

| AGND       | 27  | PWR  |                    | Analog Ground                                                                                                                                                                                                                                                                              |

| AUX1       | 28  | 0    | DVDD               | Auxiliary Output: This pin delivers analog and digital test signals.                                                                                                                                                                                                                       |

| AUX2       | 29  | 0    | DVDD               | Auxiliary Output: This pin delivers analog and digital test signals.                                                                                                                                                                                                                       |

| XTAL1      | 30  | I    | AVDD               | Crystal Oscillator Input: input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock ( $f_{osc} = 27.12$ MHZ).                                                                                                                       |

| XTAL2      | 31  | 0    | AVDD               | Crystal Oscillator output: Output of the inverting amplifier of the oscillator.                                                                                                                                                                                                            |

| 10         | 32  | I    | DVDD               | Interface mode lines: selects the used host interface.                                                                                                                                                                                                                                     |

|            |     |      |                    | In test mode I0 is used as test signals.                                                                                                                                                                                                                                                   |

| 11         | 33  | I    | DVDD               | Interface mode lines: selects the used host interface.                                                                                                                                                                                                                                     |

|            |     |      |                    | In test mode I0 is used as test signals.                                                                                                                                                                                                                                                   |

| TESTEN     | 34  | I    | DVDD               | Test enable pin:<br>When set to 1 enable the test mode.<br>When set to 0 reset the TCB and disable the access to the test mode.                                                                                                                                                            |

| NC1        | 35  |      |                    | Do not connect                                                                                                                                                                                                                                                                             |

| P35        | 36  | IO   | DVDD               | General purpose IO signal.                                                                                                                                                                                                                                                                 |

| Table 3: | Pin desc | riptionc | ontinued           |                                                                                                                                                                                                 |

|----------|----------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol   | Pin      | Туре     | Pad Ref<br>Voltage | Description                                                                                                                                                                                     |

| P34      | 37       | IO       | SVDD               | General purpose IO signal.                                                                                                                                                                      |

| SIGOUT   | 38       | 0        | SVDD               | Contactless communication interface output: delivers a serial data stream according to NFCIP-1 and output signal for the SAM. In test mode this signal is used as test signal output.           |

| CLK      | 39       | I        | VDDSC              | SMX Clock input                                                                                                                                                                                 |

| SIGIN    | 40       | I        | SVDD               | Contactless communication interface input: accepts a digital, serial data stream according to NFCIP-1 and input signal from the SAM. In test mode this signal is used as test signal input.     |

| SVDD1    | 41       | PWR      |                    | Output power for Smart <i>MX</i> power supply. Switched on by Firmware with an overload detection. Used as a reference voltage for SAM communication.                                           |

| SVDD2    | 42       | PWR      |                    | Output power for Smart <i>MX</i> power supply. Switched on by Firmware with an overload detection. Used as a reference voltage for SAM communication.                                           |

| RSTN     | 43       | I        | VDDSC              | SmartMX reset input; active low                                                                                                                                                                 |

| P31      | 44       | IO       | PVDD               | General purpose IO signal.Can be configured to act either as TX line of the second serial interface or general purpose IO.<br>In test mode this signal is used as input and output test signal. |

| P30      | 45       | IO       | PVDD               | General purpose IO signal.Can be configured to act either as TX line of the second serial interface or general purpose IO.<br>In test mode this signal is used as input and output test signal. |

| NC2      | 46       |          |                    | Do not connect                                                                                                                                                                                  |

| IRQ      | 47       | 0        | PVDD               | Interrupt request: Output to signal an interrupt event to the host (Port 7 bit 0)                                                                                                               |

| RSTOUT   | 48       | IO       | PVDD               | Output reset signal. When Low it indicates that the circuit is in reset state.                                                                                                                  |

# 8. Limiting values

#### Table 4: Limiting values

| In accordance with the Absolute Ma | aximum Rating System (IEC 60134). | Voltages are referenced to VSS ( | ground = $0 V$ ). |

|------------------------------------|-----------------------------------|----------------------------------|-------------------|

| Symbol                                                                                        | Parameter                                                                       | Conditions                        | Min  | Max         | Unit |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|------|-------------|------|

| $\begin{array}{l} PV_{DD},\\ SV_{DD},\\ TV_{DD},\\ AV_{DD},\\ DV_{DD}, \ V_{BUS} \end{array}$ | Supply voltage                                                                  |                                   | -0.5 | +4.0        | V    |

| V <sub>DDSC</sub>                                                                             | Supply voltage                                                                  |                                   | -0.5 | +6.0        | V    |

| P <sub>tot</sub>                                                                              | Total power dissipation per package $(V_{BUS}$ and $DV_{DD}$ in short cut mode) |                                   | -    | <tbd></tbd> | W    |

| I <sub>TX1</sub>                                                                              | Maximum current in transmitter TX1                                              |                                   | -100 | 100         | mA   |

| I <sub>TX2</sub>                                                                              | Maximum current in transmitter TX2                                              |                                   | -100 | 100         | mA   |

| T <sub>stg</sub>                                                                              | Storage temperature range                                                       |                                   | -55  | 150         | °C   |

| TJ                                                                                            | Junction temperature range                                                      |                                   |      | 100         | °C   |

| V <sub>ESD</sub>                                                                              | Electrostatic discharge voltage on all<br>pins                                  |                                   |      | ± 2.0       | kV   |

| ESDH                                                                                          | ESD Susceptibility (Human Body model)                                           | 1500 Ωm, 100pF;<br>JESD22-A114-B  |      | 2           | KV   |

| ESDM                                                                                          | ESD Susceptibility (Machine model)                                              | 0.75 mH, 200 pF;<br>JESD22-A114-A |      | 200         | V    |

# 9. Recommended operating conditions

| Table 5:                                                                          | Operating conditions                                                  |                                                 |     |            |     |      |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|-----|------------|-----|------|

| Symbol                                                                            | Parameter                                                             | Conditions                                      | Min | Тур        | Max | Unit |

| TV <sub>DD,</sub><br>AV <sub>DD</sub> ,<br>DV <sub>DD</sub> ,<br>V <sub>BUS</sub> | Supply voltage                                                        | $TV_{DD} = AV_{DD} = DV_{DD}$<br>$V_{SS} = 0 V$ | 2.5 | 3.3        | 3.6 | V    |

| $PV_{DD}$                                                                         | Supply voltage for host interface                                     | $V_{SS} = 0 V$                                  | 1.6 | 1.8 to 3.3 | 3.6 | V    |

| SV <sub>DD</sub> ,<br>V <sub>DDSC</sub>                                           | Supply voltage for Smart card device                                  | V <sub>SS</sub> = 0 V<br>Sam_switch_en set to 1 | 2.4 | 3.3        | 3.6 | V    |

| T <sub>amb</sub>                                                                  | Operating ambient temperature<br>(ISO 7816 or ISO 14443<br>operation) |                                                 | -15 | +25        | +85 | °C   |

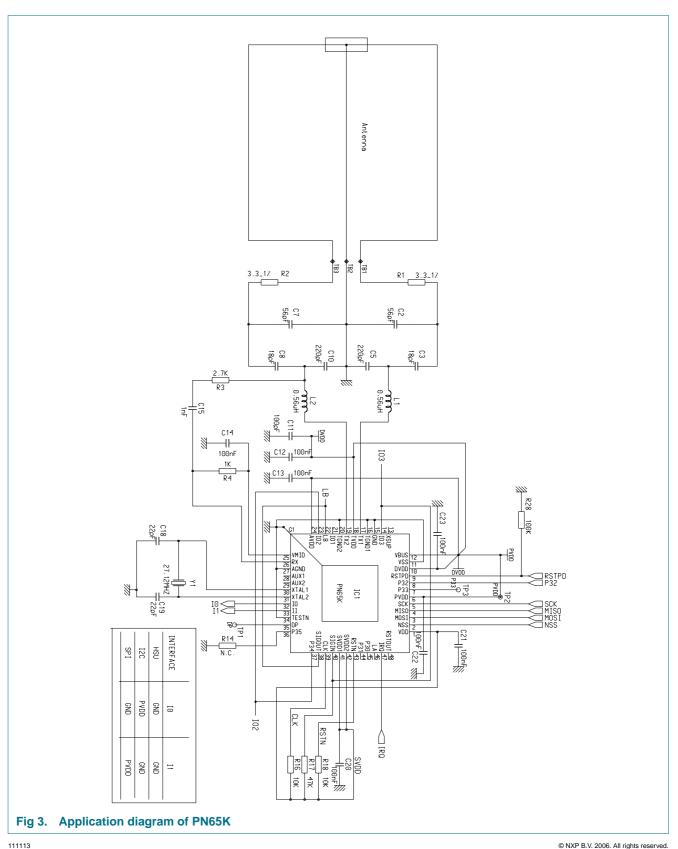

# **10.** Application information

**PN65K**

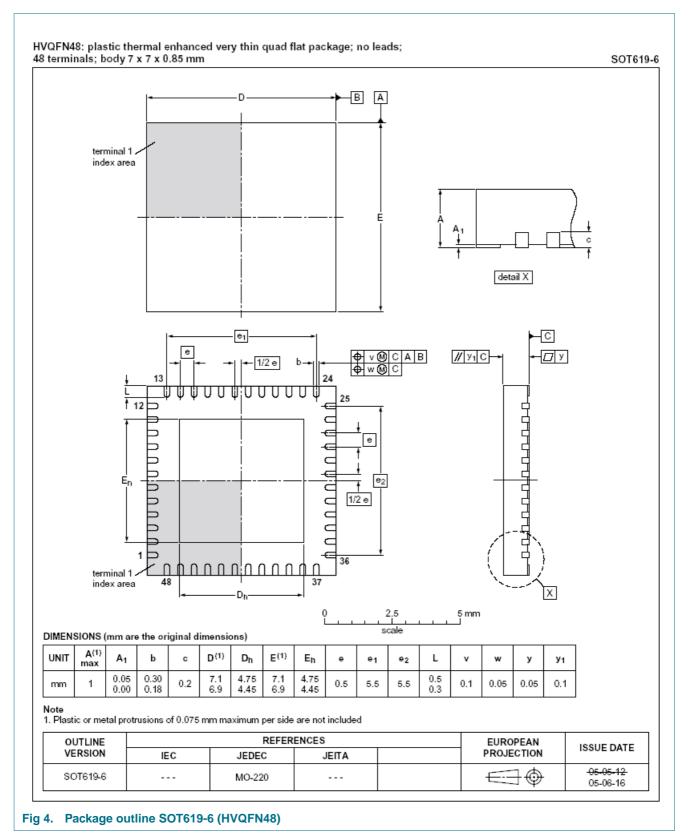

# 11. Package outline

### 12. References

For technical information see separate documents:

- "Data Sheet P5CN072, Secure Dual Interface PKI Smart Card Controller,

- "Data Sheet PN531\_C2, Near Field Communication Controller,

# 13. Revision history

| Table 6. Revision | history                                |                       |                                                            |              |

|-------------------|----------------------------------------|-----------------------|------------------------------------------------------------|--------------|

| Document ID       | Release date Dat                       | a sheet status        | Change notice                                              | Supersedes   |

| 111113            | 20 October 2006 Obj                    | ective short data she | et                                                         | Revision 1.2 |

| Modifications:    | guidelines of NXP                      | Semiconductors.       | redesigned to comply w                                     | ·            |

|                   | <ul> <li>Section 4 "Quick r</li> </ul> | eference data" on pa  | <u>ge 4</u> : added new Section<br>11: update of package d | 1            |

# 14. Legal information

### 14.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 14.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 14.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

### 14.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Mifare — is a trademark of NXP B.V. (replace by text inset t001tma<1nn>)

# **15. Contact information**

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: salesaddresses@nxp.com

### 16. Tables

| Table 1: | Quick reference data  |

|----------|-----------------------|

| Table 2: | Ordering information5 |

| Table 3: | Pin description6      |

| Table 4: | Limiting values9      |

|----------|-----------------------|

| Table 5: | Operating conditions9 |

| Table 6. | Revision history      |

# 17. Figures

| Fig 1. | Block diagram of PN65K5                  |  |

|--------|------------------------------------------|--|

| Fig 2. | Pin configuration for HVQFN 48 (SOT619)6 |  |

| Fig 3. | Application diagram of PN65K       | 10 |

|--------|------------------------------------|----|

| Fig 4. | Package outline SOT619-6 (HVQFN48) | 11 |

### **18. Contents**

| 1                                                                                                          | General description 1                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                        | Naming conventions 1                                                                                                                                                                                               |

| 2                                                                                                          | Features 2                                                                                                                                                                                                         |

| 2.1                                                                                                        | General                                                                                                                                                                                                            |

| 2.2                                                                                                        | NFC controller 2                                                                                                                                                                                                   |

| 2.3                                                                                                        | Secure smart card controller 3                                                                                                                                                                                     |

| 3                                                                                                          | Applications 4                                                                                                                                                                                                     |

| 4                                                                                                          | Quick reference data 4                                                                                                                                                                                             |

| 5                                                                                                          | Ordering information 5                                                                                                                                                                                             |

| 6                                                                                                          | Block diagram 5                                                                                                                                                                                                    |

| 7                                                                                                          | Pinning information                                                                                                                                                                                                |

| 7.1                                                                                                        | Pinning                                                                                                                                                                                                            |

| 7.2                                                                                                        | Pin description 6                                                                                                                                                                                                  |

| 8                                                                                                          | Limiting values                                                                                                                                                                                                    |

|                                                                                                            |                                                                                                                                                                                                                    |

| 9                                                                                                          | Recommended operating conditions                                                                                                                                                                                   |

| 9<br>10                                                                                                    | -                                                                                                                                                                                                                  |

| •                                                                                                          | Recommended operating conditions                                                                                                                                                                                   |

| 10                                                                                                         | Recommended operating conditions                                                                                                                                                                                   |

| 10<br>11                                                                                                   | Recommended operating conditions.9Application information.10Package outline11                                                                                                                                      |

| 10<br>11<br>12                                                                                             | Recommended operating conditions.9Application information.10Package outline11References12                                                                                                                          |

| 10<br>11<br>12<br>13                                                                                       | Recommended operating conditions.9Application information.10Package outline11References12Revision history.13                                                                                                       |

| 10<br>11<br>12<br>13<br>14                                                                                 | Recommended operating conditions.9Application information.10Package outline11References12Revision history.13Legal information.14                                                                                   |

| 10<br>11<br>12<br>13<br>14<br>14.1                                                                         | Recommended operating conditions.9Application information.10Package outline11References12Revision history13Legal information14Data sheet status14                                                                  |

| 10<br>11<br>12<br>13<br>14<br>14.1<br>14.2                                                                 | Recommended operating conditions.9Application information.10Package outline11References12Revision history13Legal information14Data sheet status14Definitions14                                                     |

| 10<br>11<br>12<br>13<br>14<br>14.1<br>14.2<br>14.3                                                         | Recommended operating conditions.9Application information.10Package outline11References12Revision history.13Legal information.14Data sheet status14Definitions.14Disclaimers.14                                    |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br><b>14</b><br>14.1<br>14.2<br>14.3<br>14.4              | Recommended operating conditions.9Application information.10Package outline11References12Revision history.13Legal information.14Data sheet status14Definitions.14Disclaimers.14Trademarks.14                       |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br><b>14</b><br>14.1<br>14.2<br>14.3<br>14.4<br><b>15</b> | Recommended operating conditions.9Application information.10Package outline11References12Revision history.13Legal information.14Data sheet status14Definitions.14Disclaimers.14Trademarks.14Contact information.14 |

#### © NXP B.V. 2006.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 20 October 2006 Document identifier: 111113