## microelectronics group

# FlashDSP®1650 Digital Signal Processor

### 1 Features

- For 5 V operation:

- 25 ns instruction cycle time (40 MIPS)

- For 3.3 V operation:

- 30 ns instruction cycle time (33 MIPS)

- Power-saving features:

- Low-power 0.6 μm CMOS technology; fully static design

- Active power: 9.5 mW/MIPS at 5.0 V

- 3.3 mW/MIPS at 3.3 V

- Low-power stopclk: 175 μW at 5.0 V

66 μW at 3.3 V

- 24 Kwords (maximum) internal flash ROM

- One bank of 1.25 Kwords or two banks of 1 Kword internal RAM

- 16 x 16-bit multiplication and 36-bit accumulation in one instruction cycle

- Two 36-bit accumulators

- Multichannel audio codec, capable of 4 ADC and 3 DAC operations per 16 kHz frame

- Instruction cache for high-speed, programefficient, zero-overhead looping

- One external vectored interrupt

- Two 64 Kword address spaces with software waitstates for external accesses

- Single-channel serial I/O port; 8-bit data channel

- Programmable phase-locked loop

- Microphone, speaker, and line driver interface circuits

- Four 8-bit and one 4-bit I/O ports for flexible status or control pins

- External memory interface, including DRAM

- Two interrupt timers and one watchdog timer

- 68-pin PLCC, 80-pin MQFP or 100-pin TQFP package

- High- and low-frequency clock options

- Synchronous serial interface unit

- Internal power-loss detection unit

- Object code upward compatible with DSP1600 Digital Signal Processor family

- Supported by DSP165X-ST support tools

- Full-speed in-circuit emulation HDS (HD-supported)

## 2 Description

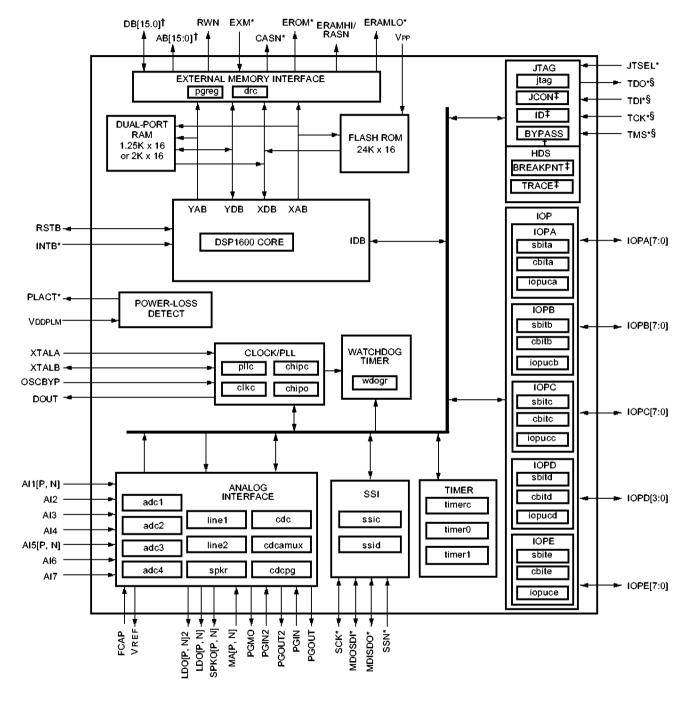

The FlashDSP1650 is a 16-bit, fixed-point digital signal processor (DSP) based on the DSP1600 core. It is programmable to perform a wide variety of fixedpoint signal processing functions. A member of the DSP165X family, the FlashDSP1650 includes a mix of peripherals specifically intended to support processing-intensive but cost-sensitive applications. In addition to the core, the FlashDSP1650 consists of the following peripheral blocks: external memory interface unit (EMI), synchronous serial interface unit (SSI), five I/O ports (IOPs), two timer units, a watchdog timer, an analog interface, and a JTAG interface; as well as one bank of 1.25 Kwords or two banks of 1 Kword of RAM. The FlashDSP1650 is part of a low-cost, high-performance solution for consumer product applications.

The *FlashDSP*1650 is available in the following packages:

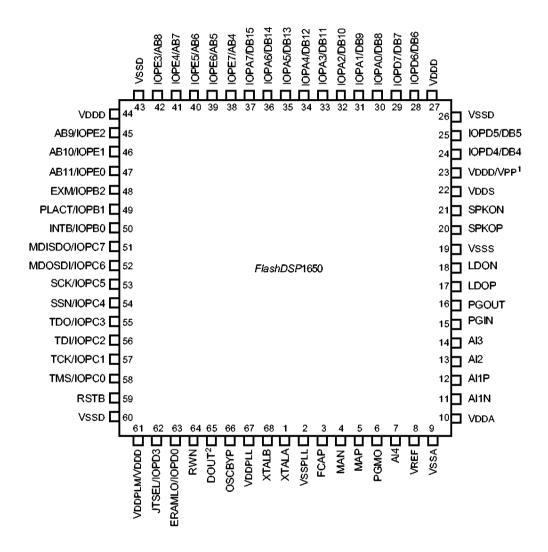

- 68-pin PLCC (See Figure 1 on page 13.)

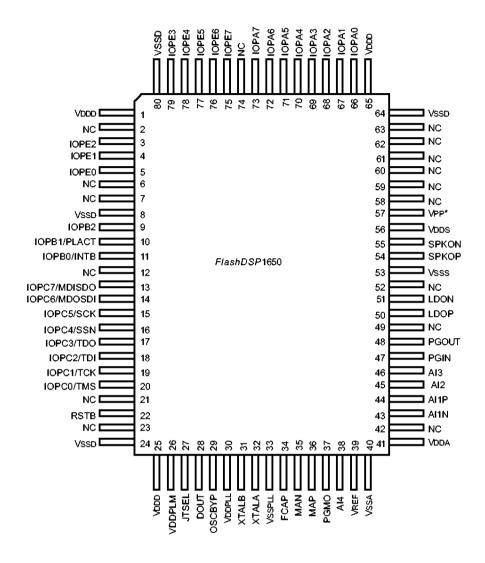

- 80-pin MQFP (See Figure 2 on page 14.)

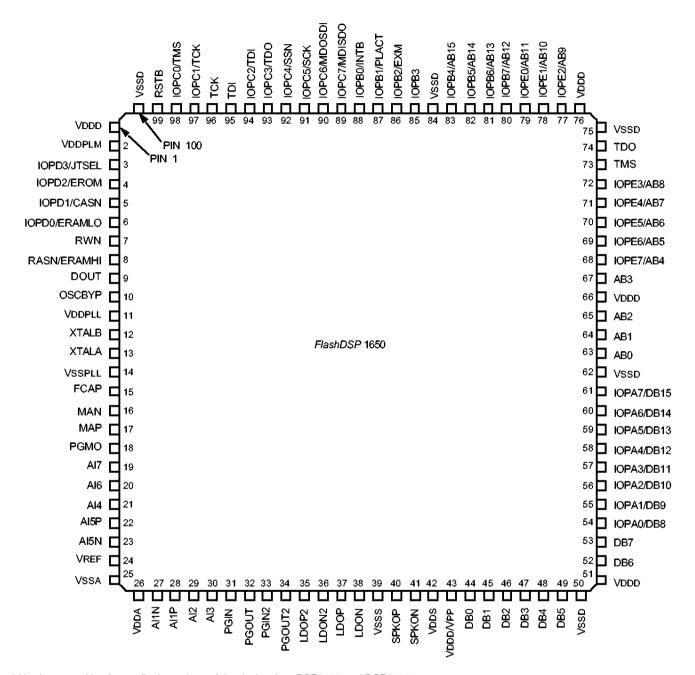

- 100-pin TQFP (See Figure 3 on page 15.)

The FlashDSP1650 achieves high throughput without programming restrictions or latencies due to its parallel pipelined architecture. The processor has an arithmetic unit capable of a 16 x 16-bit multiplication and 36-bit accumulation, or a 32-bit ALU operation in one instruction cycle. Data is accessed from memory through two independent addressing units.

A fully static, low-power, 0.6 μm CMOS design and a low-power standby mode support power-sensitive equipment applications. A single external crystal allows the use of a high-frequency and a low-frequency clock. Under program control, the *FlashDSP*1650 can be switched between the high-frequency and low-frequency clock options. When switched to the low-frequency clock, the power is reduced and can be further reduced using a stop-clock mode.

The FlashDSP1650 device is the development platform for the DSP1651/52 and DSP1653. To support full-speed in-circuit emulation, the FlashDSP1650 device includes an internal HDS module and an internal flash ROM for program store.

# **Table of Contents**

| Contents                                                                         | Page |

|----------------------------------------------------------------------------------|------|

| 1 Features                                                                       | 1    |

| 2 Description                                                                    |      |

| 2.1 Functional Differences Between the DSP1651 and the 80-Pin PLCC FlashDSP1650  |      |

| 2.2 Functional Differences Between the DSP1653 and the 100-Pin TQFP FlashDSP1650 |      |

| 2.3 Functional Differences Between the DSP1654 and the 100-Pin TQFP FlashDSP1650 |      |

| 2.4 Functional Differences Between the DSP1655 and the FlashDSP1650              |      |

| 3 Pin Information                                                                |      |

| 3.1 System Interface                                                             |      |

| 3.1.1 XTALA, XTALB                                                               |      |

| 3.1.2 RSTB                                                                       |      |

| 3.1.3 INTB                                                                       |      |

| 3.1.4 DOUT                                                                       |      |

| 3.1.5 PLACT                                                                      |      |

| 3.1.6 VDDPLM                                                                     |      |

| 3.2 External Memory Interface                                                    |      |

| 3.2.1 AB[15:0]                                                                   |      |

| 3.2.2 DB[15:0]                                                                   |      |

| 3.2.3 ERAMLO                                                                     |      |

| 3.2.4 ERAMHI/RASN                                                                |      |

| 3.2.5 CASN                                                                       |      |

| 3.2.6 RWN                                                                        |      |

| 3.2.7 EXM                                                                        |      |

| 3.2.8 EROM                                                                       |      |

| 3.3 Synchronous Serial Interface (SSI)                                           |      |

| 3.3.1 SCK                                                                        |      |

| 3.3.2 MDOSDI                                                                     |      |

| 3.3.3 MDISDO                                                                     |      |

| 3.3.4 SSN                                                                        |      |

| 3.4 I/O Port Interface (IOP)                                                     |      |

| 3.4.1 IOPA[7:0]                                                                  |      |

| 3.4.2 IOPB[7:0]                                                                  |      |

| 3.4.3 IOPC[7:0]                                                                  |      |

| 3.4.4 IOPD[3:0]                                                                  |      |

| 3.4.5 IOPE[7:0]                                                                  |      |

| 3.5.1 TCK                                                                        |      |

| 3.5.2 TMS                                                                        |      |

| 3.5.3 TDI                                                                        |      |

| 3.5.4 TDO                                                                        |      |

| 3.5.5 JTSEL                                                                      |      |

| 3.6 Line Drivers                                                                 |      |

| 3.6.1 LDOP, LDON                                                                 |      |

| 3.6.2 LDOP2, LDON2                                                               |      |

| 3.7 Microphone Amplifier and Power Supply                                        |      |

| 3.7.1 FCAP                                                                       |      |

| 3.7.2 PGMO                                                                       |      |

| 3.7.3 MAP                                                                        |      |

| 3.7.4 MAN                                                                        |      |

| 3.8 Speaker Amplifier                                                            |      |

| 3.8.1 SPKON, SPKOP                                                               |      |

| 3.9 Programmable Gain Amplifiers                                                 |      |

| 3.9.1 PGOUT                                                                      |      |

|                                                                                  |      |

| Contents                                           | Page |

|----------------------------------------------------|------|

| 3.9.2 PGOUT2                                       | 24   |

| 3.9.3 PGIN                                         |      |

| 3.9.4 PGIN2                                        |      |

| 3.10 Analog Utility                                |      |

| 3.10.1 VREF                                        |      |

| 3.11 PWR/GND                                       |      |

| 3.11.1 VDDA                                        |      |

| 3.11.2 VSSA                                        |      |

| 3.11.3 VSSD                                        |      |

| 3.11.4 VDDD                                        |      |

| 3.11.5 VDDPLL                                      |      |

| 3.11.6 VSSPLL                                      |      |

| 3.11.7 VDDS                                        |      |

| 3.11.8 Vsss                                        |      |

| 3.11.9 VPP                                         |      |

| 4 Hardware Architecture                            |      |

| 4.1 FlashDSP1650 Architectural Overview            |      |

| 4.1.1 DSP1600 Core                                 |      |

| 4.1.2 Dual-Port RAM (DPRAM)                        |      |

| 4.1.3 Read-Only Memory (ROM)                       |      |

| 4.1.4 External Memory Interface (EMI)              |      |

| 4.1.5 Timers                                       |      |

| 4.1.6 Watchdog Timer                               |      |

| 4.1.7 Analog Interface                             |      |

| 4.1.8 Input/Output Ports (IOP)                     |      |

| 4.1.9 JTAG                                         |      |

| 4.1.10 Synchronous Serial Interface Units (SSI)    |      |

| 4.1.11 Clock Generation                            |      |

| 4.1.12 Power-Loss Detect Circuit                   |      |

| 4.2 DSP1600 Core Architectural Overview            |      |

| 4.2.1 System Cache and Control Section (SYS)       |      |

| 4.2.2 Data Arithmetic Unit (DAU)                   |      |

| 4.2.3 Y Space Address Arithmetic Unit (YAAU)       |      |

| 4.2.4 X Space Address Arithmetic Unit (XAAU)       |      |

| 4.3 Interrupts, Trap, and Low-Power Standby Mode   |      |

| 4.3.1 Interruptibility                             |      |

| 4.3.2 Vectored Interrupts                          |      |

| 4.3.3 External Interrupt Pin (INTB)                |      |

| 4.3.4 Clearing Interrupts                          |      |

| 4.3.5 Power-Saving Modes                           |      |

| 4.4 Memory Maps and Wait-States                    |      |

| 4.4.1 Instruction/Coefficient Memory Map Selection |      |

| 4.4.2 Boot from External ROM                       |      |

| 4.4.3 Data Memory Map Selection                    |      |

| 4.5 Clock Generation                               |      |

| 4.5.1 Functional Overview                          |      |

| 4.5.2 Core Clock Switching                         |      |

| 4.6 External Memory Interface (EMI)                |      |

| · · · · · · · · · · · · · · · · · · ·              |      |

| 4.6.1 Memory Segment Enables                       |      |

| 4.6.3 Pin Multiplexing Control                     |      |

| 4.7 Synchronous Serial Interface (SSI)             |      |

| T. Paymonious Senai interiace (SSI)                | 43   |

| Contents                                                                 | Page |

|--------------------------------------------------------------------------|------|

| 4.7.1 SSI Operation                                                      | 44   |

| 4.8 I/O Ports (IOP)                                                      | 45   |

| 4.8.1 IOP Operation                                                      | 45   |

| 4.8.2 IOPA Interrupt Circuitry                                           | 45   |

| 4.8.3 IOPD Interrupt Circuitry                                           |      |

| 4.8.4 Pin Multiplexing Control                                           | 46   |

| 4.9 Timers                                                               | 47   |

| 4.10 Watchdog Timer                                                      | 47   |

| 4.11 Analog Interface                                                    |      |

| 5 Software Architecture                                                  | 49   |

| 5.1 Instruction Set                                                      |      |

| 5.1.1 F1 Multiply/ALU Instructions                                       | 49   |

| 5.1.2 F2 Special Function Instructions                                   |      |

| 5.1.3 Control Instructions                                               |      |

| 5.1.4 Conditional Mnemonics (Flags)                                      |      |

| 5.1.5 F3 ALU Instructions                                                | 54   |

| 5.1.6 Cache Instructions                                                 |      |

| 5.1.7 Data Move Instructions                                             |      |

| 5.2 Register Settings                                                    |      |

| 5.3 Reset States                                                         |      |

| 5.4 Instruction Set Formats                                              |      |

| 5.4.1 Multiply/ALU Instructions                                          |      |

| 5.4.2 Special Function Instructions                                      |      |

| 5.4.3 Control Instructions                                               |      |

| 5.4.4 Data Move Instructions                                             |      |

| 5.4.5 Cache Instructions                                                 |      |

| 5.4.6 Field Descriptions                                                 |      |

| 6 Device Requirements and Characteristics                                |      |

| 6.1 Absolute Maximum Ratings                                             |      |

| 6.2 Handling Precautions                                                 |      |

| 6.3 Recommended Operating Conditions                                     | 80   |

| 6.4 Decoupling Requirements                                              |      |

| 6.5 Package Thermal Considerations                                       |      |

| 7 Electrical Requirements and Characteristics                            |      |

| 7.1 Typical Power Dissipation                                            |      |

| 7.2 Input and I/O Buffer Power Dissipation                               |      |

| 7.3 Analog Interface                                                     |      |

| 7.3.1 A-to-D and D-to-A Converter                                        |      |

| 7.3.2 A-to-D Inputs                                                      |      |

| 7.3.3 Speaker Driver                                                     |      |

| 7.3.4 Line Driver                                                        |      |

| 7.3.5 Programmable Gain Amplifiers                                       |      |

| 7.3.6 Microphone Power Supply and Amplifier                              |      |

| 7.3.7 Reference Designs                                                  |      |

| 7.3.8 System Characteristics                                             |      |

| 8 Timing Requirements and Characteristics                                |      |

| 8.1 Input Clock Options                                                  |      |

| 8.2 DSP Clock Generation 8.3 Powerup Reset (Assuming VDDPLM Is Disabled) |      |

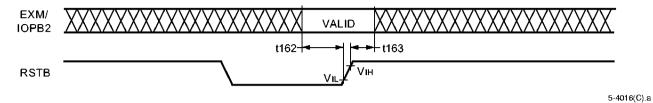

| 8.4 Reset Synchronization                                                | 100  |

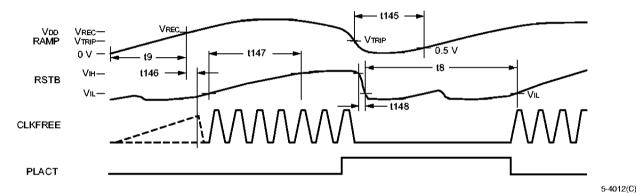

| 8.5 Powerup and Power-Loss Detect Circuit Reset                          |      |

| 8.5.1 Powerup Reset Specifications (VDDPLM Connected to VDD)             |      |

| J.S. F. Official Flood, oppositional (FDD) Lin Colliforiou to FDD /      |      |

| Contents                                                                    | Page |

|-----------------------------------------------------------------------------|------|

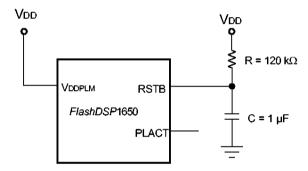

| 8.5.2 Power-Loss Detect Specifications (VDDPLM Connected to a Separate VDD) | 108  |

| 8.5.3 PLACT Pin Specifications                                              | 110  |

| 8.6 JTAG I/O Specifications                                                 | 111  |

| 8.7 Interrupt                                                               |      |

| 8.8 Input/Output Ports (IOP)                                                | 113  |

| 8.9 External Memory Interface                                               | 114  |

| 8.10 External DRAM Interface                                                | 120  |

| 8.11 Synchronous Serial Interface (SSI) Specifications                      | 125  |

| 9 Crystal Oscillator Electrical Requirements and Characteristics            | 128  |

| 9.1 Crystal Oscillator                                                      | 128  |

| 9.1.1 Crystal Oscillator Power Dissipation                                  | 128  |

| 9.1.2 Crystal Oscillator External Components                                | 128  |

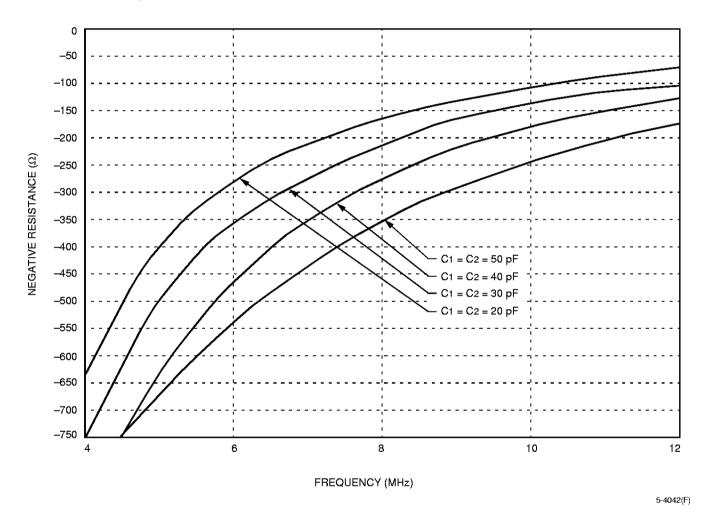

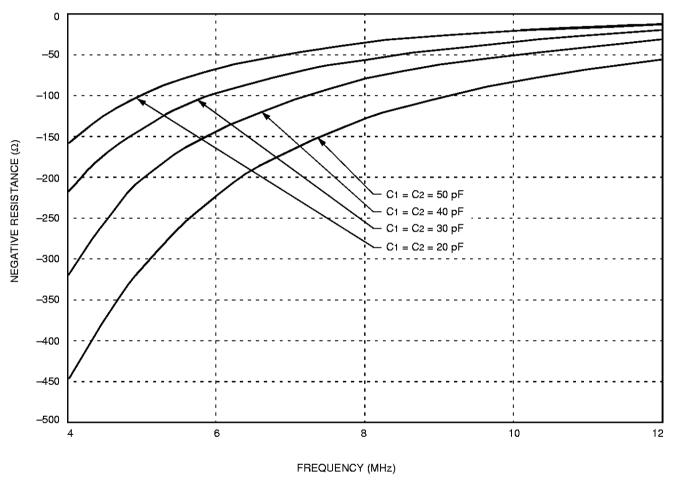

| 9.1.3 Crystal Oscillator Negative Resistance Curves                         | 129  |

| 9.2 Frequency Accuracy Considerations                                       | 131  |

| 10 Outline Diagrams                                                         | 134  |

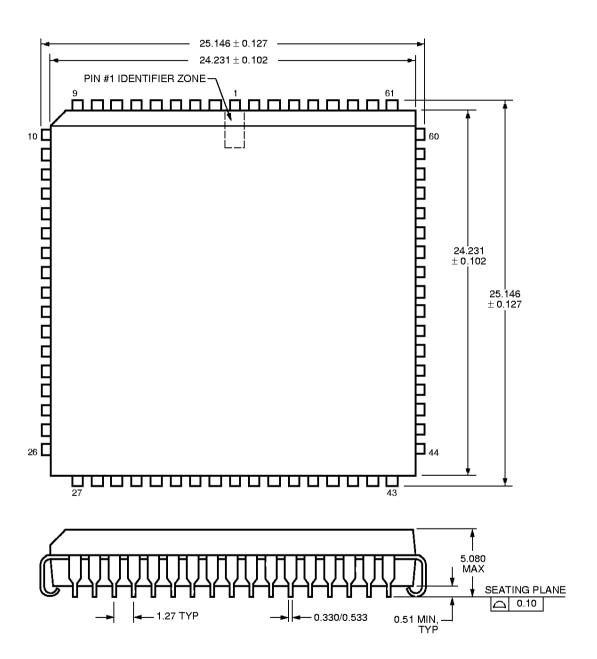

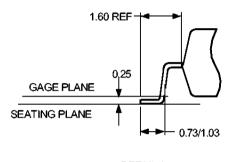

| 10.1 68-Pin PLCC Outline Diagram                                            | 134  |

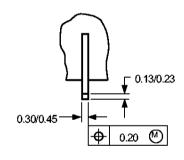

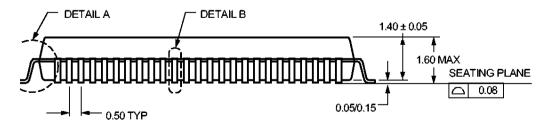

| 10.2 80-Pin MQFP Outline Diagram                                            | 135  |

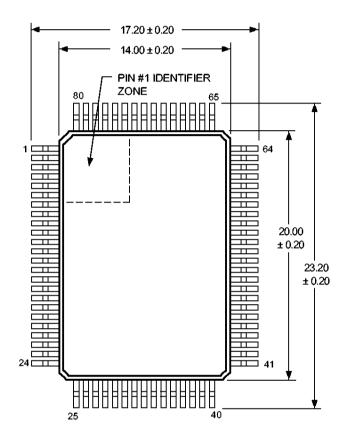

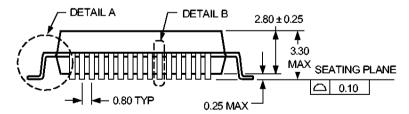

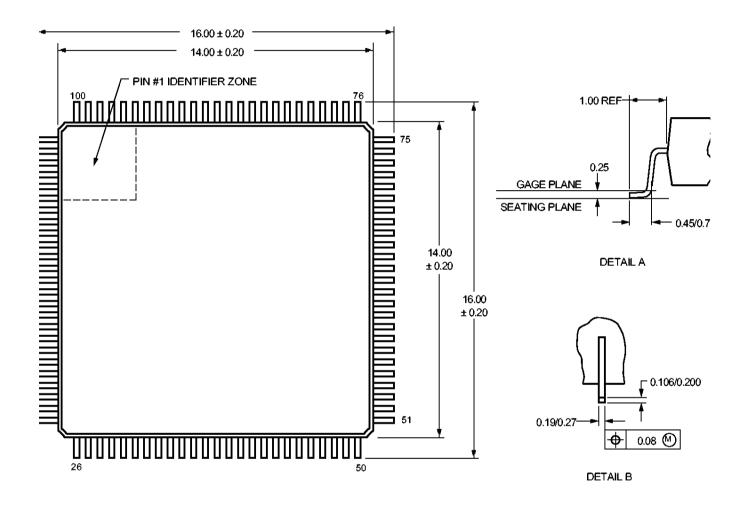

| 10.3 100-Pin TQFP Thin Quad Flat Pack                                       | 136  |

| 11 Ordering Information                                                     | 137  |

| 11.1 Device Coding                                                          | 137  |

| 11.2 Mask-Programmable Options                                              | 137  |

| Figures                                                                                                                    | Page |

|----------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1. FlashDSP1650 68-Pin PLCC Pin Diagram                                                                             | 13   |

| Figure 2. FlashDSP1650 80-Pin MQFP Pin Diagram                                                                             |      |

| Figure 3. FlashDSP1650 100-Pin TQFP Pin Diagram                                                                            |      |

| Figure 4. FlashDSP1650 Pinout by Group                                                                                     | 16   |

| Figure 5. FlashDSP1650 Block Diagram                                                                                       | 26   |

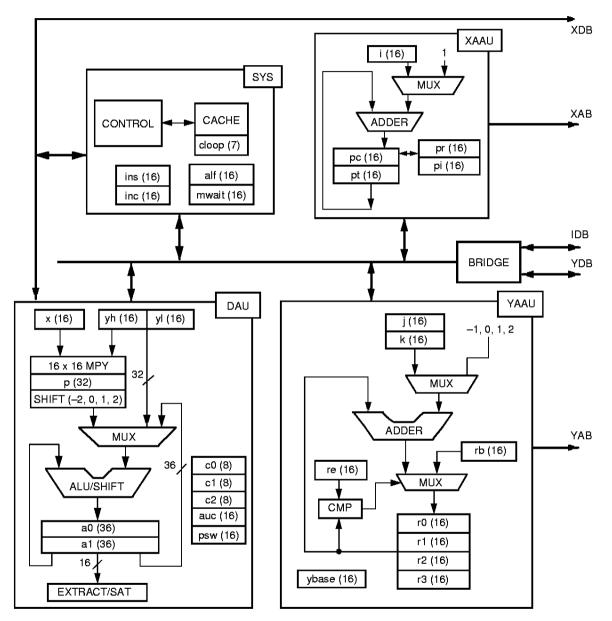

| Figure 6. DSP1600 Core Block Diagram                                                                                       | 31   |

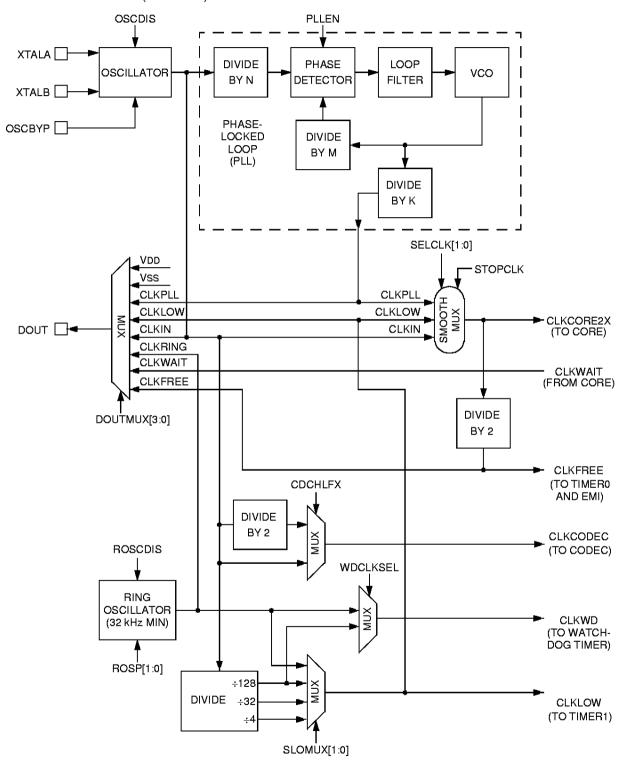

| Figure 7. Clock Generation Overview                                                                                        | 40   |

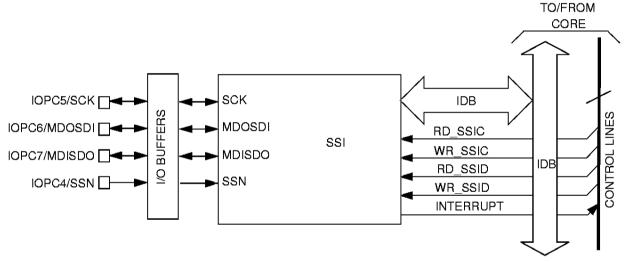

| Figure 8. SSI Interconnections                                                                                             | 43   |

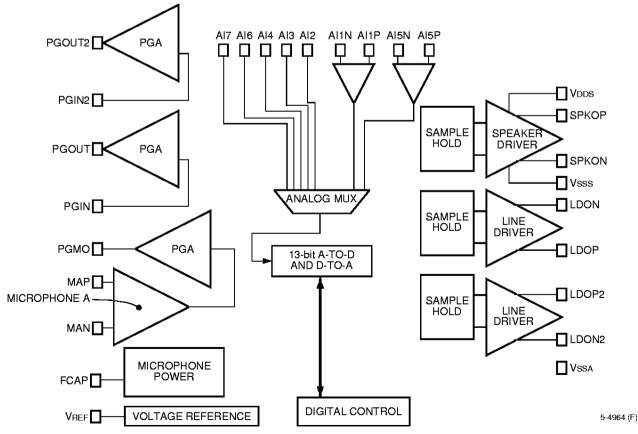

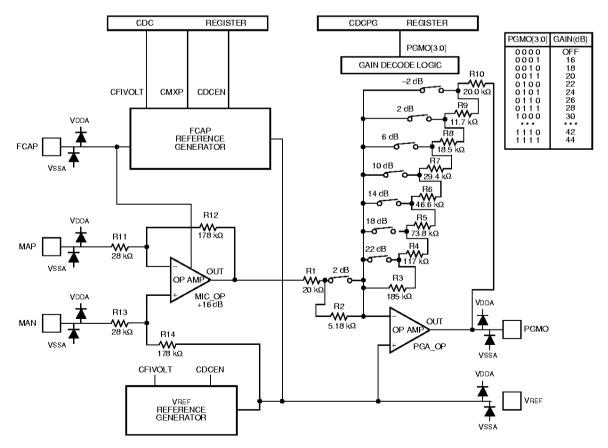

| Figure 9. Block Diagram of Analog Circuitry                                                                                |      |

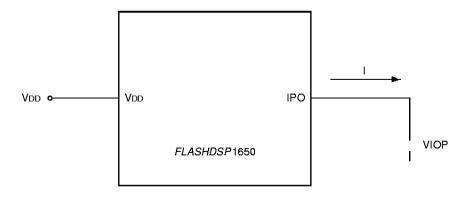

| Figure 10. Pull-Up and Pull-Down Measurements                                                                              |      |

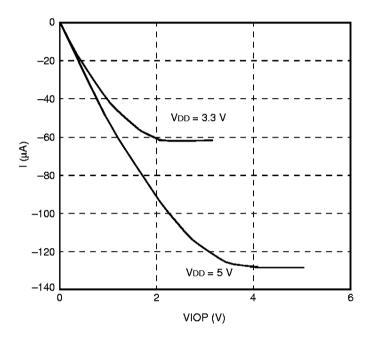

| Figure 11. Pull-Down Characteristics of an I/O Port                                                                        |      |

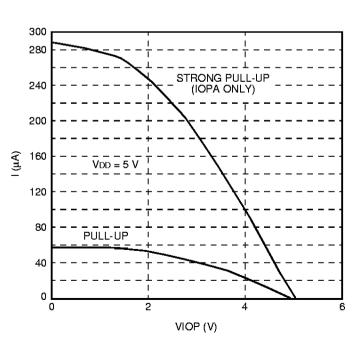

| Figure 12. Pull-Up Characteristics of an I/O Port at VDD = 5 V                                                             |      |

| Figure 13. Pull-Up Characteristics of an I/O Port at VDD = 3.3 V                                                           |      |

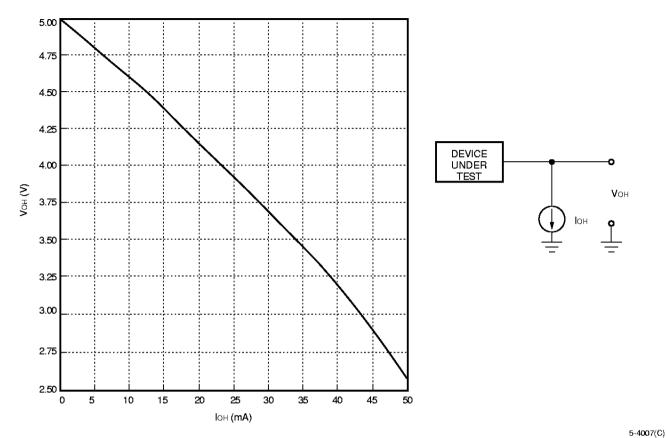

| Figure 14. Plot of Voн vs. Ioн Under Typical Operating Conditions                                                          |      |

| Figure 15. Plot of Vo∟ vs. lo∟ Under Typical Operating Conditions                                                          |      |

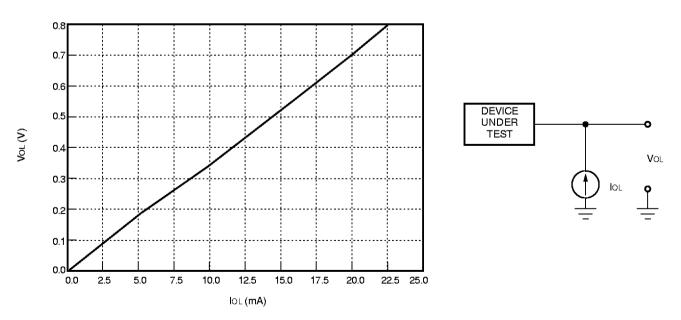

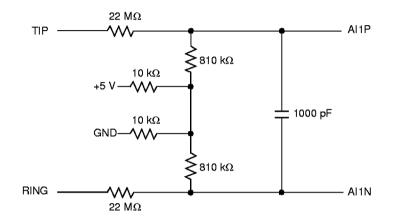

| Figure 16. Antialias Filter from PGMO                                                                                      |      |

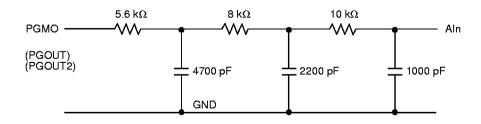

| Figure 17. ADC Functional Block Diagram                                                                                    |      |

| Figure 18. Overload Compression (5 V Supply)                                                                               |      |

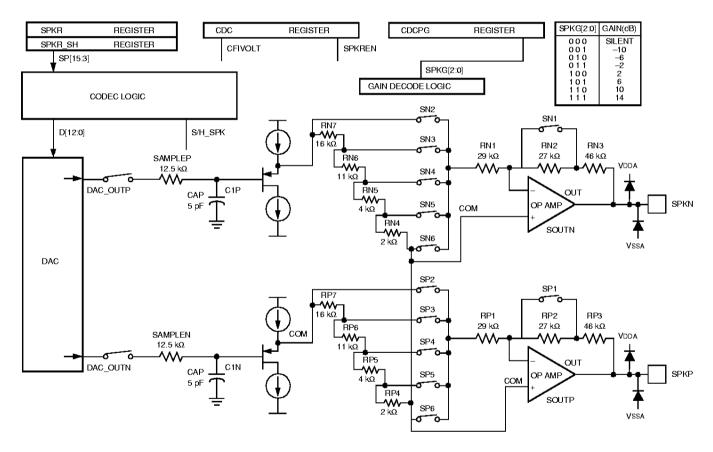

| Figure 19. Speaker Driver Functional Block Diagram                                                                         |      |

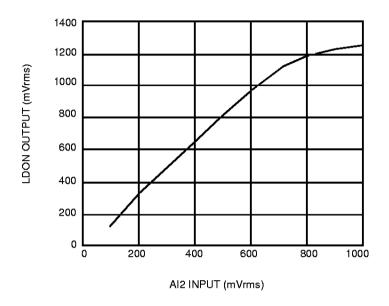

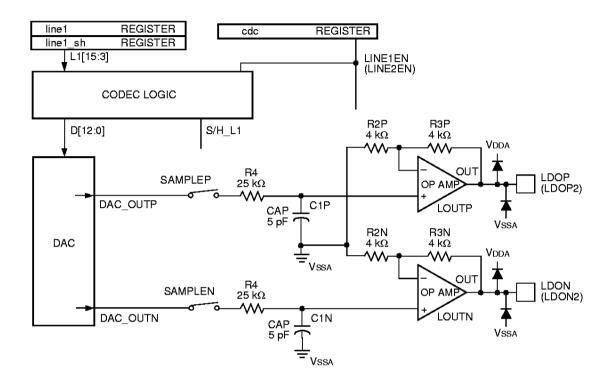

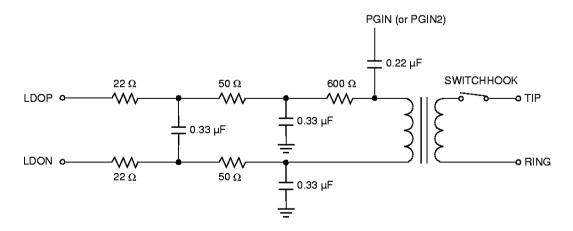

| Figure 20. Line Drivers Functional Block Diagram                                                                           |      |

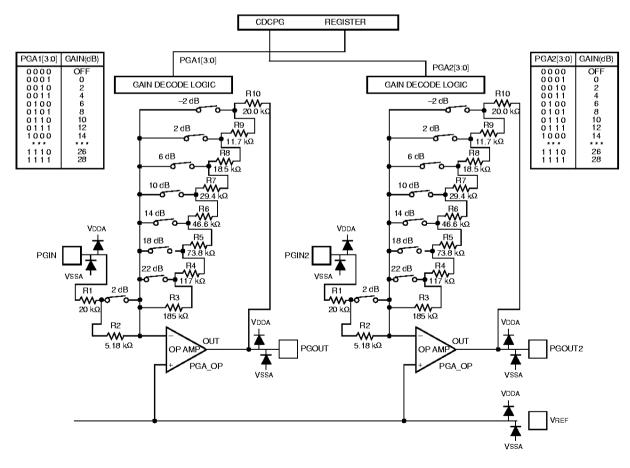

| Figure 21. Programmable Gain Amplifiers Functional Block Diagram                                                           |      |

| Figure 22. Microphone Power Supply and Amplifier Functional Block Diagram                                                  |      |

| Figure 23. Ring Detection/Parallel Set Detection                                                                           |      |

| Figure 24. Line Interface/Smoothing Filter                                                                                 |      |

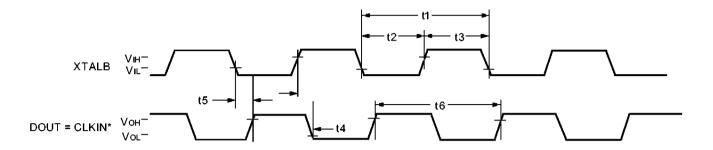

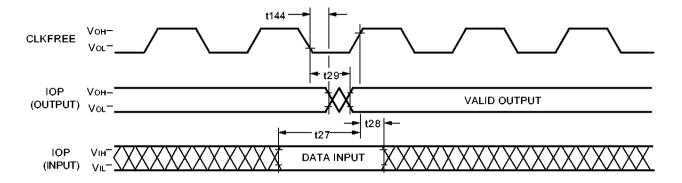

| Figure 25. I/O Clock Timing Diagram                                                                                        |      |

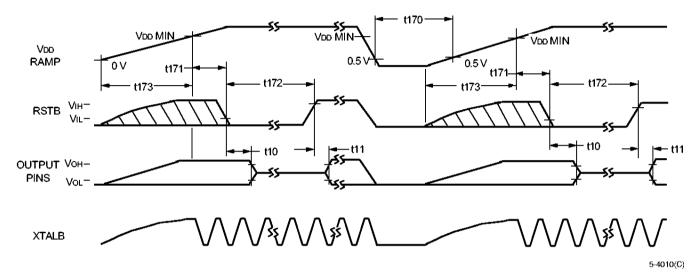

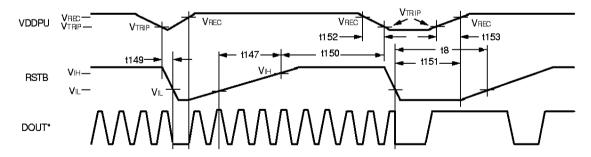

| Figure 26. Powerup Reset and Device Reset Timing Diagram                                                                   |      |

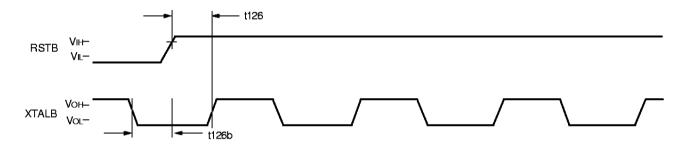

| Figure 27. Reset Synchronization Timing                                                                                    |      |

| Figure 28. Powerup Reset                                                                                                   |      |

| Figure 29. Example of Power-Loss Detect External Component Configuration                                                   |      |

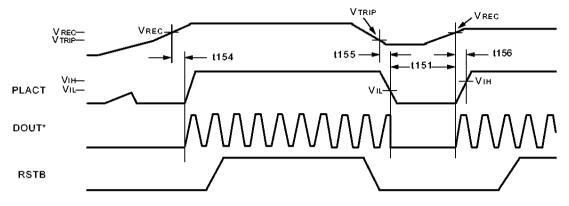

| Figure 30. Power-Loss Detect Reset                                                                                         |      |

| Figure 31. PLACT Functionality with VDDPLM Enabled and PLCKOFF bit Set in chipo negister<br>Figure 32. JTAG Timing Diagram |      |

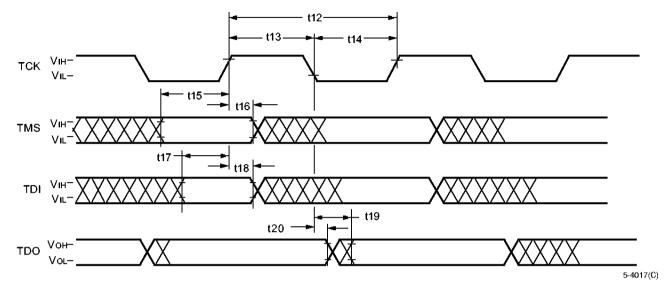

|                                                                                                                            |      |

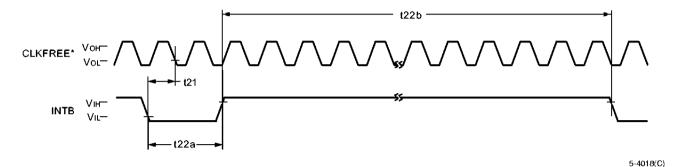

| Figure 33. Interrupt Timing Diagram                                                                                        |      |

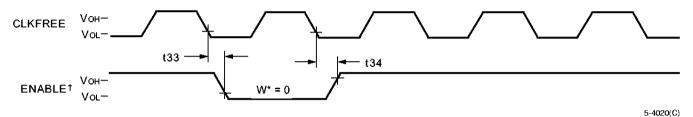

| Figure 35. Enable Transition Timing                                                                                        |      |

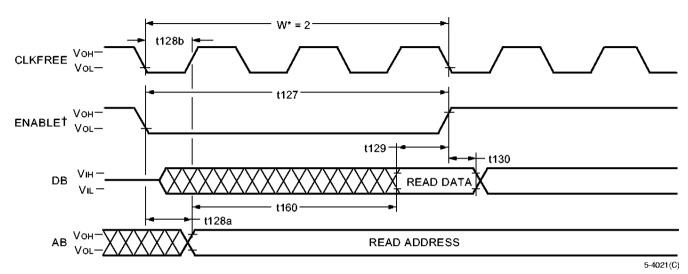

| Figure 36. External Memory Data Read Timing Diagram                                                                        |      |

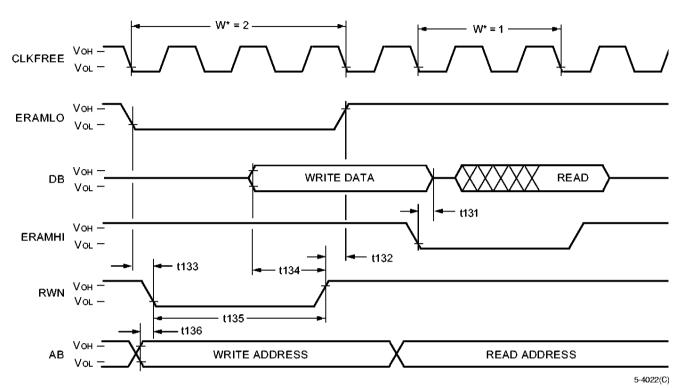

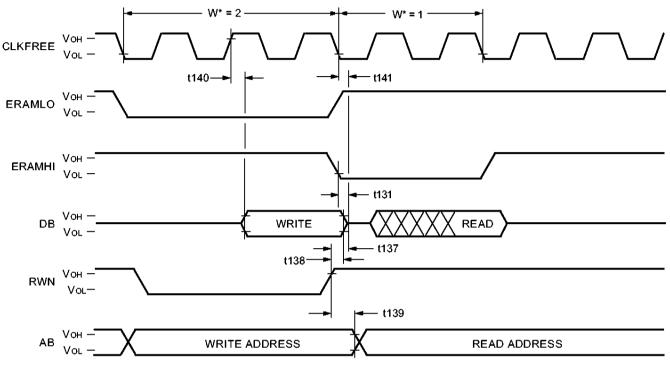

| Figure 37. External Memory Data Write, Read Timing Diagram                                                                 |      |

| Figure 38. Write Cycle Followed by Read Cycle                                                                              |      |

| Figure 39. EXM Timing Diagram                                                                                              |      |

| Figure 40. Read Cycle Timing (Relative) Diagram                                                                            |      |

| Figure 41. Early Write Cycle Timing (Relative) Diagram                                                                     |      |

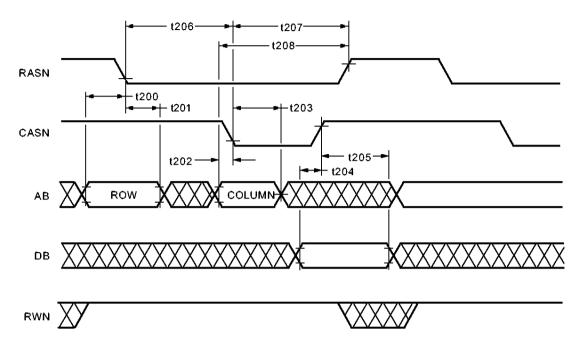

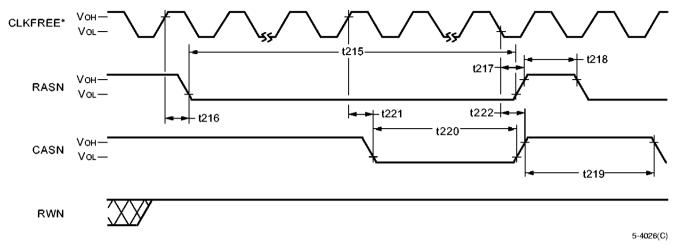

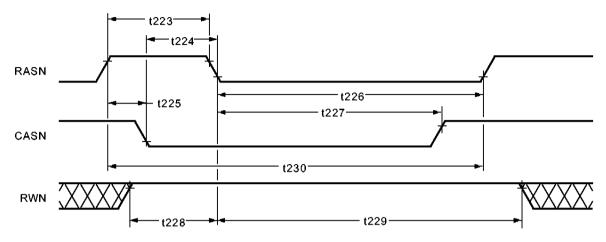

| Figure 42. Synchronous Delay DRAM Interface Timing Diagram                                                                 |      |

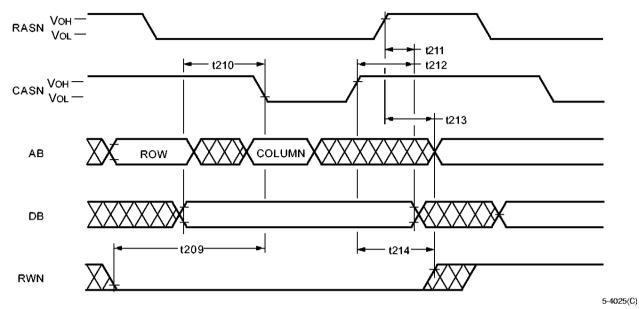

| Figure 43. CASN Before RASN Refresh Cycle Timing Diagram                                                                   |      |

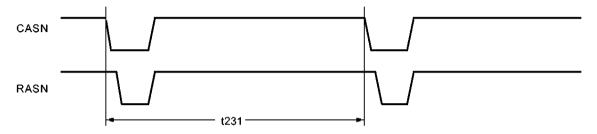

| Figure 44. Refresh Interval Timing with High-Speed Clocking                                                                |      |

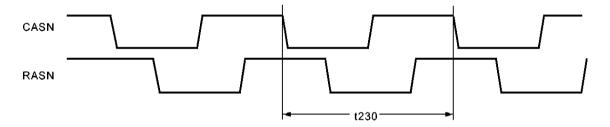

| Figure 45. Refresh Interval Timing with CLKLOW Clocking DSP Core                                                           |      |

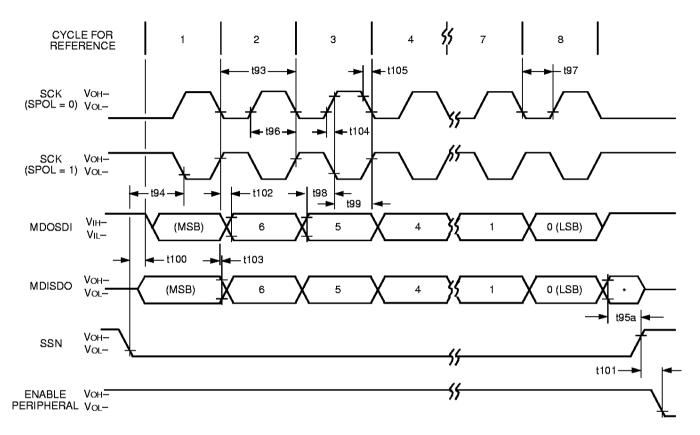

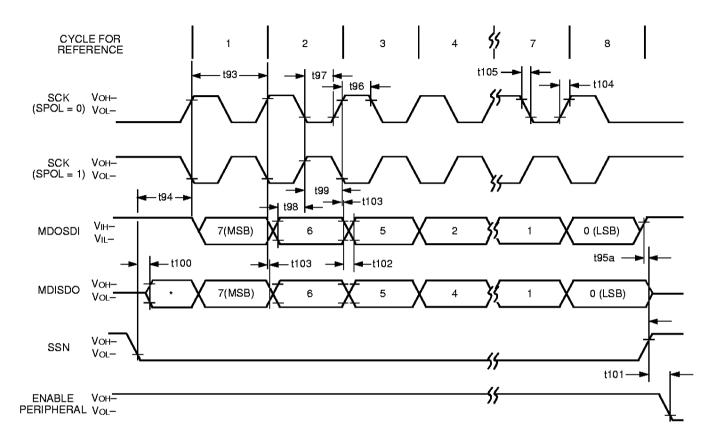

| Figure 46. SSI Transfer Timing (SPHA = 0)                                                                                  |      |

| Figure 47. SSI Transfer Timing (SPHA = 1)                                                                                  |      |

| Figure 48. Fundamental Crystal Configuration.                                                                              |      |

| Figure 49. 5 V Crystal Oscillator Negative Resistance Curves                                                               |      |

| Figure 50. 3.3 V Crystal Oscillator Negative Resistance Curves                                                             |      |

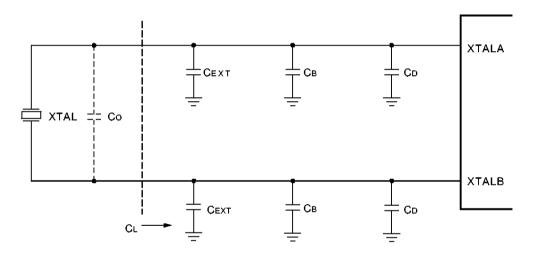

| Figure 51. Components of Load Capacitance for Crystal Oscillator                                                           |      |

| Tables                                                                                      | Page |

|---------------------------------------------------------------------------------------------|------|

| Table 1. Functional Differences Between the DSP1651 and the 80-Pin PLCC FlashDSP1650        | 10   |

| Table 2. Functional Differences Between the DSP1653 and the 100-Pin TQFP FlashDSP1650       | 11   |

| Table 3. Functional Differences Between the DSP1654 and the 100-Pin TQFP FlashDSP1650       | 11   |

| Table 4. Functional Differences Between the DSP1655 and the FlashDSP1650                    |      |

| Table 5. FlashDSP1650 Pinout                                                                |      |

| Table 6. FlashDSP1650 Power Supply, Ground, and Unconnected Pins                            |      |

| Table 7. FlashDSP1650 Block Diagram Legend                                                  |      |

| Table 8. DOUT Pin Output Functions                                                          |      |

| Table 9. DSP1600 Core Block Diagram Legend                                                  |      |

| Table 10. Interrupt Vectors                                                                 |      |

| Table 11. Instruction/Coefficient Memory Map (X Memory Space) for FlashDSP1650 (IR2KEN = 0) | 36   |

| Table 12. Instruction/Coefficient Memory Map (X Memory Space) for FlashDSP1650 (IR2KEN = 1) |      |

| Table 13. FlashDSP1650 Data Memory Map (IR2KEN = 0)                                         |      |

| Table 14. FlashDSP1650 Data Memory Map (IR2KEN = 1)                                         |      |

| Table 15. Clock Options                                                                     |      |

| Table 16. Clock Switch Latencies                                                            |      |

| Table 17. Core Clock Stabilization Requirements                                             | 41   |

| Table 18. SSI Pin Descriptions                                                              |      |

| Table 19. IOP Operation's                                                                   |      |

| Table 20. IOP Pin Multiplexing                                                              |      |

| Table 21. Analog Interface Registers                                                        |      |

| Table 22. Instruction Set Operators                                                         |      |

| Table 23. F1 Multiply/ALU Instructions                                                      |      |

| Table 24. Replacement Table for F1 Multiply/ALU Instructions                                |      |

| Table 25. F2 Special Function Instructions                                                  |      |

| Table 26. Replacement Table for F2 Special Function Instructions                            |      |

| Table 27. Control Instructions.                                                             |      |

| Table 28. Replacement Table for Control Instructions                                        |      |

| Table 29. FlashDSP1650 Conditional Mnemonics                                                |      |

| Table 30. F3 ALU Instructions                                                               |      |

| Table 31. Replacement Table for F3 ALU Instructions                                         |      |

| Table 32. Cache Instructions                                                                |      |

| Table 33. Replacement Table for Cache Instructions                                          |      |

| Table 34. Data Move Instructions                                                            |      |

| Table 35. Replacement Table for Data Move Instructions                                      |      |

| Table 36. alf (Standby and Memory Map) Register                                             |      |

| Table 37. auc (Arithmetic Unit Control) Register                                            | 57   |

| Table 38. cbit <a-e> (IOP Control Bit) and sbit<a-e> (IOP Status Bit) Registers</a-e></a-e> |      |

| Table 39. drc (DRAM Control) Register                                                       |      |

| Table 40. inc (Interrupt Control) Register                                                  |      |

| Table 41. ins (Interrupt Status) Register                                                   |      |

| Table 42. pllc Register Fields                                                              |      |

| Table 43. chipc Register Fields                                                             |      |

| Table 44. clkc Register Fields                                                              |      |

| Table 45. chipo Register Fields                                                             |      |

| Table 46. JTAG ID Register (32-bit)                                                         |      |

| Table 47. JTAG ROMCODE Letter Values                                                        |      |

| Table 48. mwait (External Memory Wait-States Control) Register                              |      |

| Table 49. pgreg (Page Address) Register                                                     |      |

| Table 50. psw (Processor Status Word) Register                                              |      |

| Table 51. sbit <a—e> (IOP Status Bit) and cbit<a—e> (IOP Control Bit) Registers</a—e></a—e> |      |

| Table 52. IOPUC <a—e> Register Fields</a—e>                                                 |      |

| Tables                                                                              | Page |

|-------------------------------------------------------------------------------------|------|

| Table 53. SSI Control Register (SSIC) Fields                                        | 66   |

| Table 54. SSI Data Register (SSID) Fields                                           |      |

| Table 55. timerc (Timer Control) Register (TIMER0 and TIMER1)                       |      |

| Table 56. cdc Register Fields                                                       |      |

| Table 57. cdcpg Register Fields                                                     | 69   |

| Table 58. cdcamux Register (Codec Analog MUX) Fields                                |      |

| Table 59. adc1, adc2, adc3 Register Fields                                          |      |

| Table 60. adc4 Register Fields                                                      |      |

| Table 61. spkr, line1, and line2 Register Fields                                    | 71   |

| Table 62. Register States After Reset                                               |      |

| Table 63. Format 1: Multiply/ALU Read/Write Group                                   | 73   |

| Table 64. Format 1a: Multiply ALU Read/Write Group                                  |      |

| Table 65. Format 2: Multiply/ALU Read/Write Group                                   |      |

| Table 66. Format 2a: Multiply/ALU Read/Write Group                                  |      |

| Table 67. Format 3: F2 ALU Special Functions                                        |      |

| Table 68. Format 3a: F3 ALU Operations                                              |      |

| Table 69. Format 4: Branch Direct Group                                             |      |

| Table 70. Format 5: Branch Indirect Group                                           |      |

| Table 71. Format 6: Conditional Branch Qualifier                                    |      |

| Table 72. Format 7: Data Move Group.                                                |      |

| Table 73. Format 8: Data Move (16-Bit Immediate Operand—2 Words)                    |      |

| Table 74. Format 9: Short Immediate Group                                           |      |

| Table 75. Format 9a: Direct Addressing                                              |      |

| Table 76. Format 10: Do/Redo                                                        |      |

| Table 77. T Field                                                                   |      |

| Table 78. aT Field                                                                  |      |

| Table 78. B Field                                                                   |      |

| Table 80. CON Field                                                                 |      |

| Table 81. D Field                                                                   |      |

| Table 82. DR Field                                                                  |      |

| Table 93. F1 Field                                                                  |      |

| Table 84. F2 Field                                                                  |      |

| Table 85. F3 Field                                                                  |      |

| Table 86. I Field                                                                   |      |

| Table 87. R Field                                                                   |      |

|                                                                                     |      |

| Table 88. S Field                                                                   |      |

| Table 90. SRC2 Field                                                                |      |

| Table 91. X Field                                                                   |      |

|                                                                                     |      |

| Table 92. Y Field                                                                   |      |

| Table 93. Z Field                                                                   |      |

| Table 94. Maximum Package Rating Parameters and Values                              |      |

| Table 95. Recommended Voltage and Temperature                                       |      |

| Table 96. Electrical Requirements                                                   |      |

| Table 97. Electrical Characteristics                                                |      |

| Table 98. PLL Electrical Specifications, VCO Frequency Ranges                       |      |

| Table 99. PLL Electrical Specifications and Register Settings                       |      |

| Table 100. Internal Module Power Dissipation                                        |      |

| Table 101. Input Buffer Maximum Power Dissipation                                   |      |

| Table 102. Schmitt Trigger Input Buffer Maximum Power Dissipation                   |      |

| Table 103. D-to-A and A-to-D Specifications                                         |      |

| Table 104. Analog-to-Digital Converter (A/D) Electrical Characteristics, TA = 25 °C | 90   |

| Tables                                                                                                    | Р                                    | age |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|-----|

| Table 105. Speaker Gain Control                                                                           |                                      | 91  |

| Table 106. Speaker Driver Specifications                                                                  |                                      |     |

| Table 107. Speaker Driver Electrical Characteristics (TA =                                                | = 25 °C)                             | 92  |

| Table 108. Line Driver Specifications                                                                     |                                      |     |

| Table 109. Line Driver (Analog Test Mode, No A/D/A) Ele                                                   | ctrical Characteristics (TA = 25 °C) | 95  |

| Table 110. Programmable Gain Amplifier Control                                                            |                                      |     |

| Table 111. Programmable Gain Amplifier Specifications                                                     |                                      |     |

| Table 112. Closed-Loop Frequency Response                                                                 |                                      |     |

| Table 113. Programmable Gain Amplifier Electrical Chara                                                   |                                      |     |

| Table 114. Microphone Gain Control (Includes Associated                                                   |                                      |     |

| Table 115. Microphone Preamp and Power Supply Speci-                                                      |                                      |     |

| Table 116. Microphone Preamp Electrical Characteristics                                                   |                                      |     |

| Table 117. System Characteristics Transmit Path Electric                                                  |                                      |     |

| Table 118. System Characteristics Receive Path Electrica                                                  |                                      |     |

| Table 119. Test Conditions                                                                                |                                      |     |

| Table 120. Timing Requirements for Input Clock                                                            |                                      |     |

| Table 121. Timing Requirements for Input Clock and Out                                                    |                                      |     |

| Table 122. Timing Requirements for Powerup Reset and                                                      |                                      |     |

| Table 123. Timing Characteristics for Powerup Reset and                                                   |                                      |     |

| Table 124. Timing Requirements and Characteristics for I                                                  |                                      |     |

| Table 125. Timing Requirements for Powerup Reset with                                                     |                                      |     |

| Table 126. Timing Characteristics for Powerup Reset with                                                  |                                      |     |

| Table 127. Power-Loss Detect Voltage Levels                                                               |                                      |     |

| Table 128. Timing Requirements for Power-Loss Reset w                                                     |                                      |     |

| Table 129. Timing Characteristics for PLACT Response to                                                   |                                      |     |

| Table 130. Timing Requirements for JTAG Input                                                             |                                      |     |

| Table 131. Timing Characteristics for JTAG Input                                                          |                                      |     |

| Table 132. Timing Requirements for Interrupt                                                              |                                      |     |

| Table 133. Timing Requirements for IOP Input Read                                                         |                                      |     |

| Table 134. Timing Characteristics for IOP Output Table 135. Timing Characteristics for External Memory Er | nables (EDOM EDAMLI EDAMLO)          | 114 |

| Table 136. Timing Characteristics for Device Enable                                                       |                                      |     |

| Table 130. Timing Characteristics for Delayed External M                                                  |                                      |     |

| Table 137. Timing Characteristics for External Memory A                                                   |                                      |     |

| Table 139. Timing Requirements for External Memory Re                                                     |                                      |     |

| Table 140. Timing Characteristics for External Memory De                                                  |                                      |     |

| Table 141. Timing Characteristics for Write Cycle Followe                                                 |                                      |     |

| Table 142. Timing Requirements for EXM with Respect to                                                    |                                      |     |

| Table 143. Timing Specification for a DRAM Read Cycle.                                                    |                                      |     |

| Table 144. Timing Specification for a DRAM Write Cycle.                                                   |                                      |     |

| Table 145. Timing Specification for DRAM Control Signals                                                  |                                      |     |

| Table 146. Timing Specification for Refresh with High-Spe                                                 |                                      |     |

| Table 147. Timing Specification for Refresh Under Low-F                                                   |                                      |     |

| Table 148. Timing Specifications for Refresh Interval Und                                                 |                                      |     |

| Table 149. Timing Specifications for Refresh Interval with                                                |                                      |     |

| Table 150. Timing Characteristics for SSI                                                                 |                                      |     |

| Table 151 DSP165X Device Coding                                                                           |                                      | 137 |

## 2 Description (continued)

The DSP1653 is identical to the *FlashDSP*1650 except that it contains mask-programmable internal ROM in place of flash ROM, it does not include an HDS module, and it has only 1.25 Kwords and a single bank of RAM.

The DSP1651 is a subset of the DSP1653. It contains 4 Kwords of internal ROM, 704 words of internal RAM, no external memory interface, and does not include line driver 2, programmable amplifier 2, or AI 5—7.

#### 2.1 Functional Differences Between the DSP1651 and the 80-Pin PLCC FlashDSP1650

The DSP1651 is offered only in the 80-pin MQFP package. It is the production version of 80-pin MQFP FlashDSP 1650. Table 1 lists the differences between the DSP1651 and the 80-pin MQFP FlashDSP1650.

Table 1. Functional Differences Between the DSP1651 and the 80-Pin PLCC FlashDSP 1650

| Difference                      | DSP1651                                                  | FlashDSP1650                                                            |

|---------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|

| ROM                             | 4 Kword (diffusion)                                      | 24 Kword, internal flash                                                |

| RAM                             | One bank of 700 word only (IR2KEN = 0)*                  | 1 bank of 1.25 Kword (IR2KEN = 0)<br>or 2 banks of 1 Kword (IR2KEN = 1) |

| Packages                        | 80-pin MQFP only<br>(Pin VPP is tied to VDD.)            | 68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                              |

| Power-loss Detect Settings      | chipo register bits PLC[2:0]<br>hard-coded with ROM mask | Programmable through <b>chipo</b> register bits PLC[2:0] <sup>†</sup>   |

| Full-speed In-circuit Emulation | JTAG but not HDS <sup>‡</sup>                            | HD supported                                                            |

| I/O Ports                       | 8-bit: 6-bit: 3-bit: A, C, E — B                         | 8-bit: 6-bit: 3-bit:<br>A, C, E — B                                     |

| Line Drivers                    | LDOP, LDON                                               | LDOP, LDON                                                              |

| Programmable Gain Amplifier     | PGIN, PGOUT                                              | PGIN, PGOUT                                                             |

| Analog Interface (AI-)          | I[P, N], 2, 3, 4                                         | I[P, N], 2, 3, 4                                                        |

| External Memory Interface       | None                                                     | None                                                                    |

<sup>\*</sup> For DSP1651, users should reset IR2KEN, chipo[9] = 0. When set, only the memory map in Table 11 applies.

<sup>†</sup> See Table 45 on page 62 for chipo register bits PLC[2:0].

<sup>‡</sup> Still supports read/write to registers and internal RAM, and read of internal ROM if the secure bit is not set.

## 2 Description (continued)

## 2.2 Functional Differences Between the DSP1653 and the 100-Pin TQFP FlashDSP1650

The DSP1653 is offered only in a 100-pin TQFP package. Table 2 lists the differences between the DSP1653 and 100-pin TQFP FlashDSP1650.

Table 2. Functional Differences Between the DSP1653 and the 100-Pin TQFP FlashDSP1650

| Difference                      | DSP1653                                                  |             | FlashDSP1650                                             |           |

|---------------------------------|----------------------------------------------------------|-------------|----------------------------------------------------------|-----------|

| ROM                             | 24 Kword (diffusion                                      | )           | 24 Kword, internal flash                                 | 1         |

| RAM                             |                                                          |             | 1 bank of 1.25 Kword (I<br>or 2 banks of 1 Kword (       |           |

| Packages                        | (Pin VPP is tied to VDD.)                                |             | 68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP               |           |

| Power-loss Detect Settings      | chipo register bits PLC[2:0]<br>hard-coded with ROM mask |             | Programmable through register bits PLC[2:0] <sup>†</sup> | chipo     |

| Full-speed In-circuit Emulation | JTAG but not HDS <sup>‡</sup>                            |             | HD supported                                             |           |

| I/O Ports                       | 8-bit:<br>A, B, C, E                                     | 4-bit:<br>D | 8-bit: 4-<br>A, B, C, D <sup>§</sup> , E –               | bit:<br>– |

<sup>\*</sup> For DSP1653, users should reset IR2KEN, chipo[9] = 0. When set, only the memory map in Table 11 applies.

#### 2.3 Functional Differences Between the DSP1654 and the 100-Pin TQFP FlashDSP1650

The DSP1654 is offered only in a 100-pin TQFP package. Table 3 lists the differences between the DSP1654 and 100-pin TQFP FlashDSP1650.

Table 3. Functional Differences Between the DSP1654 and the 100-Pin TQFP FlashDSP1650

| Difference                 | DSP1654                                                  | FlashDSP1650                                                            |

|----------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|

| ROM                        | 32 Kword VIA                                             | 24 Kword, internal flash                                                |

| RAM                        | One bank of 2 Kword only (IR2KEN = 0)*                   | 1 bank of 1.25 Kword (IR2KEN = 0)<br>or 2 banks of 1 Kword (IR2KEN = 1) |

| Packages                   | 100-pin TQFP only<br>(Pin VPP is tied to VDD.)           | 68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                              |

| Power-loss Detect Settings | chipo register bits PLC[2:0]<br>hard-coded with ROM mask | Programmable through <b>chipo</b> register bits PLC[2:0] <sup>†</sup>   |

| I/O Ports                  | 8-bit:<br>A, B, C, D, E                                  | 8-bit:<br>A, B, C, D <sup>‡</sup> , E                                   |

<sup>\*</sup> For DSP1654, users should reset IR2KEN, **chipo**[9] = 0. When set, only the memory map in Table 11 applies.

<sup>†</sup> See Table 45 on page 62 for chipo register bits PLC[2:0].

<sup>‡</sup> Still supports read/write to registers and internal RAM, and read of internal ROM if the secure bit is not set.

<sup>§</sup> Versions 1, 2, and 3 of FlashDSP 1650 provides IOPD[0:3], the same as DSP1653. Version 4 of FlashDSP 1650 provides IOPD[0:7].

<sup>†</sup> See Table 45 on page 62 for chipo register bits PLC[2:0].

<sup>‡</sup> Versions 1, 2, and 3 of FlashDSP1650 provides IOPD[0:3]. Version 4 of FlashDSP1650 provides IOPD[0:7] the same as DSP1654.

## 2 Description (continued)

## 2.4 Functional Differences Between the DSP1655 and the FlashDSP1650

Table 4 lists the differences between the DSP1655 and FlashDSP1650.

Table 4. Functional Differences Between the DSP1655 and the FlashDSP1650

| Difference                                                                                                                          | DSP1655                                                                                                  | FlashDSP1650                                                                                                                                                                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ROM                                                                                                                                 | 16 Kword on chip                                                                                         | 24 Kword, internal flash                                                                                                                                                          |  |

| RAM                                                                                                                                 | One bank of 1.25 Kword only (IR2KEN = 0)*                                                                | 1 bank of 1.25 Kword (IR2KEN = 0)<br>or 2 banks of 1 Kword (IR2KEN = 1)                                                                                                           |  |

| Packages                                                                                                                            | 68-pin PLCC<br>100-pin TQFP                                                                              | 68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                                                                                                                                        |  |

| Power-loss Detect Settings                                                                                                          | chipo register bits PLC[2:0]<br>hard-coded with ROM mask                                                 | Programmable through <b>chipo</b> register bits PLC[2:0] <sup>†</sup>                                                                                                             |  |

| Full-speed In-circuit Emulation                                                                                                     | JTAG but not HDS <sup>‡</sup>                                                                            | HD supported                                                                                                                                                                      |  |

| I/O Ports:<br>68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                                                                            | 8-bit: 6-bit: 3-bit:<br>A, C, E D B<br>— — — —<br>A, B, C, D, E — —                                      | 8-bit: 6-bit: 3-bit:<br>A, C, E D B<br>A, C, E — B<br>A, B, C, D <sup>§</sup> , E — —                                                                                             |  |

| Line Drivers:<br>68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                                                                         | LDOP, LDON<br>—<br>LDOP, LDON                                                                            | LDOP, LDON<br>LDOP, LDON<br>LDOP, LDON, LDOP2, LDON2                                                                                                                              |  |

| Programmable Gain Amplifier:<br>68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                                                          | PGIN, PGOUT<br>—<br>PGIN, PGOUT                                                                          | PGIN, PGOUT<br>PGIN, PGOUT<br>PGIN, PGOUT, PGIN2, PGOUT2                                                                                                                          |  |

| Analog Interface (AI–):<br>68-pin PLCC<br>80-pin MQFP<br>100-pin TQFP                                                               | I[P, N], 2, 3, 4<br>—<br>I[P, N], 5[P, N], 2, 3, 4                                                       | I[P, N], 2, 3, 4<br>I[P, N], 2, 3, 4<br>I[P, N], 5[P, N], 2, 3, 4, 6, 7                                                                                                           |  |

| External Memory Interface: 68-pin PLCC 80-pin MQFP 100-pin TQFP                                                                     | Address Bus: Data Bus: AB[11:4] DB[15:4] — AB[11:0] DB[15:0]                                             | Address Bus: Data Bus: AB[11:4] DB[15:4]  — — — — — — — — — — — — — — — — — — —                                                                                                   |  |

| JTAG Test Mode Interface: JTSEL: 68-pin PLCC 80-pin MQFP 100-pin TQFP TDO, TDI, TCLK, and TMS: 68-pin PLCC 80-pin MQFP 100-pin TQFP | Multiplexed with IOPD3 — Multiplexed with IOPD3  Multiplexed with IOPC[3:0] — Multiplexed with IOPC[3:0] | Multiplexed with IOPD3 A dedicated pin Multiplexed with IOPD3  Multiplexed with IOPC[3:0] Multiplexed with IOPC[3:0] Can choose to multiplex with IOPC[3:0] or use dedicated pins |  |

<sup>\*</sup> For DSP1655, users should reset IR2KEN, chipo[9] = 0. When set, only the memory map in Table 11 applies.

<sup>†</sup> See Table 45 on page 62 for **chipo** register bits PLC[2:0].

<sup>‡</sup> Still supports read/write to registers and internal RAM, and read of internal ROM if the secure bit is not set.

<sup>§</sup> Version 4 of FlashDSP 1650 provides IOPD[0:7]. Versions 1, 2, and 3 provides only IOPD[0:3].

## 3 Pin Information

The FlashDSP1650 is available in the following packages:

- 68-pin PLCC (See Figure 1.)

- 80-pin MQFP (See Figure 2 on page 14.)

- 100-pin TQFP (See Figure 3 on page 15.)

- 1.  $\ensuremath{V_{PP}}$  becomes  $\ensuremath{V_{DD}}$  for nonflash versions of the device.

- 2. DOUT is also known as CKO.

Note: VDDPLM and VDDD are connected to the same pin.

Figure 1. FlashDSP1650 68-Pin PLCC Pin Diagram

5-3995(C).a

<sup>\*</sup> VPP becomes VDD for nonflash versions of the device, i.e., DSP1651 and DSP1653.

5-4003(C).a

Figure 2. FlashDSP1650 80-Pin MQFP Pin Diagram

$<sup>^{\</sup>star}$  VPP becomes VDD for nonflash versions of the device, i.e., DSP1651 and DSP1653.

5-4003(C).a

Figure 3. FlashDSP1650 100-Pin TQFP Pin Diagram

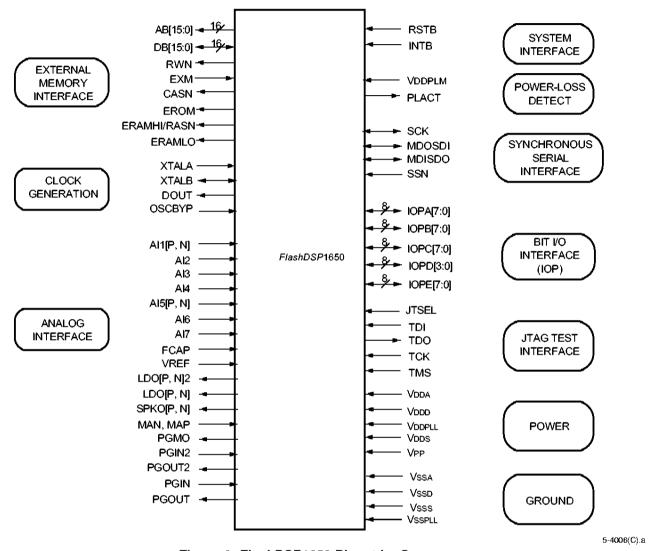

Figure 4 shows *FlashDSP* 1650 pins organized into their functional groups. Tables 5 and 6 and Sections 3.1 through 3.11 describe these pins.

Figure 4. FlashDSP1650 Pinout by Group

Note: The FlashDSP1650 80-pin MQFP package has no AB[15:0], AI[7:6], AI5N, AI5P, DB[15:0], EXM, IOPB3, IOPD[2:0], EROM, ERAMLO, LDON2, LDOP2, PGIN2, PGOUT2, RASN/ERAMHI, CASN, or RWN pin.

For each FlashDSP1650 pin listed in Table 5:

- Each entry in the Type column is one of the following:

- —I (input)

- —I/O (input/output)

- —O (output)

- -OD (open-drain output)

- —TO (3-state output)

- Each entry in the Active column is one of the following:

- —High

- —Low

- —Pgm (programmable polarity)

- -Neg (negative edge triggered)

Table 5. FlashDSP1650 Pinout

|                 | Pin Number     |                 |      |        |                                                                                                  |  |

|-----------------|----------------|-----------------|------|--------|--------------------------------------------------------------------------------------------------|--|

| Symbol          | 80-Pin<br>MQFP | 100-Pin<br>TQFP | Туре | Active | Pin Description                                                                                  |  |

| AB[2:0]         | _              | 63—65           | 0    | High   | 16-bit external memory address bus, bits 15—0.                                                   |  |

| AB[3]           |                | 67              |      |        | Pins AB[15:4] are multiplexed with IOPB[4:7] and                                                 |  |

| AB[8:4]         |                | 68—72           |      |        | IOPE[0:7] in the 100-pin TQFP. (The 80-pin MQFP has no AB pins, but does have IOP pins.)         |  |

| AB[15:9]        |                | 77—83           |      |        | , ,                                                                                              |  |

| Al1 N           | 43             | 27              | I    | _      | Differential analog pair.                                                                        |  |

| Al1P            | 44             | 28              |      |        |                                                                                                  |  |

| Al5N            |                | 23              | I    | _      | Second differential analog pair. (The 80-pin MQFP                                                |  |

| AI5P            |                | 22              |      |        | has no Al5N or Al5P pins.)                                                                       |  |

| AI[7:6]         | _              | 19—20           | I    | _      | Single-ended analog inputs. (The 80-pin MQFP has                                                 |  |

| Al4             | 38             | 21              |      |        | no Al[7:6] pins.)                                                                                |  |

| AI[3:2]         | 46—45          | 30—29           |      |        |                                                                                                  |  |

| CASN            | _              | 5               | 0    | Low    | Column address select; multiplexed with IOPD1. (The 80-pin MQFP has no CASN pin.)                |  |

| DB[5:0]         | _              | 49—44           | 1/0  | High   | Data bus for read or write transaction to external                                               |  |

| DB[15:6]        | _              | 61—52           |      |        | memory data bus. DB[15:8] are multiplexed with IOPA[7:0]. (The 80-pin MQFP has no DB pins.)      |  |

| DOUT            | 28             | 9               | 0    | High   | Processor clock; digital output/clock output.                                                    |  |

| ERAMHI/<br>RASN |                | 8               | 0    | Low    | External RAM, high select, or row address select. (The 80-pin MQFP has no ERAMHI/RASN pin.)      |  |

| ERAMLO          | _              | 6               | 0    | Low    | External RAM, low select; multiplexed with IOPD0. (The 80-pin MQFP has no ERAMLO pin.)           |  |

| EROM            | _              | 4               | 0    | Low    | External ROM select; multiplexed with IOPD2. (The 80-pin MQFP has no EROM pin.)                  |  |

| EXM             | _              | 86              | I    | High   | External memory enable; multiplexed with IOPB2. (The 80-pin MQFP has no EXM pin.)                |  |

| FCAP            | 34             | 15              | 0    | _      | Microphone power supply output.                                                                  |  |

| INTB            | 11             | 88              | I    | Neg    | External interrupt, negative edge triggered; multiplexed with IOPB0.                             |  |

| IOPA[7:0]       | 73—66          | 61—54           | I/O  | Pgm    | I/O port A (bits 7—0). (In the 100-pin TQFP, pins IOPA[7:0] are multiplexed with pins DB[15:8].) |  |

Table 5. FlashDSP1650 Pinout (continued)

|           | Pin N          | Pin Number      |      |        |                                                                                                                                                                            |  |

|-----------|----------------|-----------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol    | 80-Pin<br>MQFP | 100-Pin<br>TQFP | Туре | Active | Pin Description                                                                                                                                                            |  |

| IOPB[7:4] | _              | 80—83           | I/O  | Pgm    | I/O port B (bits 7—0). (The 80-pin MQFP has no                                                                                                                             |  |

| IOPB[3]   | <del>-</del>   | 85              | 1    |        | IOPB[7:3] pins. In the 100-pin TQFP, pins                                                                                                                                  |  |

| IOPB[2:0] | 9—11           | 86—88           |      |        | IOPB[7:4] are multiplexed with pins AB[12:15], and pin IOPB2 is multiplexed with EXM. In both packages, IOPB[1:0] are multiplexed with pins PLACT and INTB, respectively.) |  |

| IOPC[7:2] | 13—18          | 89—94           | I/O  | Pgm    | I/O port C (bits 7—0); multiplexed with pins                                                                                                                               |  |

| IOPC[1:0] | 19—20          | 97—98           |      |        | MDISDO, MDOSDI, SCK, SSN, TDO, TDI, TCK, and TMS, respectively.                                                                                                            |  |

| IOPD[3:0] | _              | 3—6             | I/O  | Pgm    | I/O port D (bits 3—0); multiplexed with pins JTSEL, EROM, CASN, and ERAMLO, respectively. (The 80-pin MQFP has no IOPD pins.)                                              |  |

| IOPE[7:3] | 75—79          | 68—72           | I/O  | Pgm    | I/O port E (bits 7—0). (In the 100-pin TQFP, pins                                                                                                                          |  |

| IOPE[2:0] | 3—5            | 77—79           | 1    |        | IOPE[7:0] are multiplexed with pins AB[4:11].)                                                                                                                             |  |

| JTSEL     | 27             | 3               | I    | High   | JTAG select. (In the 100-pin TQFP, JTSEL is multiplexed with IOPD3.)                                                                                                       |  |

| LDOP      | 50             | 37              | 0    | _      | Differential output for interface to a telephone line.                                                                                                                     |  |

| LDON      | 51             | 38              | 1    |        |                                                                                                                                                                            |  |

| LDOP2     | _              | 35              | 0    | _      | Second differential output to telephone line. (The                                                                                                                         |  |

| LDON2     | _              | 36              | 1    |        | 80-pin MQFP has no LDOP2 or LDON2 pins.)                                                                                                                                   |  |

| MAN       | 35             | 16              | 1    | _      | Microphone amplifier positive and negative inputs.                                                                                                                         |  |

| MAP       | 36             | 17              | ]    |        |                                                                                                                                                                            |  |

| MDISDO    | 13             | 89              | I/O  | _      | SSI master data in/slave data out; multiplexed with IOPC7.                                                                                                                 |  |

| MDOSDI    | 14             | 90              | I/O  | _      | SSI master data out/slave data in; multiplexed with IOPC6.                                                                                                                 |  |

| OSCBYP    | 29             | 10              | I    | High   | Oscillator bypass.                                                                                                                                                         |  |

| PGIN      | 47             | 31              | I    | _      | Programmable gain input.                                                                                                                                                   |  |

| PGIN2     |                | 33              |      | _      | Programmable gain input for two-line applications. (The 80-pin MQFP has no PGIN2 pin.)                                                                                     |  |

| PGMO      | 37             | 18              | 0    | _      | Programmable gain amplifier output for the microphone amplifier.                                                                                                           |  |

| PGOUT     | 48             | 32              | 0    | _      | Programmable gain output.                                                                                                                                                  |  |

| PGOUT2    | _              | 34              | 0    | _      | Programmable gain output for two-line application (The 80-pin MQFP has no PGOUT2 pin.)                                                                                     |  |

| PLACT     | 10             | 87              | 0    | High   | Power-loss active; multiplexed with IOPB1.                                                                                                                                 |  |

| RSTB      | 22             | 99              | I/O  | Low    | Reset.                                                                                                                                                                     |  |

| RWN       | _              | 7               | 0    | _      | Read/write not. (The 80-pin MQFP has no RWN pin.)                                                                                                                          |  |

| SCK       | 15             | 91              | I/O  | _      | SSI serial clock; multiplexed with IOPC5.                                                                                                                                  |  |

| SPKON     | 55             | 41              | 0    | _      | Speaker differential outputs.                                                                                                                                              |  |

| SPKOP     | 54             | 40              | 1    |        |                                                                                                                                                                            |  |

| SSN       | 16             | 92              | I    | Low    | SSI serial slave select; multiplexed with IOPC4.                                                                                                                           |  |

Table 5. FlashDSP1650 Pinout (continued)

|        | Pin Number     |                 |      |                                |                                                                                                                 |  |

|--------|----------------|-----------------|------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Symbol | 80-Pin<br>MQFP | 100-Pin<br>TQFP | Туре | Active                         | Pin Description                                                                                                 |  |

| TCK    | 19             | 96 and 97       | I    |                                | Test clock (JTAG). (In the 100-pin TQFP, TCK is connected to two pins; pin 97 is multiplexed with IOPC1.)       |  |

| TDI    | 18             | 95 and 94       | I    | High                           | Test data in (JTAG). (In the 100-pin TQFP, TDI is connected to two pins; pin 94 is multiplexed with IOPC2.)     |  |

| TDO    | 17             | 74 and 93       | 0    | High                           | Test data in (JTAG). (In the 100-pin TQFP, TDO is connected to two pins; pin 93 is multiplexed with IOPC3.)     |  |

| TMS    | 20             | 73 and 98       | I    | High                           | Test mode select (JTAG). (In the 100-pin TQFP, TMS is connected to two pins; pin 98 is multiplexed with IOPC0.) |  |

| VDDPLM | 26             | 2               | I    | High                           | VDD power-loss monitor.                                                                                         |  |

| VREF   | 39             | 24              | I    | _                              | Voltage reference for the converter.                                                                            |  |

| XTALA  | 32             | 13              | I/O  | Crystal oscillator connection. |                                                                                                                 |  |

| XTALB  | 31             | 12              |      |                                |                                                                                                                 |  |

Table 6. FlashDSP1650 Power Supply, Ground, and Unconnected Pins

| Cumbal | Pin Nu                                        | umber               | Din Decements on                                                                                              |  |

|--------|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------|--|

| Symbol | 80-Pin MQFP                                   | 100-Pin TQFP        | Pin Description                                                                                               |  |

| VDDA   | 41                                            | 26                  | Supply for analog circuitry (5 V or 3.3 V).                                                                   |  |

| Vssa   | 40                                            | 25                  | Ground for analog circuitry.                                                                                  |  |

| VDDD   | 1, 25, 65                                     | 1, 51, 66, 76       | Supply for digital circuitry (5 V or 3.3 V).                                                                  |  |

| Vssd   | 8, 24, 64, 80                                 | 50, 62, 75, 84, 100 | Ground for digital circuitry.                                                                                 |  |

| VDDPLL | 30                                            | 11                  | Supply for phase-locked loop (should be connected to VDDD).                                                   |  |

| VSSPLL | 33                                            | 14                  | Ground for phase-locked loop (should be connected to VSSD).                                                   |  |

| VDDS   | 56                                            | 42                  | Supply for speaker driver.                                                                                    |  |

| Vsss   | 53                                            | 39                  | Ground for speaker driver.                                                                                    |  |

| VPP    | 57                                            | 43                  | Programming supply for flash ROM. VPP becomes a VDD pin for nonflash devices (DSP1651, DSP1652, and DSP1653). |  |

| NC     | 2, 6, 7, 12, 21, 23, 42,<br>49, 52, 58—63, 74 | <u>—</u>            | No connection.                                                                                                |  |

## 3.1 System Interface

#### 3.1.1 XTALA, XTALB

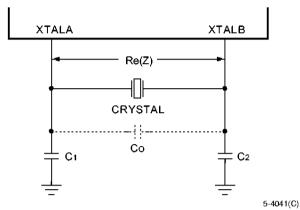

Crystal Oscillator. Input/Output. The external crystal is connected between these two pins, which places the crystal in the feedback loop of the on-chip crystal oscillator. The output of the crystal oscillator is used as a reference for the phase-locked loop (PLL) and codec. The frequency of the oscillator input must be 4.096 MHz.

#### 3.1.2 RSTB