# **Signetics**

# NE/SA/SE5105/A Precision High-Speed Comparator With Latch

**Product Specification**

#### **Linear Products**

#### DESCRIPTION

The NE/SA/SE5105/A is a precision high-speed comparator ideally suited for applications requiring ultra-precision and speed. A typical application may be in a 12-bit successive approximation A/D converter. Input offset voltage is factory trimmed to typically 100 µV (0.04 LSB for a 12-bit, 10V system); the 36ns response time (measured at 1.2mV overdrive), low input offset current, and high gain remain essentially constant over the entire operating temperature range. Thus, the same degree of precision and speed can be maintained over the specified temperature range. A latch function incorporated with the comparator allows added flexibility to the system designer. A TTL high input at the latch enable pin forces the output of the comparator to stay at its existing logical state irrespective of subsequent signal transitions at the input.

#### **FEATURES**

- Precision input stage: Input offset voltage 100μV Input offset current 3nA

- Fast response time: 5mV overdrive 32ns

1.2mV overdrive 36ns

- High voltage gain 26,000V/V

- Low power dissipation 100mW

- TTL output capable of driving 10 TTL gates

- Latch function with TTL compatible input

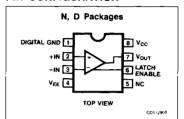

#### PIN CONFIGURATION

#### **APPLICATIONS**

- High-speed, high-resolution successive approximation A/D converters

- Precision zero-crossing detectors

- Precision latching window comparators

- Fast latching ECL-to-TTL line translators

- Precision signal regenerators

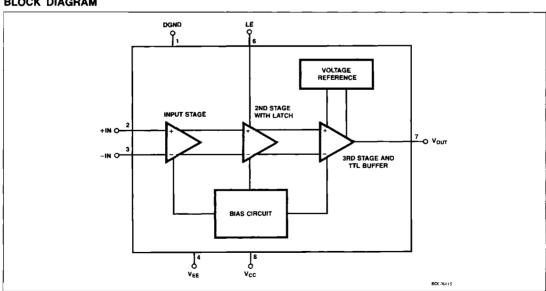

#### BLOCK DIAGRAM

NE/SA/SE5105/A

#### ORDERING INFORMATION

| DESCRIPTION       | TEMPERATURE RANGE | ORDER CODE |

|-------------------|-------------------|------------|

| 8-Pin Plastic DIP | 0 to +70°C        | NE5105AN   |

| 8-Pin Plastic DIP | 0 to +70°C        | NE5105N    |

| 8-Pin Plastic DIP | -40°C to +85°C    | SA5105AN   |

| 8-Pin Plastic DIP | -40°C to +85°C    | SA5105N    |

| 8-Pin Plastic SO  | 0 to +70°C        | NE5105AD   |

| 8-Pin Plastic SO  | 0 to +70°C        | NE5105D    |

| 8-Pin Plastic SO  | -40°C to +85°C    | SA5105AD   |

| 8-Pin Plastic SO  | -40°C to +85°C    | SA5105D    |

| 8-Pin Plastic DIP | -55°C to +125°C   | SE5105AN   |

| 8-Pin Plastic DIP | -55°C to +125°C   | SE5105N    |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                             | PARAMETER                                                                                                            | RATING                                | UNIT           |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|

| V <sub>CC</sub><br>V <sub>EE</sub> | Power supply Power supply                                                                                            | +6<br>-18                             | V<br>V         |

| P <sub>D MAX</sub>                 | Maximum power dissipation,<br>T <sub>A</sub> = 25°C (still-air) <sup>1</sup><br>FE package<br>N package<br>D package | 885<br>1160<br>780                    | mW<br>mW<br>mW |

|                                    | Differential input voltage                                                                                           | ± 5                                   | V              |

|                                    | LATCH ENABLE input voltage                                                                                           | V <sub>CC</sub> to V <sub>EE</sub>    | V              |

| T <sub>STG</sub>                   | Storage temperature range                                                                                            | -65 to +150                           | °C             |

| T <sub>A</sub>                     | Operating temperature range<br>SE5105 (FE package)<br>SA5105 (N and D package)<br>NE5105 (N and D package)           | -55 to +125<br>-40 to +85<br>0 to +70 | ္ ့<br>ပဲ ့ ပဲ |

| I <sub>SC</sub>                    | Output short-circuit duration<br>To ground<br>To V <sub>CC</sub>                                                     | Indefinite<br>1                       | Minute         |

#### NOTE:

<sup>1.</sup> Derate above 25°C, at the following rates:

FE package at 6.75mW/°C. N package at 9.3mW/°C.

D package at 6.2mW/°C.

# NE/SA/SE5105/A

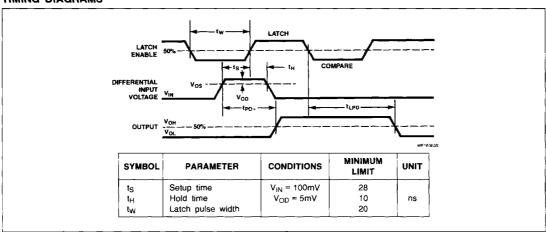

#### TIMING DIAGRAMS

NE/SA/SE5105/A

DC ELECTRICAL CHARACTERISTICS  $V_{CC} = +5V$ ,  $V_{EE} = -5V$ ,  $T_A = 25^{\circ}C$ ;  $V_{+\,IN} = V_{-\,IN} = 0V$  and Latch Enable grounded, unless otherwise noted.

| SYMBOL          | PARAMETER                                 | TEST CONDITIONS                                                                                            | 5105A      |            |            | 5105       |            |            |          |

|-----------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|----------|

|                 |                                           |                                                                                                            | Min        | Тур        | Max        | Min        | Тур        | Max        | UNIT     |

| Vos             | Input offset voltage                      | $H_S = 25\Omega$ , $V_{CM} = 0V$<br>$H_S = 25\Omega$ , $V_{CM} = \pm 3V$                                   |            | 100<br>140 | 250<br>400 |            |            | 600<br>750 | μV       |

| los             | Input offset current                      | V <sub>LATCH</sub> = V <sub>CC</sub>                                                                       |            | 3          | 20         |            |            | 40         | лА       |

| I <sub>B</sub>  | Input bias current                        | V <sub>LATCH</sub> = V <sub>CC</sub>                                                                       |            | 400        | 1200       |            |            | 1400       | nA       |

| A <sub>VO</sub> | Voltage gain <sup>1</sup>                 |                                                                                                            | 18         | 26         |            | 18         | 26         | -          | V/mV     |

| CMVR            | Input voltage range                       |                                                                                                            | ± 3        | ± 3.3      |            | ± 3        | ± 3.3      |            | ٧        |

| CMRR            | Common mode rejection ratio               | $V_{CM} = \pm 3V$                                                                                          | 86         | 99         |            | 84         |            |            | ₫B       |

| PSRR            | Power supply rejection ratio              | $V_{CC}/V_{EE} = \pm 4.5V$ to $\pm 5.5V$<br>$V_{CC} = +5V$ and<br>$V_{EE} = -4.5V$ to $-15V$               | 78<br>86   | 94<br>104  |            | 78<br>84   |            |            | dB<br>dB |

| V <sub>OH</sub> | Output high voltage                       | $V_{IN} \ge 10$ mV, $I_{OH} = 0\mu$ A<br>$V_{IN} \ge 10$ mV, $I_{OH} = 400\mu$ A                           | 2.4<br>2.4 | 2.8<br>2.6 |            | 2.4<br>2.4 | 2.8<br>2.6 |            | V<br>V   |

| VOL             | Output low voltage                        | $V_{IN} \le 10 \text{mV}, \ I_{OL} = 0 \mu \text{A}$<br>$V_{IN} \le 10 \text{mV}, \ I_{OL} = 16 \text{mA}$ |            | 0.2<br>0.3 | 0.4<br>0.4 |            | 0.2<br>0.3 | 0.4<br>0.4 | V<br>V   |

| Icc             | Positive supply current                   | $V_0 \le 0.4V, I_0 = 0\mu A$                                                                               |            | 11         | 14         |            |            | 16         | mA       |

| IEE             | Negative supply current                   | $V_O \le 0.4V$ , $I_O = 0\mu A$                                                                            |            | 9          | 12         |            |            | 14         | mA       |

| PD              | Power dissipation                         |                                                                                                            |            | 100        | 130        |            |            | 150        | mW       |

| V <sub>LH</sub> | Logic 1 at latch input                    |                                                                                                            | 2          |            |            | 2          | _          |            | v        |

| V <sub>LL</sub> | Logic 0 at latch input                    |                                                                                                            |            |            | 0.8        |            |            | 0.8        | ٧        |

| լ<br>լ<br>լ     | Latch input current<br>Logic 1<br>Logic 0 | V <sub>LATCH</sub> = 3V<br>V <sub>LATCH</sub> = 0.8V                                                       |            | 4          | 20<br>5    |            | 4          | 20<br>5    | μA<br>μA |

| R <sub>IN</sub> | Differential input resistance             |                                                                                                            |            | 1000       |            |            | 1000       |            | МΩ       |

NOTE:

<sup>1.</sup> Guaranteed by design.

NE/SA/SE5105/A

# DC ELECTRICAL CHARACTERISTICS $V_{CC}$ = +5V, $V_{EE}$ = -5V; -55°C $\leq$ T<sub>A</sub> $\leq$ +125°C for SE5105A/5105; $-40^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +85°C for SA5105A/5105; and, 0°C $\leq$ T<sub>A</sub> $\leq$ +70°C for NE5105A/5105. $V_{+IN}$ = 0V and Latch Enable grounded, unless otherwise noted.

| SYMBOL             | PARAMETER                                 | TEST CONDITIONS                                                                                            |            | 5105A        |             |            | 5105         |             |          |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------|------------|--------------|-------------|------------|--------------|-------------|----------|

|                    |                                           |                                                                                                            | Min        | Тур          | Max         | Min        | Тур          | Max         | UNIT     |

| Vos                | Input offset voltage                      | $R_S = 25\Omega$ , $V_{CM} = 0V$<br>$R_S = 25\Omega$ , $V_{CM} = \pm 3V$                                   |            | 0.25<br>0.3  | 0.6<br>0.75 | -          |              | 1<br>1.2    | mV       |

| TC V <sub>OS</sub> | Input offset voltage drift                | V <sub>CM</sub> = 0V                                                                                       |            | 1.5          | 7.5         |            |              | 10          | μV/°C    |

| los                | Input offset current                      | V <sub>LATCH</sub> = V <sub>CC</sub>                                                                       |            | 4            | 25          |            |              | 60          | nA       |

| IB                 | Input bias current                        | V <sub>LATCH</sub> = V <sub>CC</sub>                                                                       |            | 0.5          | 1.5         |            |              | 1.8         | μΑ       |

| Avo                | Voltage gain <sup>1</sup>                 |                                                                                                            | 16         | 23           |             | 16         | 23           |             | V/mV     |

| CMVR               | input voltage range                       |                                                                                                            | ± 3        | ± 3.2        |             | ± 3        | ± 3.2        |             | ٧        |

| CMRR               | Common mode rejection ratio               | V <sub>CM</sub> = ± 3V                                                                                     | 83         | 93           |             | 80         |              |             | dB       |

| PSRR               | Power supply rejection ratio              | $V_{CC}/V_{EE} = \pm 4.5V$ to $\pm 5.5V$<br>$V_{CC} = +5V$ and<br>$V_{FF} = -4.5V$ to $-15V$               | 75<br>75   | 94<br>94     |             | 72<br>72   |              |             | dB<br>dB |

| V <sub>OH</sub>    | Output high voltage                       | $V_{IN} \ge 10 \text{mV}, I_{OH} = 0 \mu \text{A}$<br>$V_{IN} \ge 10 \text{mV}, I_{OH} = 320 \mu \text{A}$ | 2.4<br>2.4 | 34           |             | 2.4<br>2.4 |              |             | V        |

| V <sub>OL</sub>    | Output low voltage <sup>2</sup>           | $V_{IN} \le 10$ mV, $I_{OL} = 9.6$ mA<br>$V_{IN} \le 10$ mV, $I_{OL} = 12.8$ mA                            |            | 0.28<br>0.35 | 0.4<br>0.45 |            | 0.28<br>0.35 | 0.4<br>0.45 | V<br>V   |

| Icc                | Positive supply current                   | $V_{O} < 0.4V$ , $I_{O} = 0 \mu A$                                                                         |            | 15           | 19          |            |              | 22          | mA       |

| IEE                | Negative supply current                   | $V_0 \le 0.4V, I_0 = 0\mu A$                                                                               |            | 12           | 17          |            |              | 20          | mA       |

| PD                 | Power dissipation                         |                                                                                                            |            | 135          | 180         |            |              | 210         | mW       |

| V <sub>LH</sub>    | Logic 1 at latch input                    |                                                                                                            | 2          |              |             | 2          |              |             | ٧        |

| V <sub>LL</sub>    | Logic 0 at latch input                    |                                                                                                            |            |              | 8.0         |            |              | 0.8         | ν        |

| I <sub>LH</sub>    | Latch input current<br>Logic 1<br>Logic 0 | V <sub>LATCH</sub> = 3V<br>V <sub>LATCH</sub> = 0.8V                                                       |            | 6<br>1       | 20<br>10    |            | 6            | 20<br>10    | μA<br>μA |

| R <sub>IN</sub>    | Differential input resistance             |                                                                                                            |            | 1000         |             |            | 1000         |             | МΩ       |

#### NOTES:

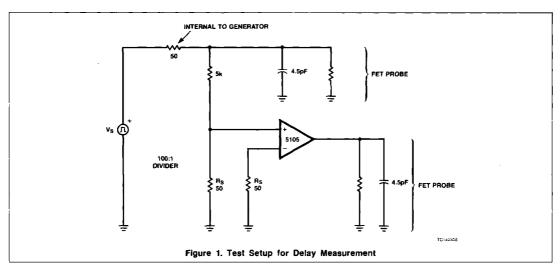

# AC ELECTRICAL CHARACTERISTICS V<sub>CC</sub> = +5V; V<sub>EE</sub> = -5V; T<sub>A</sub> = 25°C and Latch Enable grounded, unless otherwise noted.

| SYMBOL            | PARAMETER                                              |                                                  | 5   |          |     |          |

|-------------------|--------------------------------------------------------|--------------------------------------------------|-----|----------|-----|----------|

|                   |                                                        | TEST CONDITIONS                                  | Min | Тур      | Max | UNIT     |

| t <sub>PD+</sub>  | Input to output high propagation delay <sup>1, 2</sup> | V <sub>OD</sub> = 1.2mV<br>V <sub>OD</sub> = 5mV |     | 36<br>32 | 50  | ns<br>ns |

| t <sub>PD</sub> _ | Input to output low propagation delay <sup>1, 2</sup>  | $V_{OD} = 1.2 \text{mV}$ $V_{OD} = 5 \text{mV}$  |     | 34<br>32 | 50  | ns<br>ns |

| t <sub>LPD</sub>  | Latch disable time <sup>1, 2</sup>                     |                                                  |     | 25       | 38  | ns       |

#### NOTES:

<sup>1.</sup> Guaranteed by design.

<sup>2.</sup>  $V_{OL} = 0.45V$  max at  $T_A \le -40$ °C and  $I_{OL} = 12.8$ mA.

<sup>1.</sup> Guaranteed by design.

<sup>2.</sup> Times are for 100mV step inputs. See Timing Diagrams, Figures 3 and 4.

NE/SA/SE5105/A

# AC ELECTRICAL CHARACTERISTICS $V_{CC} = +5V$ ; $V_{EE} = -5V$ ; $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ for SE5105A/5105; $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ for SA5105/5105A, and, $0^{\circ}C \le T_{A} \le +70^{\circ}C$ for NE5105A/5105

Latch Enable grounded, unless otherwise noted.

| SYMBOL            | PARAMETER                                              |                                                 | 5   |          |     |          |

|-------------------|--------------------------------------------------------|-------------------------------------------------|-----|----------|-----|----------|

|                   |                                                        | TEST CONDITION                                  | Min | Тур      | Max | UNIT     |

| t <sub>PD+</sub>  | Input to output high propagation delay <sup>1, 2</sup> | $V_{OD} = 1.2 \text{mV}$ $V_{OD} = 5 \text{mV}$ |     | 50<br>45 |     | ns<br>ns |

| t <sub>PD</sub> _ | Input to output low propagation delay <sup>1, 2</sup>  | $V_{OD} = 1.2 \text{mV}$ $V_{OD} = 5 \text{mV}$ |     | 43<br>40 |     | ns<br>ns |

| t <sub>LPD</sub>  | Latch disable time <sup>1, 2</sup>                     |                                                 | 1   | 34       |     | ns       |

#### NOTES:

- 1. Guaranteed by design.

- 2. Times are for 100mV step inputs. See Timing Diagrams, Figures 3 and 4.

#### SYMBOLS AND DEFINITIONS

#### Common-Mode Rejection Ratio (CMRR)

The ratio of the change in common-mode voltage to the corresponding change in  $V_{OS}$ . CMRR is expressed in dB, CMRR = 20 log  $(\Delta CMV/\Delta V_{OS})$ .

#### Differential Input Resistance (RIN)

Resistance looking into either input terminal with the other referred to a specified voltage.

#### Input Bias Current (IBIAS)

The current into either input terminal with both inputs referred to a specified voltage.

#### Input Offset Current (IOS)

The difference between the two input bias currents with both inputs referred to a specified voltage

#### Input Offset Voltage (Vos)

The minimum potential difference required between the input terminals to force the output to a specified voltage.

#### Input Offset Voltage Drift (TCVOS)

The ratio of the change in  $V_{OS}$  to the change in temperature as that temperature deviates from a +25°C ambient.

# Input to Output Propagation Delay (tpp+ and tpp-)

The propagation delay measured from the time the input signal crosses V<sub>OS</sub> to the 50% transition point of the output signal. Delay is measured with a specified input step size (V<sub>ID</sub>) and overdrive (V<sub>OD</sub>).

#### Input Voltage Range (CMVR)

The range of common-mode voltage at the input for which operation within specifications is guaranteed.

#### Latch Disable Propagation Delay (t<sub>LPD</sub>)

The propagation delay measured between the 50% transition points of the LATCH ENABLE signal falling edge and the output signal transition point.

#### Latch Hold Time (tu)

The minimum time after the positive transition of the LATCH ENABLE signal that the input signal must remain unchanged in order to be acquired and held at the output. Hold time is measured from the 50% transition point of the LATCH ENABLE signal to the point where comparator input signal crosses V<sub>OS</sub>.

#### Latch Pulse Width (tw)

The minimum time that the LATCH ENABLE signal must be low in order to acquire and subsequently hold the input signal change. Pulse width is measured between the 50% transition points of the falling and rising edges of the latch pulse.

#### Latch Setup Time (ts)

The minimum time before the positive transition of the LATCH ENABLE signal that an input signal change must be present in order to be acquired and held at the output. Setup time is measured from the point the input signal crosses  $V_{OS}$  to the 50% transition point of the LATCH ENABLE signal.

#### Output High Current (IOH)

The current that the comparator output can source at a specified output voltage and input overdrive.

#### Output High Voltage (VOH)

The high output voltage with a specified source current and input overdrive.

#### Output Low Voltage (VOL)

The low output voltage with a specified sink current and input overdrive.

#### Output Sink Current (IOL)

The current that the comparator output can sink at a specified output voltage and input overdrive.

#### Overdrive (V<sub>OD</sub>)

The applied input differential voltage in excess of input offset voltage  $(V_{OS})$ .

#### Power Supply Rejection Ratio (PSRR)

The ratio of the change in input offset voltage to the specified change in power supply voltage.

#### Voltage Gain (A<sub>V</sub>)

The ratio of the change in output voltage (over a specified range) to the change in differential input voltage.

#### APPLYING THE NE/SA/SE5105/A

#### PC Board Layout

As with any high-speed circuit, layout of the PC board becomes critical for optimum performance. The supplies should be bypassed with good high frequency capacitors mounted as close to the IC as possible. A combination of high frequency ceramic and tantalum capacitors provide adequate suppression of transients on the supply lines. Since the comparator is an uncompensated amplifier with high gain, even a small amount of feedback from the output to the input can cause oscillation. A poor layout of the PC board not only increases the uncertainty region (due to oscillation) of the comparator, but also introduces hysteresis. Use of ground planes is essential since ground planes not only minimize inductance, but also reduce stray feedback capacitances by referring them to ground. Separate analog and digital ground planes should be used; the inputs are referred to the analog ground while the supplies and output are referred to the digital ground (Pin 1). Furthermore, the analog and digital ground planes should only meet at one point. Comparator output and input pins should be isolated from each other along with the traces from the respective pins. Stray capacitance from the IC pins to ground can be minimized by keeping the lead lengths and traces as short as possible.

### NE/SA/SE5105/A

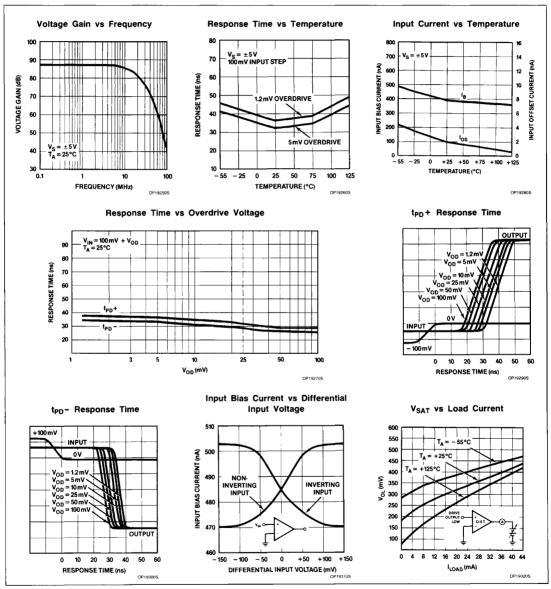

#### TYPICAL PERFORMANCE CHARACTERISTICS

March 1, 1988 5-267

# NE/SA/SE5105/A

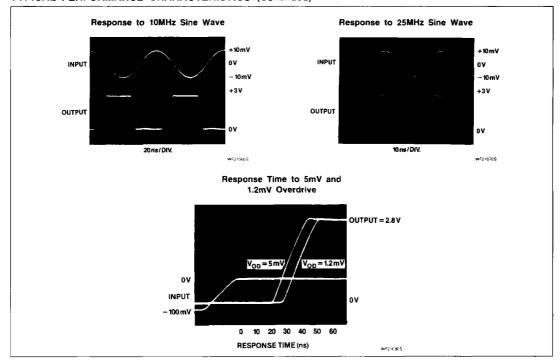

#### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

March 1, 1988 5-268