# JOLOGY 550MHz, 2200V/µs Gain of 1, Single Supply Triple Video Amplifier with Input Bias Control

### **FEATURES**

- -3dB Small-Signal Bandwidth: 550MHz

- -3dB 2V<sub>P-P</sub> Large-Signal Bandwidth: 400MHz

- Slew Rate: 2200V/µs

- Fixed Gain of 1, No External Resistors Required

- AC Coupling with Programmable DC Input Bias

- Output Swings to 0.8V of Supply Rails

- Full Video Swing with 5V Single Supply

- Differential Gain: 0.02%

- Differential Phase: 0.02°

- Enable/Shutdown Pin

- High Output Current: ±90mA

- Supply Range: 3V to 7.5V

- Operating Temperature Range: –40°C to 85°C

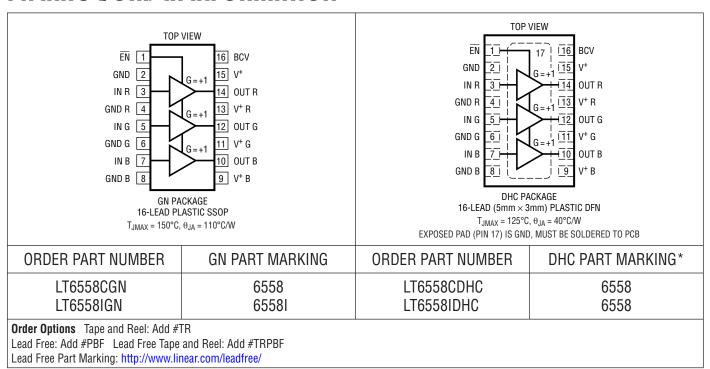

- Available in 16-Lead SSOP and 5mm × 3mm DFN Packages

### **APPLICATIONS**

- LCD Video Projectors

- RGB HD Video Amplifiers

- Coaxial Cable Drivers

- Low Supply ADC Drivers

### DESCRIPTION

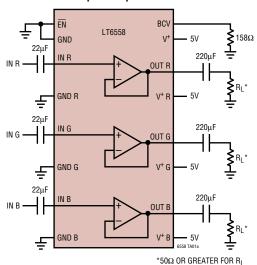

The LT®6558 is a high speed triple video amplifier with an internal fixed gain of 1 and a programmable DC input bias voltage. This amplifier features a 400MHz  $2V_{P-P}$  signal bandwidth, 2200V/ $\mu$ s slew rate and a unique ability to drive heavy output loads to 0.8V of the supply rails, making the LT6558 ideal for a single 5V supply, wideband video application. With just one resistor, the inputs of all three amplifiers can be programmed to a common voltage level, simplifying and reducing the need for external circuitry in AC-coupled applications. Without the programming resistor, the input bias circuit becomes inactive, allowing the use of an external clamp circuit or direct coupled input.

The LT6558 has separate power supply and ground pins for each amplifier to improve channel separation and to ease power supply bypassing. The LT6558 provides uncompromised performance in many high speed applications where a low voltage, single supply is required.

The LT6558 is available in 16-lead SSOP and  $5 \text{mm} \times 3 \text{mm}$  DFN packages.

(T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

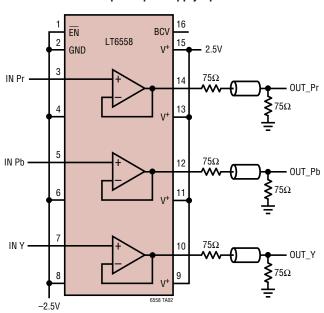

### TYPICAL APPLICATION

#### **AC-Coupled Triple Video Driver**

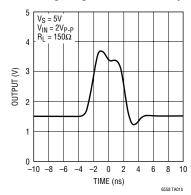

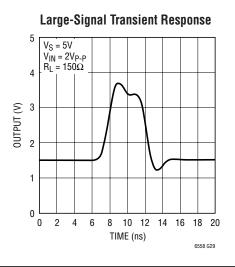

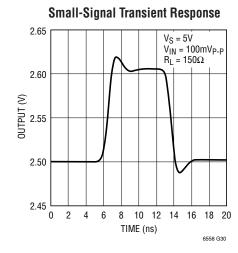

#### Fast Large-Signal Transient Response

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Total Supply Voltage (V <sub>S</sub> <sup>+</sup> to GND) | 7.5V          |

|-----------------------------------------------------------|---------------|

| Input Current                                             | ±10mA         |

| Output Current (Note 2)                                   | ±90mA         |

| Output Short-Circuit Duration (Note 2)                    | Indefinite    |

| Operating Temperature Range (Note 3).                     | 40°C to 85°C  |

| Specified Temperature Range (Note 4)                      | –40°C to 85°C |

|                                                           |               |

| Junction Temperature               |               |

|------------------------------------|---------------|

| SSOP                               | 150°C         |

| DFN                                | 125°C         |

| Storage Temperature Range          |               |

| SSOP                               | 65°C to 150°C |

| DFN                                | 65°C to 125°C |

| Lead Temperature (Soldering, 10 se | ec)           |

| SSOP                               | 300°C         |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = 5V$ , $R_L = 150\Omega$ to $V_S/2$ , $V_{\overline{EN}} = 0.4V$ , $R_{BCV} = open$ , unless otherwise noted.

| SYMBOL          | PARAMETER            | CONDITIONS                                    |   | MIN        | TYP        | MAX       | UNITS    |

|-----------------|----------------------|-----------------------------------------------|---|------------|------------|-----------|----------|

| V <sub>0S</sub> | Input Offset Voltage | V <sub>IN</sub> = 2.5V                        | • |            | 12<br>15   | 45<br>55  | mV<br>mV |

| I <sub>IN</sub> | Input Current        | V <sub>IN</sub> = 2.5V                        | • |            | 35<br>45   | 70<br>100 | μΑ<br>μΑ |

| R <sub>IN</sub> | Input Resistance     | V <sub>IN</sub> = 2V to 3V, BCV (Pin 16) Open | • | 200<br>150 | 450<br>400 |           | kΩ<br>kΩ |

| C <sub>IN</sub> | Input Capacitance    | f = 1MHz                                      |   |            | 1.4        |           | pF       |

www.DataSheet4U.com

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_S = 5V$ , $R_L = 150\Omega$ to $V_S/2$ , $V_{\overline{EN}} = 0.4V$ , $R_{BCV} = open$ , unless otherwise noted.

| SYMBOL                            | PARAMETER                         | CONDITIONS                                                                     |   | MIN          | TYP            | MAX          | UNITS    |

|-----------------------------------|-----------------------------------|--------------------------------------------------------------------------------|---|--------------|----------------|--------------|----------|

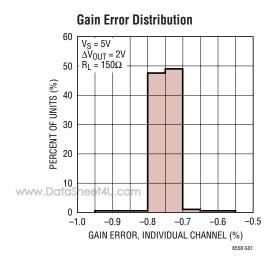

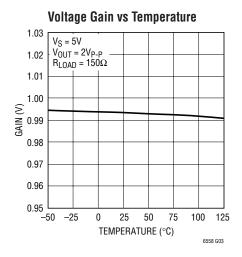

| A <sub>V</sub> ERR                | Gain Error                        | V <sub>IN</sub> = 1.5V to 3.5V                                                 | • |              | ±0.7<br>±0.9   | ±2.0<br>±2.5 | %<br>%   |

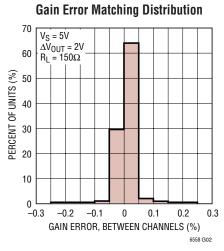

| A <sub>V</sub> MATCH              | Gain Match Between Channels       | V <sub>IN</sub> = 1.5V to 3.5V                                                 | • |              | ±0.02<br>±0.05 | ±1.5<br>±2.5 | %<br>%   |

| V <sub>IN(DC)</sub>               | Input Voltage Bias                | $R_{BCV} = 158\Omega$                                                          | • | 2.0<br>1.5   | 2.5<br>2.8     | 3<br>3.5     | V        |

| PSRR                              | Power Supply Rejection Ratio      | V <sub>S</sub> = 4V to 6V, V <sub>IN</sub> = 1.25V                             | • | 42<br>38     | 50<br>47       |              | dB<br>dB |

| V <sub>OL</sub><br>vww.DataSheet4 | Output Voltage Swing Low<br>U.com |                                                                                | • |              | 0.8<br>0.9     | 0.9<br>1.0   | V        |

| V <sub>OH</sub>                   | Output Voltage Swing High         |                                                                                | • | 4.1<br>4.0   | 4.2<br>4.1     |              | V        |

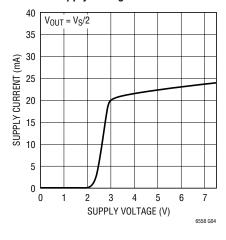

| I <sub>S</sub>                    | Supply Current per Amplifier      | $V_{\overline{EN}} = 0.4V$ , $R_L = \infty$ , Includes $I_S$ of $V^+$ (Pin 15) | • |              | 22.5<br>25.0   | 24<br>28     | mA<br>mA |

|                                   | Total Supply Current (Disabled)   | $V_{\overline{EN}} = Open, R_L = \infty$                                       | • |              | 10<br>10       | 450<br>1000  | μA<br>μA |

| I <sub>EN</sub>                   | Enable Pin Current                | $V_{\overline{EN}} = 0.4V$                                                     | • | -250<br>-300 | -125<br>-150   |              | μA<br>μA |

| I <sub>SC</sub>                   | Short-Circuit Current             |                                                                                | • | ±60<br>±40   | ±90<br>±80     |              | mA<br>mA |

| SR                                | Slew Rate                         | V <sub>OUT</sub> = 1.25V to 3.75V (Note 5)                                     |   | 1200         | 2200           |              | V/µs     |

| -3dB BW                           | -3dB Bandwidth                    | $V_{OUT} = 2V_{P-P}$                                                           |   |              | 400            |              | MHz      |

|                                   |                                   | $V_{OUT} = 0.2V_{P-P}$                                                         |   |              | 550            |              | MHz      |

| 0.1dB BW                          | Gain Flatness ±0.1dB Bandwidth    | $V_{OUT} = 2V_{P-P}$                                                           |   |              | 100            |              | MHz      |

| FPBW                              | Full Power Bandwidth              | V <sub>OUT</sub> = 2V <sub>P-P</sub> (Note 6)                                  |   | 190          | 350            |              | MHz      |

| XTalk                             | All Hostile Crosstalk             | $f = 10MHz$ , $V_{OUT} = 2V_{P-P}$<br>$f = 100MHz$ , $V_{OUT} = 2V_{P-P}$      |   |              | -80<br>-55     |              | dB<br>dB |

| $t_S$                             | Settling Time                     | To 1%, V <sub>OUT</sub> = 1.5V to 3.5V<br>To 0.1%                              |   |              | 4<br>7         |              | ns<br>ns |

| t <sub>r</sub> , t <sub>f</sub>   | Rise Time, Fall Time              | 10% to 90%, V <sub>OUT</sub> = 1.5V to 3.5V                                    |   |              | 875            |              | ps       |

| $\Delta G$                        | Differential Gain                 | NTSC Signal                                                                    |   |              | 0.02           |              | %        |

| $\Delta\Phi$                      | Differential Phase                | NTSC Signal                                                                    |   |              | 0.02           |              | Deg      |

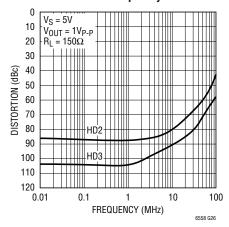

| HD2                               | 2nd Harmonic Distortion           | f = 10MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub>                                |   |              | -75            |              | dBc      |

| HD3                               | 3rd Harmonic Distortion           | f = 10MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub>                                |   |              | -79            |              | dBc      |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** A heat sink may be required to keep the junction temperature below the Absolute Maximum Rating.

**Note 3:** The LT6558C is guaranteed functional over the temperature range of -40°C and 85°C.

**Note 4:** The LT6558C is guaranteed to meet specified performance from 0°C to 70°C. The LT6558C is designed, characterized and expected to

meet specified performance from -40°C to 85°C but is not tested or QA sampled at these temperatures. The LT6558I is guaranteed to meet specified performance from -40°C to 85°C.

**Note 5:** Slew rate is 100% production tested on the R channel and measured on the rising edge of the output signal. The slew rate of the falling edge and of the G and B channels is guaranteed through design and characterization.

$\textbf{Note 6:} \ Large-signal \ bandwidth \ is \ calculated \ from \ slew \ rate:$

$FPBW = SR/(\pi \bullet V_{P-P})$

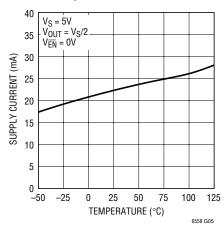

# Supply Current per Amplifier vs Temperature

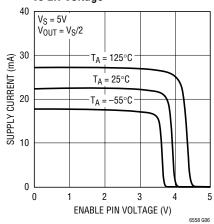

Supply Current per Amplifier vs EN Voltage

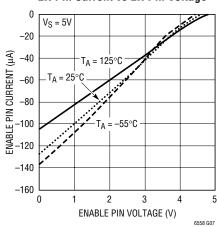

**EN** Pin Current vs **EN** Pin Voltage

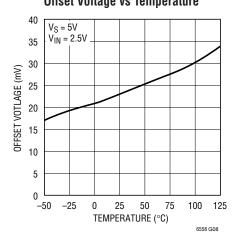

Offset Voltage vs Temperature

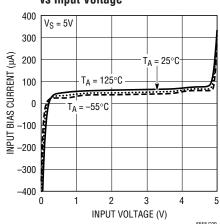

Input Bias Current vs Input Voltage

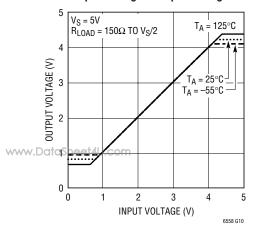

#### **Output Voltage vs Input Voltage**

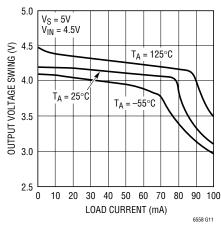

# Output Voltage Swing vs Load Current (Output High)

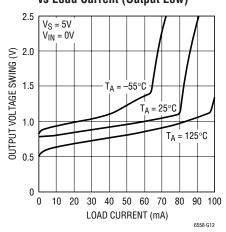

# Output Voltage Swing vs Load Current (Output Low)

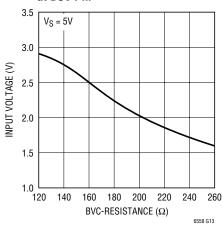

# Input Bias Voltage vs Resistance at BCV Pin

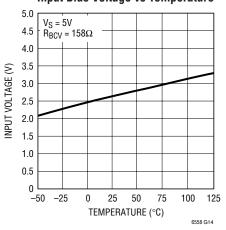

#### Input Bias Voltage vs Temperature

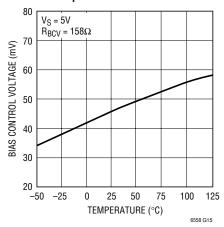

# Bias Control Voltage vs Temperature

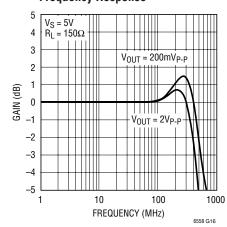

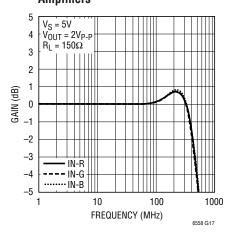

#### Frequency Response

# Frequency Response of Three Amplifiers

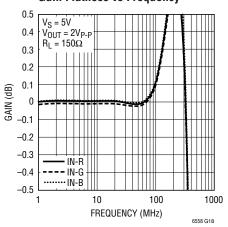

#### **Gain Flatness vs Frequency**

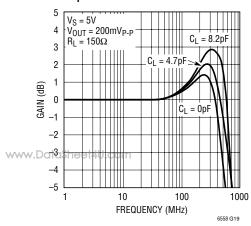

#### Frequency Response with Capacitive Loads

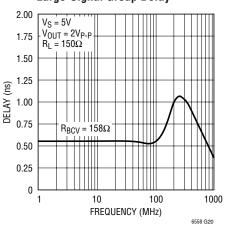

#### Large-Signal Group Delay

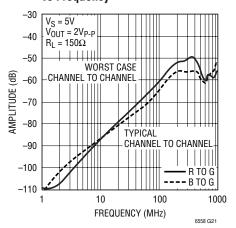

# Crosstalk Between Amplifiers vs Frequency

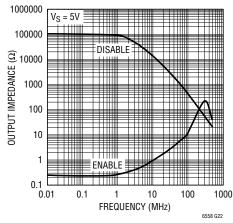

#### **Output Impedance vs Frequency**

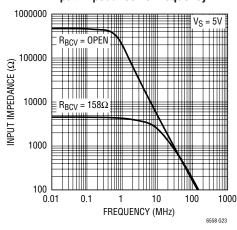

#### Input Impedance vs Frequency

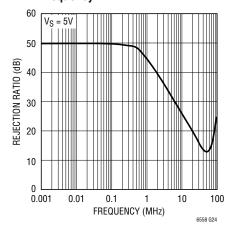

#### Power Supply Rejection Ratio vs Frequency

#### **Distortion vs Frequency**

#### **Distortion vs Frequency**

### PIN FUNCTIONS

**EN** (**Pin 1**): Enable Control Pin. The part is enabled when this pin is pulled low. An internal pull-up resistor of 40k will turn the part off if this pin is unconnected.

**GND (Pin 2):** Ground Reference for Enable Pin (Pin 1) and Bias Control Voltage Pin (Pin 16). This pin must be connected externally to ground.

**IN R (Pin 3):** Red Channel Input. This pin has a nominal impedance of  $450k\Omega$  with input bias circuit inactive, Pin 16 open.

**GND R (Pin 4):** Ground of Red Channel Amplifier. This pin is not internally connected to other ground pins and must be connected externally to ground.

**IN G (Pin 5):** Green Channel Input. This pin has a nominal impedance of  $450k\Omega$  with input bias circuit inactive, Pin 16 open.

**GND G (Pin 6):** Ground of Green Channel Amplifier. This pin is not internally connected to other ground pins and must be connected externally to ground.

**IN B (Pin 7):** Blue Channel Input. This pin has a nominal impedance of  $450k\Omega$  with input bias circuit inactive, Pin 16 open.

**GND B (Pin 8):** Ground of Blue Channel Amplifier. This pin is not internally connected to other ground pins and must be connected externally to ground.

### PIN FUNCTIONS

**V<sup>+</sup> B (Pin 9):** Positive Supply Voltage of Blue Channel Amplifier. This pin is not internally connected to other supply voltage pins and must be externally connected to the supply voltage bus with proper bypassing. For best performance, see Power Supply Considerations.

OUT B (Pin 10): Blue Channel Output.

**V**<sup>+</sup> **G** (**Pin 11**): Positive Supply Voltage of Green Channel Amplifier. This pin is not internally connected to other supply voltage pins and must be externally connected to the supply voltage bus with proper bypassing. For best performance, see Power Supply Considerations.

OUT G (Pin 12): Green Channel Output.

V<sup>+</sup> R (Pin 13): Positive Supply Voltage of Red Channel Amplifier. This pin is not internally connected to other supply voltage pins and must be externally connected to the supply voltage bus with proper bypassing. For best performance, see Power Supply Considerations.

OUT R (Pin 14): Red Channel Output.

**V**<sup>+</sup> (**Pin 15**): Positive Supply Voltage of Control Circuitry. This pin is not internally connected to other supply voltage pins and must be externally connected to supply voltage bus with proper bypassing. For best performance, see Power Supply Considerations.

**BCV (Pin 16):** Bias Control Voltage. A resistor connected between Pin 16 and Pin 2 (GND) will generate a DC voltage bias at the inputs of the three amplifiers for AC coupling application, see Programmable Input Bias.

**Exposed Pad (Pin 17, DFN Package):** Ground. This pad must be soldered to PCB and is internally connected to GND (Pin 2).

### APPLICATIONS INFORMATION

### **Power Supply Considerations**

The LT6558 is optimized to provide full video signal swing output when operated from a standard 5V single supply. Due to the supply current involved in ultrahigh slew rate amplifiers like the LT6558, selection of the lowest workable supply voltage is recommended to minimize heat generation and simplify thermal management. Temperature rise at the internal devices  $(T_J)$  must be kept below 150°C (SSOP package) or 125°C (DFN package), and can be estimated from the ambient temperature  $(T_A)$  and power dissipation  $(P_D)$  as follows:

$$T_J = T_A + P_D \cdot 40^{\circ}$$

C/W for DFN package

or

$$T_J = T_A + P_D \cdot 110^{\circ} \text{C/W}$$

for SSOP package

where

$$P_D = (I_S + 0.5 \bullet I_0) \bullet V_{S(TOTAL)}$$

The latter equation assumes (conservatively) that the output swing is small relative to the supply and RMS load current  $(I_0)$  is bidirectional (as with AC coupling).

The grounds are separately pinned for each amplifier to minimize crosstalk.

Operation from split supplies can be accomplished by connecting the LT6558 ground pins to the negative rail. With dual supplies, recommended voltages range from nominal ±2.5V to ±3.3V.

The ultrahigh frequency (UHF) operating range of the LT6558 requires that careful printed circuit layout practices be followed to obtain maximum performance. Trace lengths between power pins and bypass capacitors should be minimized (<0.1 inch) and one or more dedicated ground planes should be employed to minimize parasitic inductance. Poor layout or breadboarding methods can seriously impact amplifier stability, frequency response and crosstalk performance. A 2.2 $\mu$ F and a 10 $\mu$ F bypass capacitor is recommended for the LT6558 supply bus, plus a 10 $\mu$ F high frequency bypass capacitor at each individual power pin.

www.DataSheet4U.com

### **APPLICATIONS INFORMATION**

#### **Programmable Input Bias**

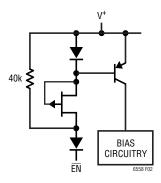

The LT6558 contains circuitry that provides a user-programmed bias voltage to the inputs of all three amplifier sections. The internal biasing feature is designed to minimize external component count in AC-coupled applications, but may be defeated if external biasing is desired. Figure 1 shows the simplified equivalent circuit feeding the noninverting input of each amplifier. A programming resistor from Pin 16 to GND (Pin 2) establishes the nominal

www.DataSheet4U.com  $I = \frac{V_{PIN16}}{R_{SET}}$  9.1k

Figure 1. Simplified Programmable Input Bias Circuit Diagram

Figure 2. Simplified Shutdown Circuit Diagram

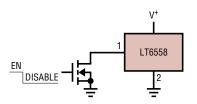

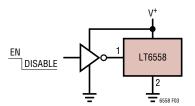

(3a) Open Drain or Open Collector

no-signal amplifier input bias condition according to the following relationship:

$$V_{BIAS(IN)} = \frac{V_{PIN16} \bullet 9.1k}{R_{SET}}$$

where  $V_{PIN16} = 0.044V$  typical.

For single 5V supply operation, a  $158\Omega$  programming resistor is generally optimal. In applications that demand maximum amplifier linearity, or if external biasing is preferred (in DC-coupled applications, for example), the internal biasing circuitry may be disabled by leaving Pin 16 open. With BCV (Pin 16) open, input loading is approximately  $450k\Omega$ .

#### **Shutdown Control**

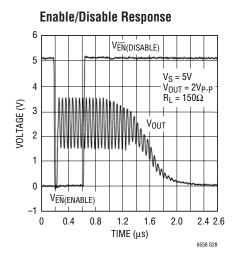

The LT6558 may be placed into a shutdown mode, where all three amplifier sections are deactivated and power supply draw is reduced to approximately  $10\mu A$ . When the EN pin is left open, an internal 40k pull-up resistor brings the pin to V<sup>+</sup> and the part enters the shutdown mode. Pulling the pin more than approximately 1.5V below V<sup>+</sup> will enable the LT6558 (see Figure 2 for equivalent circuit). The pull-down current required to activate the part is typically  $125\mu A$ . In most applications, the EN pin is simply connected to ground (for continuous operation) or driven directly by a CMOS-level logic gate (see Figure 3 for examples). Response time is typically 50ns for enabling, and  $1\mu s$  for shutdown. In shutdown mode, the feedback resistors remain connected between the output pins and the individual ground (or V<sup>-</sup> connected) pins.

(3b) CMOS Gate with Shared Supply

Figure 3. Suitable Shutdown Pin Drive Circuits

www.DataSheet4tr.com

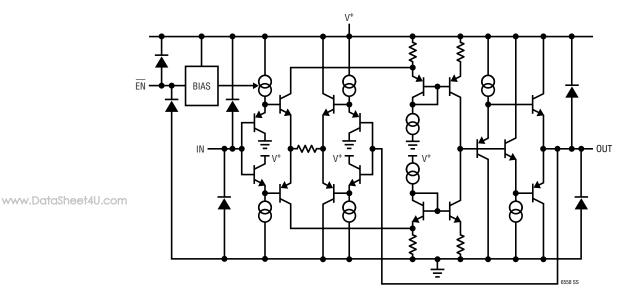

# SIMPLIFIED SCHEMATIC (Single Amplifier Section)

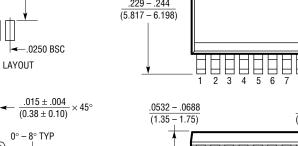

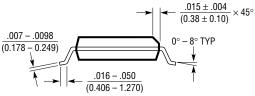

# PACKAGE DESCRIPTION

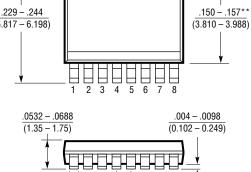

#### **GN Package** 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

.008 - .012

(0.203 - 0.305)

- 1. CONTROLLING DIMENSION: INCHES

- 2. DIMENSIONS ARE IN  $\frac{\text{INCHES}}{\text{(MILLIMETERS)}}$

- 3. DRAWING NOT TO SCALE

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

.0250

(0.635)

.189 - .196\*

$\overline{(4.801 - 4.978)}$

15 14 13 12 11 10 9

.009 (0.229)

REF

T GN16 (SSOP) 0204

www.DataSheet4U.com

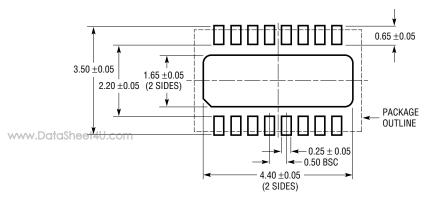

# PACKAGE DESCRIPTION

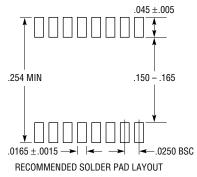

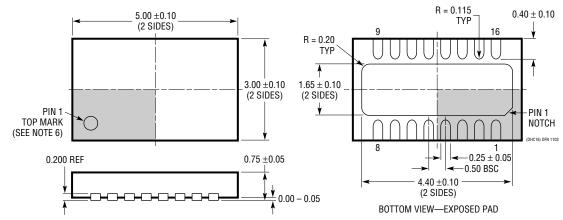

# $\begin{array}{c} \textbf{DHC Package} \\ \textbf{16-Lead Plastic DFN (5mm} \times \textbf{3mm)} \end{array}$

(Reference LTC DWG # 05-08-1706)

#### **RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WJED-1) IN JEDEC PACKAGE OUTLINE MO-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

#### **DC-Coupled Split Supply Operation**

www.DataSheet4U.com

# **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                               | COMMENTS                                                                   |  |

|---------------|-------------------------------------------|----------------------------------------------------------------------------|--|

| LT1399        | 300MHz Triple Current Feedback Amplifier  | 0.1dB Gain Flatness to 150MHz, Shutdown                                    |  |

| LT1675        | 250MHz Triple RGB Multiplexer             | 100MHz Pixel Switching, 1100V/µs Slew Rate, 16-Lead SSOP                   |  |

| LT6550/LT6551 | 3.3V Triple and Quad Video Buffers        | 110MHz Gain of 2 Buffers in MS Package                                     |  |

| LT6553        | 650MHz Gain of 2 Triple Video Amplifier   | Optimized for Driving $75\Omega$ Cables                                    |  |

| LT6554        | 650MHz Gain of 1 Triple Video Amplifier   | Performance Similar to the LT6553 with A <sub>V</sub> = 1, 16-Lead SSOP    |  |

| LT6555        | 650MHz Gain of 2 Triple Video Multiplexer | Optimized for Driving 75Ω Cables                                           |  |

| LT6556        | 750MHz Gain of 1 Triple Video Multiplexer | High Slew Rate 2100V/μs                                                    |  |

| LT6557        | 500MHz, Gain of 2 Triple Video Amplifier  | Optimized for Single 5V Supply Driving 75Ω Cables, High Slew Rate 2200V/μ: |  |

| LT6559        | Low Cost, 300MHz, Triple Video Amplifier  | 3mm × 3mm QFN Package                                                      |  |