## ARM946E-S

Revision: r1p1

### **Technical Reference Manual**

#### ARM946E-S

#### **Technical Reference Manual**

Copyright © 2001-2003 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

#### Change history

| Date             | Issue | Change         |

|------------------|-------|----------------|

| 16 February 2001 | A     | First release  |

| 17 May 2002      | В     | Second release |

| 15 May 2003      | С     | Third release  |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents **ARM946E-S Technical Reference Manual**

|           | Preta | ace                                    |       |

|-----------|-------|----------------------------------------|-------|

|           |       | About this document                    | . xiv |

|           |       | Feedback                               | . xix |

| Chapter 1 | Intro | duction                                |       |

|           | 1.1   | About the ARM946E-S processor          | 1-2   |

|           | 1.2   | ARM946E-S block diagram                |       |

| 5         | 1.3   | Differences between processor versions |       |

| Chapter 2 | Prog  | rammer's Model                         |       |

|           | 2.1   | About the ARM946E-S programmer's model | 2-2   |

|           | 2.2   | About the ARM9E-S programmer's model   | 2-3   |

|           | 2.3   | CP15 register map summary              | 2-4   |

| Chapter 3 | Cach  | nes                                    |       |

|           | 3.1   | About cache architecture               | 3-2   |

|           | 3.2   | Instruction cache                      | 3-6   |

|           | 3.3   | Data cache                             | 3-8   |

|           | 3.4   | Cache lockdown                         |       |

| Chapter 4 | Prote | ection Unit                            |       |

|           | 4.1   | About the protection unit              | 4-2   |

|           |       |                                        |       |

|             | 4.2<br>4.3 | Memory regions  Overlapping regions            |      |

|-------------|------------|------------------------------------------------|------|

|             | 1.0        | Cronapping regions                             |      |

| Chapter 5   | Tight      | tly-Coupled Memory Interface                   |      |

|             | 5.1        | ARM946E-S TCM interface description            | 5-2  |

|             | 5.2        | Using CP15 Control Register                    | 5-3  |

|             | 5.3        | Enabling the Instruction TCM during soft reset |      |

|             | 5.4        | Data TCM accesses                              | 5-8  |

|             | 5.5        | Instruction TCM accesses                       | 5-9  |

| Chapter 6   | Bus        | Interface Unit and Write Buffer                |      |

|             | 6.1        | About the BIU and write buffer                 | 6-2  |

|             | 6.2        | AHB bus master interface                       | 6-3  |

|             | 6.3        | Noncached Thumb instruction fetches            | 6-10 |

|             | 6.4        | AHB clocking                                   | 6-11 |

|             | 6.5        | The write buffer                               |      |

| Chapter 7   | Copr       | rocessor Interface                             |      |

| •           | 7.1        | About the coprocessor interface                | 7-2  |

|             | 7.2        | Coprocessor interface signals                  |      |

|             | 7.3        | LDC/STC                                        |      |

|             | 7.4        | MCR/MRC                                        | 7-13 |

|             | 7.5        | Interlocked MCR                                | 7-14 |

|             | 7.6        | CDP                                            |      |

|             | 7.7        | Privileged instructions                        | 7-16 |

|             | 7.8        | Busy-waiting and interrupts                    | 7-17 |

| Ob austau 0 |            | Interfere                                      |      |

| Chapter 8   |            | Interface                                      | 0.0  |

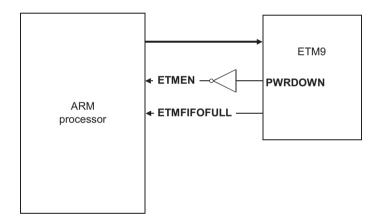

|             | 8.1        | About the ETM interface                        |      |

|             | 8.2        | Enabling the ETM interface                     |      |

|             | 8.3        | ARM946E-S trace support features               | 8-4  |

| Chapter 9   | Debu       | ug Support                                     |      |

|             | 9.1        | About the debug interface                      | 9-2  |

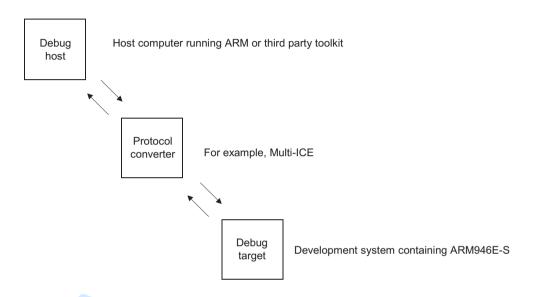

|             | 9.2        | Debug systems                                  | 9-4  |

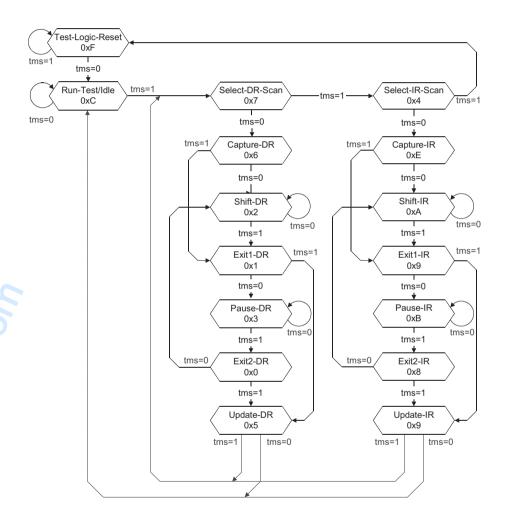

|             | 9.3        | The JTAG state machine                         | 9-7  |

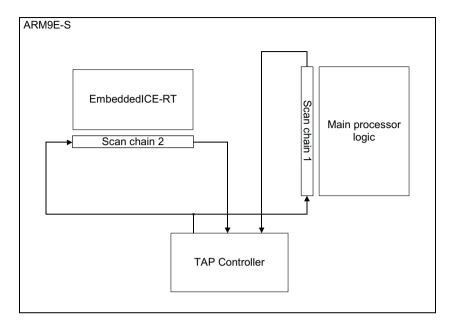

|             | 9.4        | Scan chains                                    | 9-12 |

|             | 9.5        | Debug access to the caches                     | 9-18 |

|             | 9.6        | Debug interface signals                        | 9-20 |

|             | 9.7        | Determining the core and system state          |      |

|             | 9.8        | Overview of EmbeddedICE-RT                     | 9-26 |

|             | 9.9        | Disabling EmbeddedICE-RT                       | 9-28 |

|             | 9.10       | The debug communication channel                |      |

|             | 9.11       | Monitor mode debugging                         |      |

| Chapter 10 | Test | Support                                        |      |

|------------|------|------------------------------------------------|------|

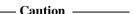

| -          | 10.1 | About the ARM946E-S processor test methodology | 10-2 |

|            | 10.2 | Scan insertion and ATPG                        |      |

|            | 10.3 | BIST of memory arrays                          | 10-5 |

| Appendix A | AC P | Parameters                                     |      |

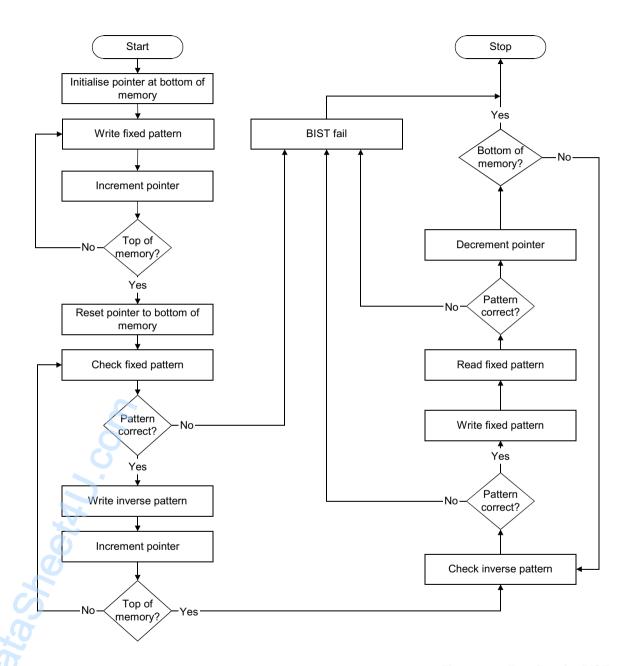

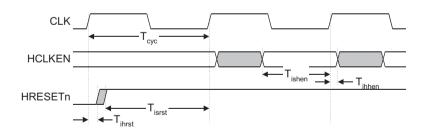

|            | A.1  | Timing diagrams                                | A-2  |

| Appendix B | Sign | al Descriptions                                |      |

|            | B.1  | Signal properties and requirements             | B-2  |

|            | B.2  | Clock interface signals                        | B-3  |

|            | B.3  | TCM interface signals                          |      |

|            | B.4  | AHB signals                                    |      |

|            | B.5  | Coprocessor interface signals                  | B-8  |

|            | B.6  | Debug signals                                  |      |

|            | B.7  | JTAG signals                                   |      |

|            | B.8  | Miscellaneous signals                          |      |

|            | B.9  | ETM interface signals                          |      |

|            | B.10 | INTEST wrapper signals                         |      |

|            |      |                                                |      |

Glossary

Contents

# List of Tables ARM946E-S Technical Reference Manual

|            | Change history                                                     | i    |

|------------|--------------------------------------------------------------------|------|

| Table 1-1  | Location of block descriptions                                     |      |

| Table 2-1  | CP15 register map                                                  | 2-5  |

| Table 2-2  | CP15 terms and abbreviations                                       | 2-6  |

| Table 2-3  | Register 0, ID code                                                | 2-8  |

| Table 2-4  | Cache Type Register format                                         |      |

| Table 2-5  | Cache size encoding                                                | 2-9  |

| Table 2-6  | Cache associativity encoding                                       | 2-10 |

| Table 2-7  | Tightly-coupled Memory Size Register                               |      |

| Table 2-8  | Memory size field                                                  | 2-11 |

| Table 2-9  | Register 1, Control Register                                       | 2-12 |

| Table 2-10 | Programming instruction and data cachable bits                     | 2-16 |

| Table 2-11 | Programming data bufferable bits                                   | 2-17 |

| Table 2-12 | Programming instruction and data access permission bits (extended) | 2-17 |

| Table 2-13 | Access permission encoding (extended)                              | 2-18 |

| Table 2-14 | Instruction and data access permission bits (standard)             | 2-19 |

| Table 2-15 | Access permission encoding (standard)                              |      |

| Table 2-16 | Accessing Protection Region Base and Size Registers                |      |

| Table 2-17 | Protection Region Base and Size Register format                    | 2-21 |

| Table 2-18 | Region size encoding                                               | 2-21 |

| Table 2-19 | Cache operations                                                   |      |

| Table 2-20 | Index fields for supported cache sizes                             |      |

| Table 2-21 | Lockdown Register format                                           | 2-26 |

|            |                                                                    |      |

#### List of Tables

| Table 2-22             | TCM Region Register format                                          | 2-27 |

|------------------------|---------------------------------------------------------------------|------|

| Table 2-23             | TCM area size encoding                                              | 2-27 |

| Table 2-24             | Register 15, BIST instructions                                      | 2-30 |

| Table 2-25             | Register 15, implementation-specific BIST instructions              |      |

| Table 2-26             | BIST Control Register bit definitions                               | 2-31 |

| Table 2-27             | BIST size encodings examples                                        |      |

| Table 2-28             | Test State Register bit assignments                                 | 2-32 |

| Table 2-29             | Additional operations                                               | 2-33 |

| Table 2-30             | Index fields for supported cache sizes                              | 2-34 |

| Table 2-31             | Trace Control Register                                              | 2-35 |

| Table 2-32             | Trace Control Register bit assignments                              | 2-36 |

| Table 3-1              | TAG and index fields for supported cache sizes                      |      |

| Table 3-2              | Meaning of Cd bit values                                            | 3-9  |

| Table 3-3              | Calculating index addresses                                         |      |

| Table 4-1              | Protection Register format                                          | 4-3  |

| Table 4-2              | Region size encoding                                                | 4-4  |

| Table 6-1              | AHB transfer types                                                  | 6-4  |

| Table 6-2              | Supported burst types                                               | 6-5  |

| Table 6-3              | Data write modes                                                    | 6-14 |

| Table 7-1              | Coprocessor interface signals                                       |      |

| Table 7-2              | Handshake encoding                                                  | 7-7  |

| Table 9-1              | Public instructions                                                 |      |

| Table 9-2              | ARM946E-S scan chain allocations                                    | 9-12 |

| Table 9-3              | Scan chain 1 bits                                                   |      |

| Table 9-4              | Scan chain 2 bits                                                   |      |

| Table 9-5              | Scan chain 15 bits                                                  |      |

| Table 9-6              | Mapping of scan chain 15 address field to CP15 registers            |      |

| Table 9-7              | Status bit mapping of scan chain 15 address field to CP15 registers |      |

| Table 9-8              | Correlation between status bits and cache operations                |      |

| Table 9-9              | Coprocessor 14 register map                                         |      |

| Table 10-1             | Instruction BIST Address and General Registers                      |      |

| Table 10-2             | Data BIST Address and General Registers                             |      |

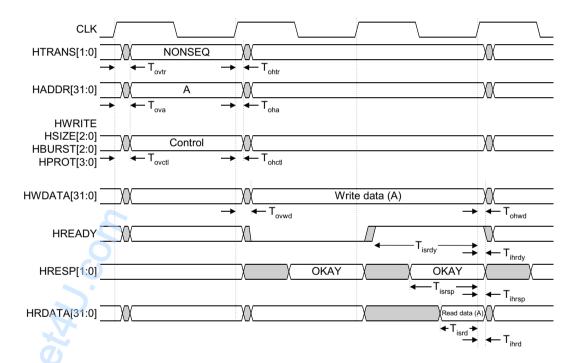

| Table A-1              | Timing parameter definitions for clock, reset, and AHB enable       |      |

| Table A-2              | Parameter definitions for AHB bus request and grant timing          |      |

| Table A-3              | Parameter definitions for AHB bus master timing                     |      |

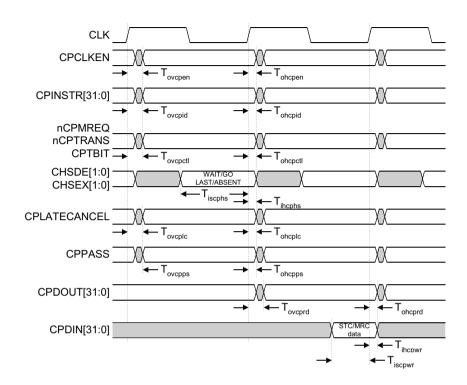

| Table A-4              | Parameter definitions for coprocessor interface timing              |      |

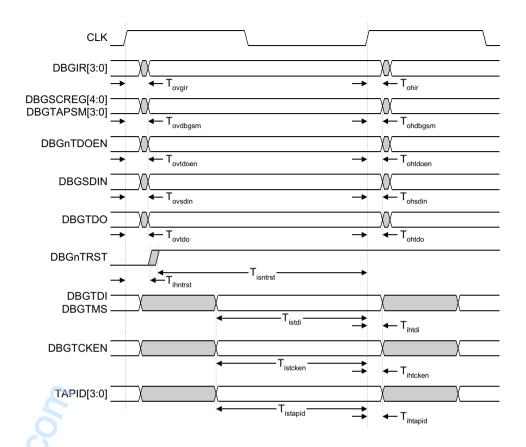

| Table A-5              | Parameter definitions for debug interface timing                    |      |

| Table A-6              | Parameter definitions for JTAG interface timing                     |      |

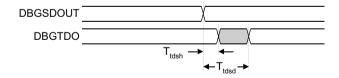

| Table A-7              | Parameter definitions for DBGSDOUT to DBGTDO timing                 |      |

| Table A-8              | Parameter definitions for exception and configuration timing        |      |

| Table A-9              | Parameter definitions for TCM interface timing                      |      |

| Table A-10             | Parameter definitions for ETM interface timing                      |      |

| Table B-1              | Clock interface signals                                             |      |

| Table B-2              | TCM interface signals                                               |      |

| Table B-3              | AHB signals                                                         |      |

| Table B-4<br>Table B-5 | Coprocessor interface signals  Debug signals                        |      |

| I aule D-3             | nennd aidiigia                                                      | D-10 |

| Table B-6 | JTAG signals          | B-1 | 12 |

|-----------|-----------------------|-----|----|

| Table B-7 | Miscellaneous signals | B-1 | 13 |

| Table B-8 | FTM interface signals | R-1 | 14 |

List of Tables

# List of Figures **ARM946E-S Technical Reference Manual**

|            | Key to timing diagram conventions                                   | xvi  |

|------------|---------------------------------------------------------------------|------|

| Figure 1-1 | ARM946E-S block diagram                                             |      |

| Figure 2-1 | CP15 MRC and MCR bit pattern                                        |      |

| Figure 2-2 | Register 7, Index and segment format                                |      |

| Figure 2-3 | Instruction cache address format                                    |      |

| Figure 2-4 | Process ID format                                                   |      |

| Figure 2-5 | Register 15, Index and segment format                               |      |

| Figure 2-6 | Data format TAG read/write operations                               |      |

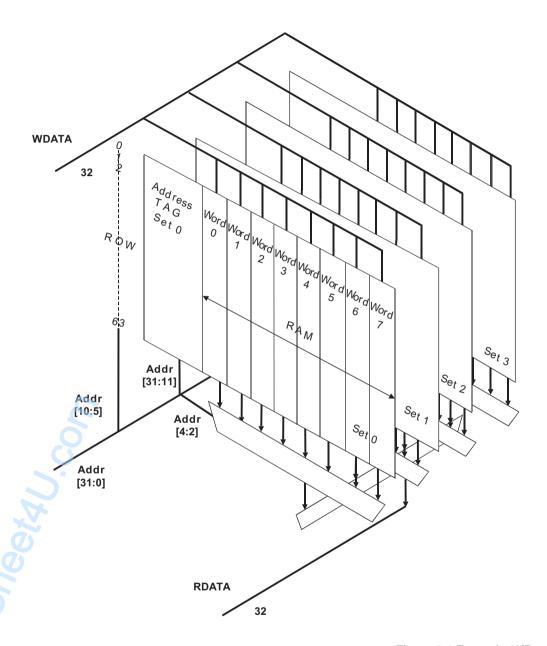

| Figure 3-1 | Example 8KB cache                                                   |      |

| Figure 3-2 | Access address for a 4KB cache                                      |      |

| Figure 3-3 | Register 7, Rd format                                               | 3-10 |

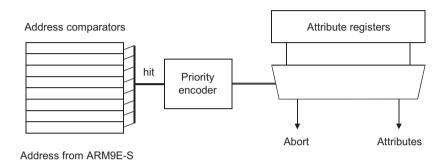

| Figure 4-1 | Protection unit                                                     | 4-2  |

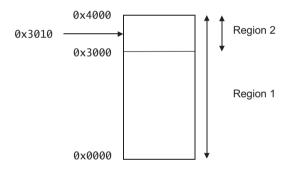

| Figure 4-2 | Overlapping memory regions                                          | 4-6  |

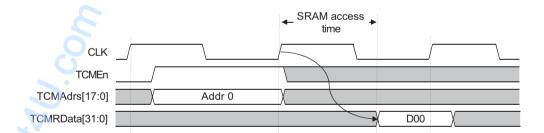

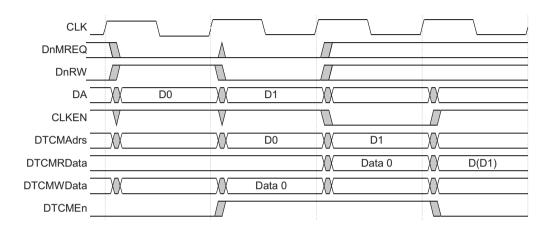

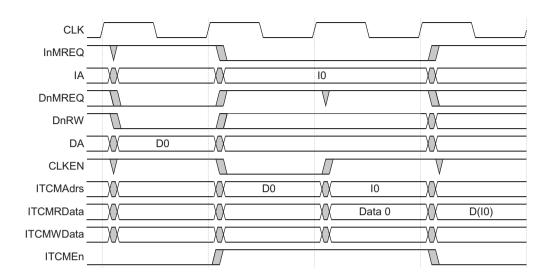

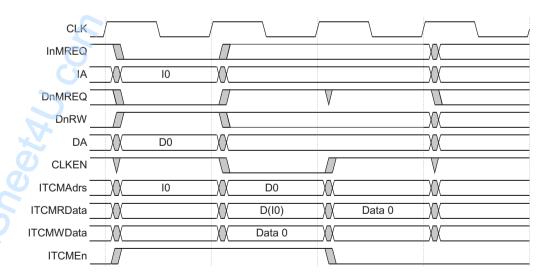

| Figure 5-1 | TCM read cycle                                                      | 5-2  |

| Figure 5-2 | Data write followed by data read of Data TCM                        | 5-8  |

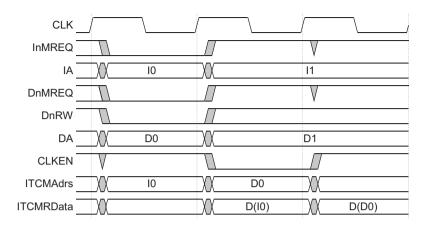

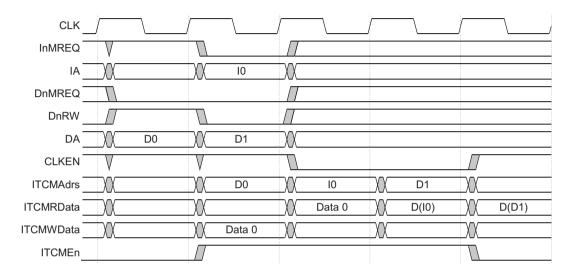

| Figure 5-3 | Simultaneous instruction fetch and data read of Instruction TCM     | 5-10 |

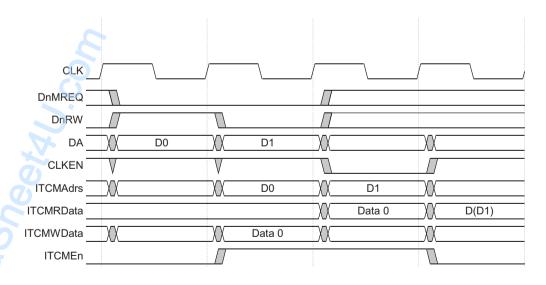

| Figure 5-4 | Data write followed by data read of Instruction TCM                 | 5-10 |

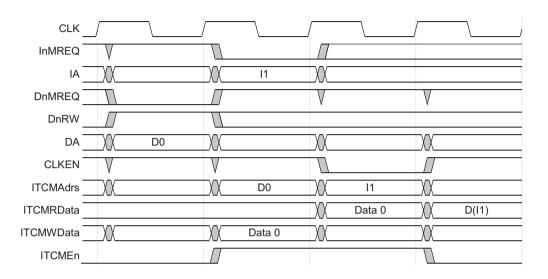

| Figure 5-5 | Data write followed by instruction fetch of Instruction TCM         |      |

| Figure 5-6 | Data read followed by instruction fetch                             |      |

| Figure 5-7 | Simultaneous instruction fetch and data write                       | 5-12 |

| Figure 5-8 | Data write followed by simultaneous instruction fetch and data read | 5-13 |

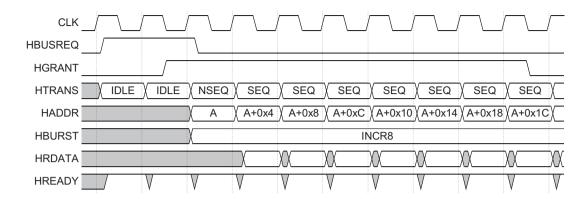

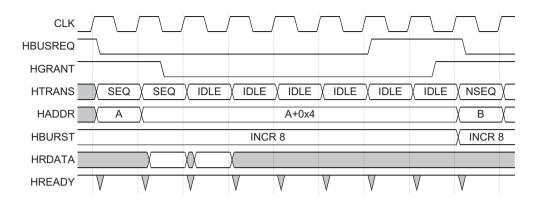

| Figure 6-1 | Linefetch transfer                                                  |      |

| Figure 6-2 | Back-to-back line fetches                                           |      |

| -          |                                                                     |      |

#### List of Figures

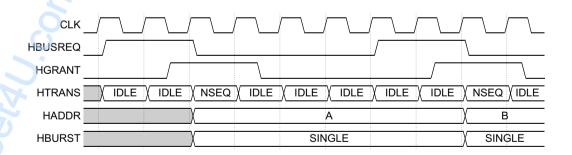

| Figure 6-3  | Nonsequential uncached accesses                   | 6-7  |

|-------------|---------------------------------------------------|------|

| Figure 6-4  | Data burst followed by instruction fetch          | 6-8  |

| Figure 6-5  | Crossing a 1KB boundary                           | 6-8  |

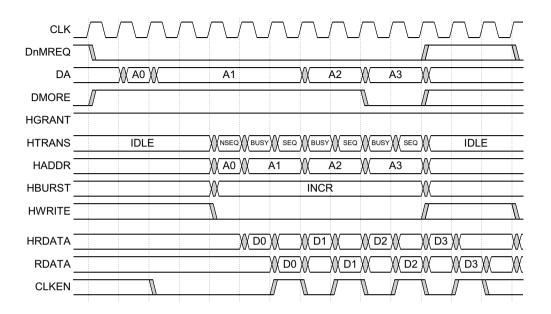

| Figure 6-6  | Uncached LDC sequence                             | 6-9  |

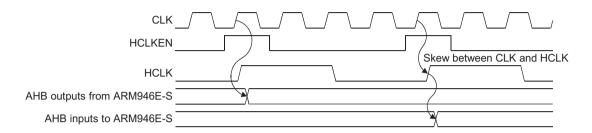

| Figure 6-7  | AHB clock relationships                           | 6-12 |

| Figure 6-8  | ARM946E-S CLK to AHB HCLK sampling                | 6-13 |

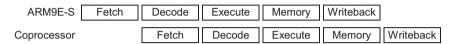

| Figure 7-1  | Pipeline stages                                   | 7-2  |

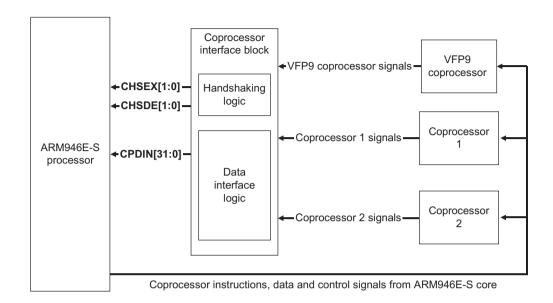

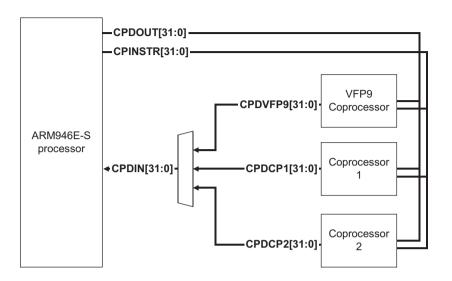

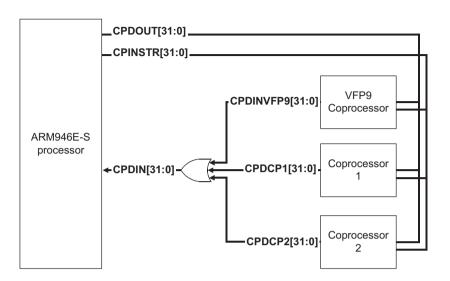

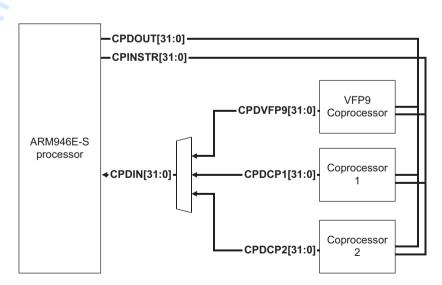

| Figure 7-2  | Connecting multiple coprocessors                  | 7-8  |

| Figure 7-3  | Example handshake logic blocks                    | 7-9  |

| Figure 7-4  | Driving the coprocessors data buses to logic 0    | 7-10 |

| Figure 7-5  | Multiplexing the coprocessors data buses          | 7-10 |

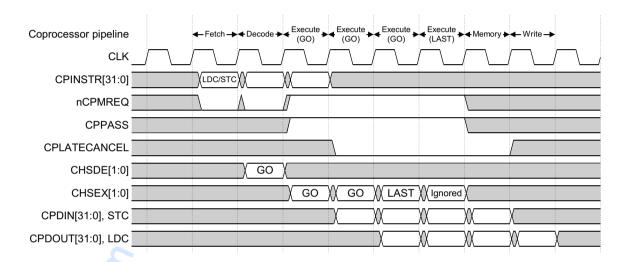

| Figure 7-6  | LDC/STC cycle timing                              |      |

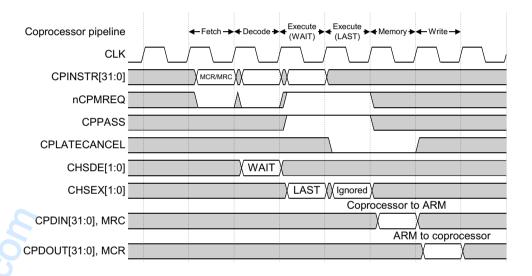

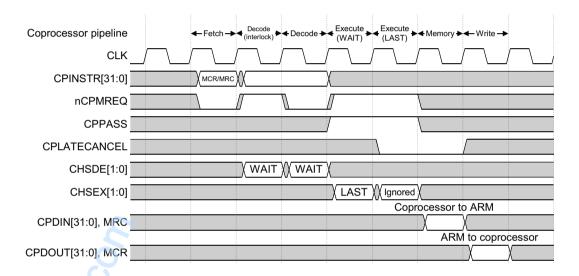

| Figure 7-7  | MCR/MRC transfer timing with busy-wait            | 7-13 |

| Figure 7-8  | Interlocked MCR/MRC timing with busy-wait         | 7-14 |

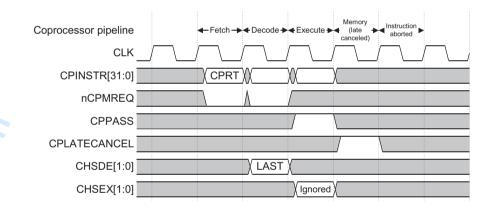

| Figure 7-9  | Late canceled CDP                                 |      |

| Figure 7-10 | Privileged instructions                           | 7-16 |

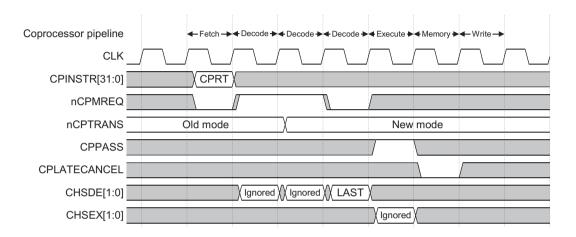

| Figure 7-11 | Busy-waiting and interrupts                       | 7-17 |

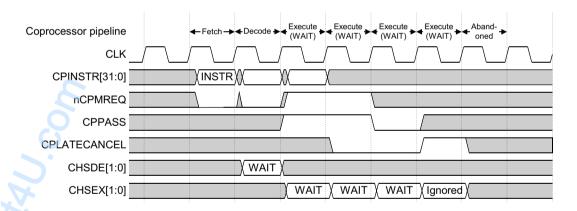

| Figure 8-1  | ARM946E-S ETM interface                           | 8-2  |

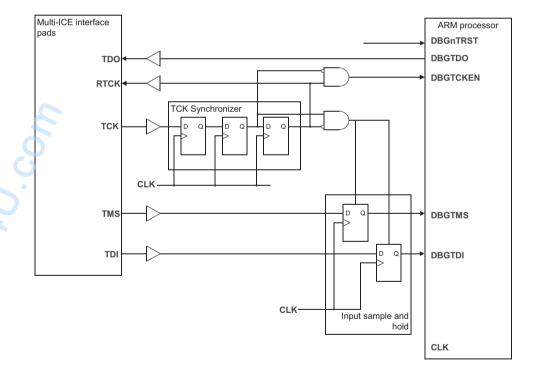

| Figure 9-1  | Clock synchronization                             | 9-3  |

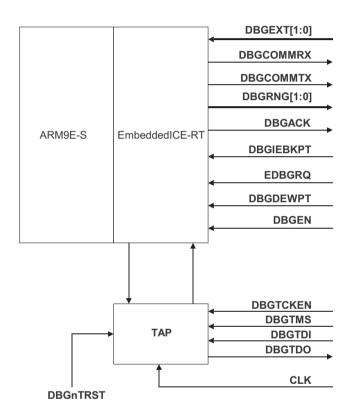

| Figure 9-2  | Typical debug system                              | 9-4  |

| Figure 9-3  | ARM9E-S block diagram                             | 9-6  |

| Figure 9-4  | TAP controller state transitions                  | 9-7  |

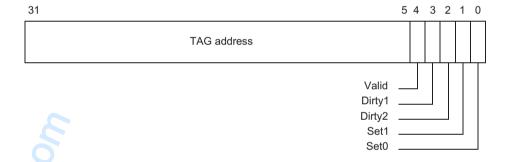

| Figure 9-5  | TAG address format                                | 9-18 |

| Figure 9-6  | Cache Index Register format                       | 9-19 |

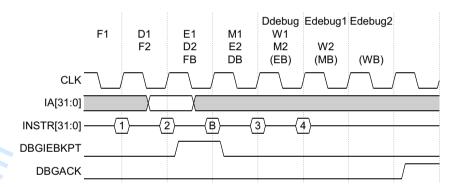

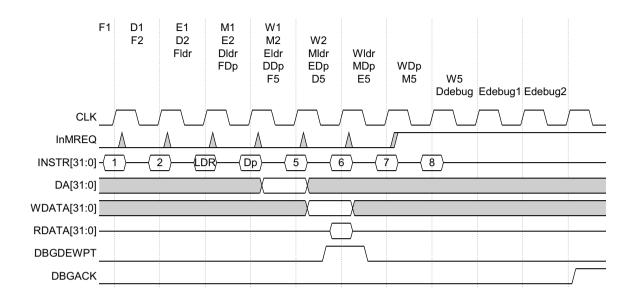

| Figure 9-7  | Breakpoint timing                                 |      |

| Figure 9-8  | Watchpoint entry with data processing instruction | 9-22 |

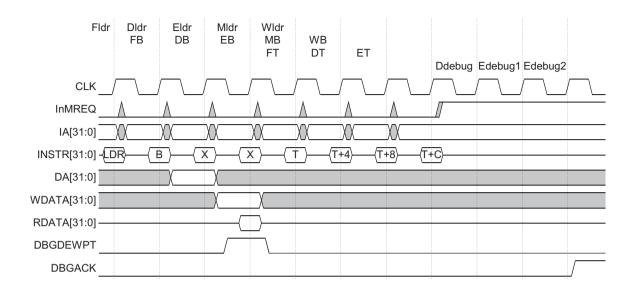

| Figure 9-9  | Watchpoint entry with branch                      |      |

| Figure 9-10 | The ARM9E-S, TAP controller, and EmbeddedICE-RT   |      |

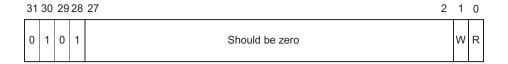

| Figure 9-11 | Debug Communication Channel Status Register       | 9-30 |

| Figure 10-1 | Test flow for BIST                                |      |

| Figure A-1  | Clock, reset, and AHB enable timing               | A-2  |

| Figure A-2  | AHB bus request and grant related timing          | A-3  |

| Figure A-3  | AHB bus master timing                             | A-4  |

| Figure A-4  | Coprocessor interface timing                      | A-6  |

| Figure A-5  | Debug interface timing                            | A-8  |

| Figure A-6  | JTAG interface timing                             | A-10 |

| Figure A-7  | DBGSDOUT to DBGTDO timing                         | A-11 |

| Figure A-8  | Exception and configuration timing                | A-12 |

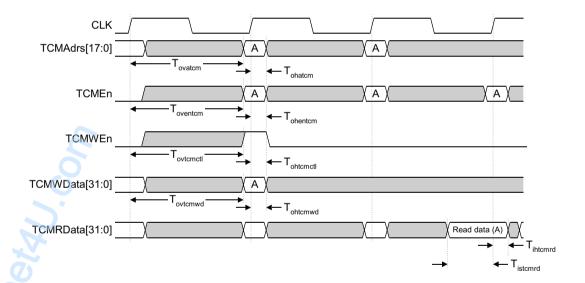

| Figure A-9  | TCM interface timing                              | A-13 |

| Figure A-10 | FTM interface timing                              | Δ-15 |

### **Preface**

This preface introduces the *ARM946E-S r1p1 Technical Reference Manual*. It contains the following sections:

- About this document on page xiv

- Feedback on page xix.

#### About this document

This document is a reference manual for the ARM946E-S processor.

#### Intended audience

This document has been written for hardware and software engineers who want to design or develop products based on the ARM946E-S processor. It assumes no prior knowledge of ARM products.

#### Using this manual

This document is organized into the following chapters:

#### Chapter 1 Introduction

This chapter provides an introduction to the ARM946E-S processor.

#### Chapter 2 Programmer's Model

This chapter describes the programmer's model of the ARM946E-S processor and includes a summary of the ARM946E-S coprocessor registers.

#### Chapter 3 Caches

This chapter describes the ARM946E-S cache implementation.

#### Chapter 4 Protection Unit

This chapter describes the ARM946E-S memory protection unit.

#### Chapter 5 Tightly-Coupled Memory Interface

This chapter describes the requirements and operation of the *Tightly-Coupled Memory* (TCM).

#### Chapter 6 Bus Interface Unit and Write Buffer

This chapter describes the operation of the bus interface unit and write buffer.

#### Chapter 7 Coprocessor Interface

This chapter describes the coprocessor interface and the operation of common coprocessor instructions.

#### Chapter 8 ETM Interface

This chapter describes the ETM interface, including details of how to enable the interface.

#### Chapter 9 Debug Support

This chapter describes the debug support for the ARM946E-S processor and the EmbeddedICE-RT logic.

#### Chapter 10 Test Support

This chapter describes the test methodology used for the ARM946E-S synthesized logic and memory.

#### Appendix A AC Parameters

This appendix describes the timing parameters applicable to the ARM946E-S processor.

#### Appendix B Signal Descriptions

This appendix describes the signals used in the ARM946E-S processor.

#### Product revision status

The rnpn identifier indicates the revision status of the product described in this document, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Typographical conventions

The following typographical conventions are used in this document:

**bold** Highlights ARM processor signal names within text, and interface

elements such as menu names. Can also be used for emphasis in

descriptive lists where appropriate.

*italic* Highlights special terminology, cross-references and citations.

monospace Denotes text that can be entered at the keyboard, such as

commands, file names and program names, and source code.

<u>mono</u>space Denotes a permitted abbreviation for a command or option. The

underlined text can be entered instead of the full command or

option name.

monospace italic Denotes arguments to commands or functions where the argument

is to be replaced by a specific value.

monospace bold Denotes language keywords when used outside example code.

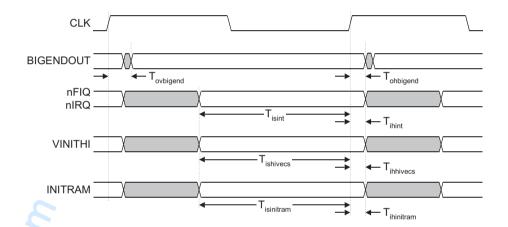

#### **Timing diagram conventions**

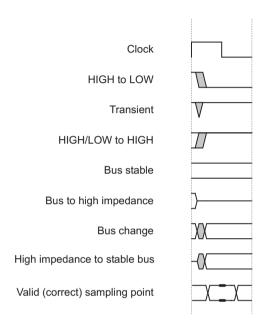

This manual contains a number of timing diagrams. The following key explains the components used in these diagrams. Any variations are clearly labeled when they occur. Therefore, no additional meaning must be attached unless specifically stated.

#### Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Other conventions

This document uses other conventions. They are described in the following sections:

- Signals on page xvii

- Bits, bytes, and word lengths on page xvii

- Numbers on page xvii

- Register fields on page xvii.

#### **Signals**

When a signal is described as being asserted, the level depends on whether the signal is active HIGH or active LOW. Asserted means HIGH for active high signals and LOW for active low signals:

**Prefix n** Active LOW signals are prefixed by a lowercase n except in the case of

AHB or APB reset signals. These are named  $\boldsymbol{HRESETn}$  and  $\boldsymbol{PRESETn}$

respectively.

**Prefix H** AHB signals are prefixed by an upper case H.

**Prefix P** APB signals are prefixed by an upper case P.

#### Bits, bytes, and word lengths

**Suffix b** Indicates bits.

**Suffix B** Indicates bytes.

Byte Eight bits.

**Halfword** Two bytes (16 bits).

Word Four bytes (32 bits).

**Quadword** 16 contiguous bytes (128 bits).

#### **Numbers**

**Suffix k** Indicates 1000.

**Suffix K** Indicates an amount of memory. It means 1024.

**Suffix M** When used to indicate an amount of memory means  $1024^2 = 1048576$ .

When used to indicate a frequency means 1000000.

**Prefix 0x** Indicates hexadecimal.

**Prefix b** Indicates binary.

#### Register fields

All reserved or unused address locations must not be accessed as this can result in unpredictable behavior of the device.

All reserved or unused bits of registers must be written as zero, and ignored on read unless otherwise stated in the relevant text.

#### Preface

All registers bits are reset to logic 0 by a system reset unless otherwise stated in the relevant text.

Unless otherwise stated in the relevant text, all registers support read and write accesses. A write updates the contents of the register and a read returns the contents of the register.

All registers defined in this document can only be accessed using word reads and word writes, unless otherwise stated in the relevant text.

#### **Further reading**

This section lists publications by ARM Limited, and by third parties.

If you would like further information on ARM products, or if you have questions not answered by this document, please contact info@arm.com or visit our web site at http://www.arm.com.

#### **ARM publications**

This document contains information that is specific to the ARM946E-S processor. You can refer to the following documents for other relevant information:

- *ARM Architecture Reference Manual* (ARM DDI 0100)

- ARM9E-S Technical Reference Manual (ARM DDI 0165)

- *AMBA Specification* (ARM IHI 0011).

#### Other publications

This section lists relevant documents published by third parties:

IEEE Std. 1149.1-1990, Standard Test Access Port and Boundary-Scan Architecture.

#### **Feedback**

ARM Limited welcomes feedback both on the ARM946E-S processor, and on the documentation.

#### Feedback on the ARM946E-S processor

If you have any comments or suggestions about this product, contact your supplier giving:

- the product name

- a concise explanation of your comments.

#### Feedback on the document

If you have any comments about this document, send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces the ARM946E-S processor. It contains the following sections:

- About the ARM946E-S processor on page 1-2

- ARM946E-S block diagram on page 1-3

- Differences between processor versions on page 1-5.

### 1.1 About the ARM946E-S processor

The ARM946E-S is a *synthesizable* processor combining an ARM9E-S<sup>™</sup> processor core with a configurable memory system. It is a member of the ARM9E<sup>™</sup> family of high-performance, 32-bit system-on-chip processor solutions.

The ARM946E-S is a Harvard architecture cached processor that provides a complete high-performance processor subsystem, including:

- An ARM9E-S RISC integer CPU core featuring:

- ARMv5TE 32-bit instruction set that has improved ARM/Thumb code interworking and an enhanced multiplier designed for improved DSP performance

- ARM debug architecture with additional support for real-time debug. This

enables critical exception handlers to execute while debugging the system.

- Support for external *Tightly-Coupled Memory* (TCM). A TCM interface is provided for each of the external instruction and data memory blocks. The size of both the Instruction and Data TCM blocks are implementor-specific and can range from 0KB to 1MB.

- Instruction and data caches. The design can be easily modified to enable any combination of caches from 0KB to 1MB.

- A protection unit that enables the memory to be protected in a simple manner, ideal for embedded control applications.

- An AMBA AHB bus interface. The ARM946E-S processor interfaces to the rest of the system are through use of unified address and data buses. This interface is compatible with the AMBA AHB bus standard.

- Support for external coprocessors enabling floating point or other application specific hardware acceleration to be added. For coprocessor support, the instruction and data buses are exported along with simple handshaking signals.

- Support for the use of a scan test methodology for the standard cell logic and *Built-In-Self-Test* (BIST) for the TCM and caches.

- An interface to an external *Embedded Trace Macrocell* (ETM) to support real-time tracing of instructions and data.

Providing this complete high-frequency subsystem frees the system-on-a-chip designer to concentrate on design issues unique to their system. The synthesizable nature of the device eases integration into ASIC technologies.

The ARM946E-S processor is targeted at a wide range of embedded applications where high-performance, low system cost, small die size, and low power are all important.

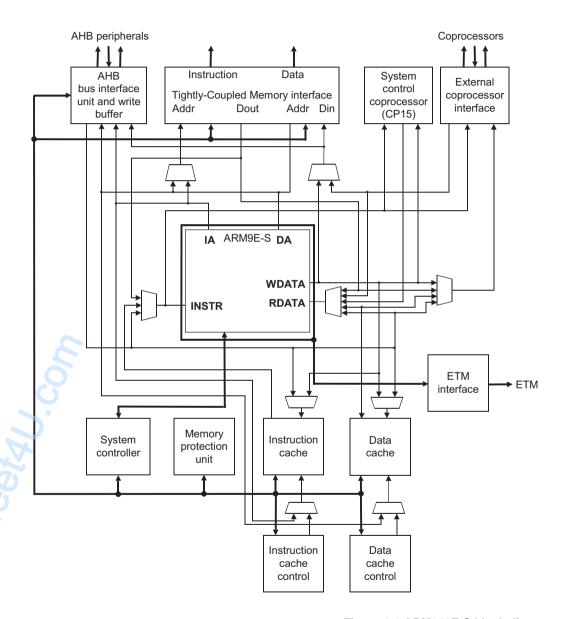

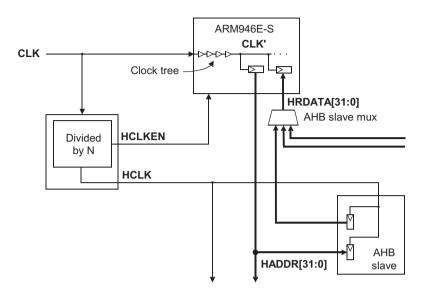

### 1.2 ARM946E-S block diagram

The ARM946E-S block diagram is shown in Figure 1-1.

Figure 1-1 ARM946E-S block diagram

The blocks shown in Figure 1-1 on page 1-3 are described in the locations listed in Table 1-1.

Table 1-1 Location of block descriptions

| Block                                   | Location of description                                         |

|-----------------------------------------|-----------------------------------------------------------------|

| ARM9E-S (Rev 1)                         | ARM9E-S (Rev 1) Technical Reference<br>Manual                   |

| AHB bus interface unit and write buffer | Chapter 6 Bus Interface Unit and Write<br>Buffer                |

| Tightly-coupled Memory interface        | Chapter 5 Tightly-Coupled Memory<br>Interface                   |

| System control coprocessor (CP15)       | Chapter 2 Programmer's Model                                    |

| External coprocessor interface          | Chapter 7 Coprocessor Interface                                 |

| ETM interface                           | Chapter 8 ETM Interface                                         |

| System controller                       | Chapter 2 Programmer's Model                                    |

| Memory protection unit                  | Chapter 4 Protection Unit                                       |

| Instruction cache                       | Chapter 3 Caches                                                |

| Data cache                              | Chapter 3 Caches                                                |

| Instruction cache control               | Chapter 2 <i>Programmer's Model</i> and Chapter 3 <i>Caches</i> |

| Data cache control                      | Chapter 2 <i>Programmer's Model</i> and Chapter 3 <i>Caches</i> |

### 1.3 Differences between processor versions

The differences between the current version of the processor and Rev 0 are as follows:

- Tightly coupled memories are external to the macrocell. Refer to Chapter 5 *Tightly-Coupled Memory Interface*.

- The AHB interface is changed to improve the input timing. Refer to Chapter 6 *Bus Interface Unit and Write Buffer*.

- The AHB interface is changed to generate BUSY cycles during access types. Refer to Chapter 5 *Tightly-Coupled Memory Interface*.

Introduction

# Chapter 2 **Programmer's Model**

This chapter describes the programmer's model for the ARM946E-S processor. It contains the following sections:

- About the ARM946E-S programmer's model on page 2-2

- About the ARM9E-S programmer's model on page 2-3

- *CP15 register map summary* on page 2-4.

#### 2.1 About the ARM946E-S programmer's model

The programmer's model for the ARM946E-S processor primarily consists of the ARM9E-S core programmer's model (see *About the ARM9E-S programmer's model* on page 2-3). Additions to this model are required to control the operation of the ARM946E-S internal coprocessors, and any coprocessor connected to the external coprocessor interface.

There are two internal coprocessors within the ARM946E-S processor:

- CP14 within the ARM9E-S core enables software access to the debug communication channel

- CP15 enables configuration of the caches, *Tightly-Coupled Memory* (TCM), protection unit, write buffer, and other ARM946E-S system options such as big or little-endian operation.

The registers defined in CP14 are accessible with MCR and MRC instructions, and are described in *The debug communication channel* on page 9-29.

The registers defined in CP15 are accessible with MCR and MRC instructions, and are described in *CP15 register map summary* on page 2-4. These instructions permit conditional access using the optional {cond} field.

Registers and operations provided by any coprocessors attached to the external coprocessor interface are accessible with appropriate coprocessor instructions.

#### 2.2 About the ARM9E-S programmer's model

The ARM9E-S core implements the ARMv5TE architecture, which includes the 32-bit ARM instruction set and the 16-bit Thumb instruction set. For a description of both instruction sets, see the *ARM Architecture Reference Manual*.

#### 2.2.1 Data Abort model

The ARM9E-S implements the *base restored Data Abort model*, which differs from the *base updated Data Abort model* implemented by ARM7TDMI.

The difference in the Data Abort model affects only a very small section of operating system code, the Data Abort handler. It does not affect user code. With the base restored Data Abort model, when a Data Abort exception occurs during the execution of a memory access instruction, the base register is always restored by the processor hardware to the value the register contains before the instruction is executed. This removes the requirement for the Data Abort handler to repair any base register update that might have been specified by the aborted instruction.

The base restored Data Abort model significantly simplifies the Data Abort handler software.

#### 2.3 CP15 register map summary

The ARM946E-S processor incorporates CP15 for system control. CP15 enables configuration of the caches, *Tightly-Coupled Memory* (TCM), and protection unit. It also enables configuration of the ARM946E-S system options including big or little-endian operation.

This section contains the following:

- Accessing CP15 registers on page 2-6

- Register 0, ID Code Register on page 2-7

- Register 0, Cache Type Register on page 2-8

- Register 0, Tightly-coupled Memory Size Register on page 2-10

- Register 1, Control Register on page 2-12

- Register 2, Cache Configuration Registers on page 2-16

- Register 3, Write Buffer Control Register on page 2-16

- Register 5, Access Permission Registers on page 2-17

- Register 6, Protection Region Base and Size Registers on page 2-20

- Register 7, Cache Operations Register on page 2-22

- Register 9, Cache Lockdown Registers on page 2-26

- Register 9, Tightly-coupled Memory Region Registers on page 2-26.

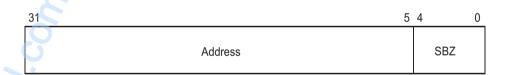

- Register 13, Trace Process Identifier Register on page 2-29

- Register 15, BIST Control Registers on page 2-29

- Register 15, Test State Register on page 2-32

- Register 15, Cache Debug Index Register on page 2-33

- Register 15, Trace Control Register on page 2-35.

The register map for CP15 is shown in Table 2-1 on page 2-5.

Table 2-1 CP15 register map

| Register | Read                                         | Write                                        |

|----------|----------------------------------------------|----------------------------------------------|

| 0        | ID code <sup>a</sup>                         | Unpredictable                                |

| 0        | Cache type <sup>a</sup>                      | Unpredictable                                |

| 0        | Tightly-coupled memory size <sup>a</sup>     | Unpredictable                                |

| 1        | Control                                      | Control                                      |

| 2        | Cache configuration <sup>b</sup>             | Cache configuration <sup>b</sup>             |

| 3        | Write buffer control                         | Write buffer control                         |

| 4        | Unpredictable                                | Unpredictable                                |

| 5        | Access permission b                          | Access permission b                          |

| 6        | Protection region base and size <sup>a</sup> | Protection region base and size <sup>a</sup> |

| 7        | Unpredictable                                | Cache operations <sup>a</sup>                |

| 8        | Unpredictable                                | Unpredictable                                |

| 9        | Cache lockdown ab                            | Cache lockdown ab                            |

| 9        | Tightly-coupled memory region ab             | Tightly-coupled memory region ab             |

| 10       | Unpredictable                                | Unpredictable                                |

| 11       | Unpredictable                                | Unpredictable                                |

| 12       | Unpredictable                                | Unpredictable                                |

| 13       | Trace process ID                             | Trace process ID                             |

| 14       | Unpredictable                                | Unpredictable                                |

| 15       | BIST control a                               | BIST control <sup>a</sup>                    |

| 15       | Test state <sup>a</sup>                      | Test state <sup>a</sup>                      |

| 15       | Cache debug index <sup>a</sup>               | Cache debug index <sup>a</sup>               |

| 15       | Trace control <sup>a</sup>                   | Trace control a                              |

Register location provides access to more than one register. The register accessed depends on the value of the opcode\_2 or CRm field. See the register description for details.

b. Separate registers for instruction and data. See the register description for details.

#### 2.3.1 Accessing CP15 registers

Table 2-2 shows the terms and abbreviations used in this section.

Table 2-2 CP15 terms and abbreviations

| Term           | Abbreviation | Description                                                                                           |

|----------------|--------------|-------------------------------------------------------------------------------------------------------|

| Unpredictable  | UNP          | For reads, the data returned when reading from this location is Unpredictable. It can have any value. |

|                |              | For writes, writing to this location causes                                                           |

|                |              | Unpredictable behavior, or an Unpredictable change in device configuration.                           |

| Undefined      | UND          | An instruction that accesses CP15 in the manner indicated takes the undefined instruction trap.       |

| Should Be Zero | SBZ          | When writing to this location, all bits of this field should be 0.                                    |

| Should Be One  | SBO          | When writing to this location, all bits of this field should be 1.                                    |

In all cases, reading from, or writing any data values to any CP15 registers, including those fields specified as Unpredictable or Should Be Zero, does not cause any permanent damage.

All CP15 register bits that are defined and contain state are set to 0 by **HRESETn** unless otherwise stated in this chapter.

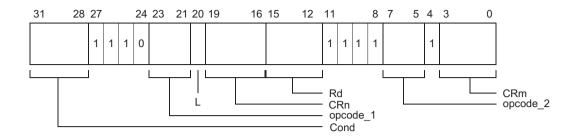

CP15 registers can only be accessed with MRC and MCR instructions in a privileged mode. The instruction bit pattern of the MCR and MRC instructions is shown in Figure 2-1 on page 2-7.

Figure 2-1 CP15 MRC and MCR bit pattern

The assembler for these instructions is:

MCR/MRC{cond} p15,opcode\_1,Rd,CRn,CRm,opcode\_2

Instructions CDP, LDC, and STC, along with unprivileged MRC and MCR instructions to CP15, cause the Undefined instruction trap to be taken. The CRn field of MRC and MCR instructions specifies the coprocessor register to access. The CRm field and opcode\_2 field specify a particular action when addressing registers.

Attempting to read from a nonreadable register, or writing to a nonwritable register causes Unpredictable results.

The opcode\_1, opcode\_2, and CRm fields Should Be Zero, except when the values specified are used to select the desired operations, in all instructions that access CP15. Using other values results in Unpredictable behavior.

#### 2.3.2 Register 0, ID Code Register

This is a read-only register that returns a 32-bit device ID code. The ID Code Register is accessed by reading CP15 register 0 with the opcode\_2 field set to any value other than 1 or 2. For example:

MRC p15, 0, Rd, c0, c0, {0,3-7}; returns ID register

The contents of the ID code are shown in Table 2-3.

Table 2-3 Register 0, ID code

| Register bits | Function                          | Value |

|---------------|-----------------------------------|-------|

| [31:24]       | Implementor                       | 0x41  |

| [23:20]       | Variant (reserved)                | 0x0   |

| [19:16]       | ARM architecture 5TE              | 0x5   |

| [15:4]        | Primary part number               | 0x946 |

| [3: 0]        | Revision (major product revision) | 0x1   |

#### 2.3.3 Register 0, Cache Type Register

This is a read-only register that contains information about the size and architecture of the instruction cache and data cache, enabling operating systems to establish how to perform operations such as cache cleaning and lockdown. Future ARM cached processors will contain this register, enabling RTOS vendors to produce future-proof versions of their operating systems.

The cache type register is accessed by reading CP15 register 0 with the opcode\_2 field set to 1. For example:

MCR p15,0,Rd,c0,c0,1; returns cache details

The format of the register is shown in Table 2-4.

**Table 2-4 Cache Type Register format**

| Register bits | Function                 | Value                      |

|---------------|--------------------------|----------------------------|

| [31:29]       | Reserved                 | b000                       |

| [28:25]       | Cache type               | b0111                      |

| [24]          | Harvard/unified          | b1 (defines Harvard cache) |

| [23:22]       | Reserved                 | b00                        |

| [21:18]       | Data cache size          | Implementation-specific    |

| [17:15]       | Data cache associativity | Implementation-specific    |

| [14]          | Data cache absent        | Implementation-specific    |

**Table 2-4 Cache Type Register format (continued)**

| Register bits | Function                         | Value                          |

|---------------|----------------------------------|--------------------------------|

| [13:12]       | Data cache words per line        | b10 (defines 8 words per line) |

| [11:10]       | Reserved                         | b00                            |

| [9:6]         | Instruction cache size           | Implementation-specific        |

| [5:3]         | Instruction cache associativity  | Implementation-specific        |

| [2]           | Instruction cache absent         | Implementation-specific        |

| [1:0]         | Instruction cache words per line | b10 (defines 8 words per line) |

Bits [28:25] indicate which major cache class the implementation falls into. b0111 means that the cache provides:

- cache-clean-step operation

- cache-flush-step operation

- lock-down facilities.

Bits [21:18] give the data cache size. Bits [9:6] give the instruction cache size. Table 2-5 lists the meaning of values used for cache size encoding.

Table 2-5 Cache size encoding

| Bits [21:18] and bits[9:6] | Cache size |

|----------------------------|------------|

| b0000                      | 0KB        |

| b0011                      | 4KB        |

| b0100                      | 8KB        |

| b0101                      | 16KB       |

| b0110                      | 32KB       |

| b0111                      | 64KB       |

| b1000                      | 128KB      |

| b1001                      | 256KB      |

| b1010                      | 512KB      |

| b1011                      | 1MB        |

Bits [17:15] give the data cache associativity. Bits [5:3] give the instruction cache associativity. Table 2-6 lists the meaning of values used for cache associativity encoding.

Table 2-6 Cache associativity encoding

| Bits [17:15] and bits [5:3] | Associativity |

|-----------------------------|---------------|

| b000                        | Direct mapped |

| b010                        | 4             |

The cache associativity fields in the cache type register are implementation-specific (implementor-defined). Therefore, if the implementation has an instruction or data cache, the associativity for that cache is set to b010 to indicate a four-way set associative cache. If either cache is not included in a specific implementation, then the associativity field for that cache is set to b000 to indicate that the cache is absent.

Bit 14 gives the data cache base size and bit 2 gives the instruction cache base size.

The base size bits are implementation-specific. If the implementation has an instruction or data cache, the base size bit for that cache is set to 0, indicating that the cache type parameters are valid. If either cache is not included for a specific implementation, the relevant base size is set to 1, indicating that the cache is absent.

The cache base size and cache size fields are generated within the cache blocks to avoid having to resynthesize the design for different cache sizes.

#### 2.3.4 Register 0, Tightly-coupled Memory Size Register

This is a read-only register that returns the size of the Instruction and Data *Tightly-coupled Memory* (TCM) integrated with the ARM946E-S processor. The register contents reflect the state of input signals **PhyITCMSize**[3:0] and **PhyDTCMSize**[3:0].

The tightly-coupled memory size register is accessed by reading CP15 register 0 with the opcode\_2 field set to 2. For example:

MRC p15, 0, Rd, c0, c0, 2; returns tightly-coupled memory size register

The register contains information about the size of the Instruction TCM and Data TCM. The format of the register is shown in Table 2-7.

**Table 2-7 Tightly-coupled Memory Size Register**

| Register bits | Meaning                | Value                   |

|---------------|------------------------|-------------------------|

| [31:22]       | Reserved               | ь0000000000             |

| [21:18]       | Data TCM size          | Implementation-specific |

| [17:15]       | Reserved               | b000                    |

| [14]          | Data TCM absent        | Implementation-specific |

| [13:10]       | Reserved               | b0000                   |

| [9:6]         | Instruction TCM size   | Implementation-specific |

| [5:3]         | Reserved               | b000                    |

| [2]           | Instruction TCM absent | Implementation-specific |

| [1:0]         | Reserved               | b00                     |

The memory size parameters are implementation-specific. The values used are generated within the memory blocks. This enables the memory size to be changed without having to re-synthesize the full design. Bits [21:18] define the Data TCM size. Bits [9:6] define the Instruction TCM size. Table 2-8 shows the memory size field definitions for Instruction and Data TCM sizes.

Table 2-8 Memory size field

| Bits [21:18] and bits [9:6] | TCM size |

|-----------------------------|----------|

| b0000                       | 0KB      |

| b0011                       | 4KB      |

| b0100                       | 8KB      |

| b0101                       | 16KB     |

| b0110                       | 32KB     |

| b0111                       | 64KB     |

| b1000                       | 128KB    |

Table 2-8 Memory size field (continued)

| Bits [21:18] and bits [9:6] | TCM size |

|-----------------------------|----------|

| b1001                       | 256KB    |

| b1010                       | 512KB    |

| b1011                       | 1MB      |

If the TCM is absent, then the relevant TCM absent bit (bit 14 or bit 2) in the tightly-coupled memory size register Must Be One. If TCM is present within the design, the relevant TCM absent bit Should Be Zero.

## 2.3.5 Register 1, Control Register

This register contains the control bits of the ARM946E-S processor. All reserved bits must either be written with zero or one, as indicated, or written using read-modify-write. The reserved bits have an Unpredictable value when read. To read and write this register:

MRC p15, 0, Rd, c1, c0, 0; read control register MCR p15, 0, Rd, c1, c0, 0; write control register

Table 2-9 lists the functions controlled by register 1.

Table 2-9 Register 1, Control Register

| Register bits | Function                  |

|---------------|---------------------------|

| [31:20]       | Reserved (SBZ)            |

| [19]          | Instruction TCM load mode |

| [18]          | Instruction TCM enable    |

| [17]          | Data TCM load mode        |

| [16]          | Data TCM enable           |

| [15]          | Disable loading TBIT      |

| [14]          | Round-robin replacement   |

| [13]          | Alternate vector select   |

| [12]          | Instruction cache enable  |

| [11:8]        | Reserved (SBZ)            |

Table 2-9 Register 1, Control Register (continued)

| Register bits | Function               |

|---------------|------------------------|

| [7]           | Big-endian             |

| [6:3]         | Reserved (SBO)         |

| [2]           | Data cache enable      |

| [1]           | Reserved (SBZ)         |

| [0]           | Protection unit enable |

The bits in the Control Register are described in this section.

#### Bit 19, Instruction TCM load mode

This bit controls the operation of the Instruction TCM load mode.

You can use the Instruction TCM load mode for initializing the Instruction TCM. The Instruction TCM load mode enables you to load data into the ARM946E-S processor from either data cache or main memory, and then write to the same address but within the Instruction TCM. This enables you to copy boot code from memory located at address 0x0 into the Instruction TCM which, when enabled, also exists at address 0x0. The operation of the load mode is described in *Initializing the Instruction TCM* on page 5-3.

At reset this bit is cleared.

#### Bit 18, Instruction TCM enable

This bit controls operation of the Instruction TCM. When the Instruction TCM is enabled, all instruction and data accesses to the Instruction TCM address range access the Instruction TCM.

At reset this bit takes the value of the input pin **INITRAM**.

#### Bit 17, Data TCM load mode

This bit controls the operation of the Data TCM load mode. You can use the Data TCM load mode for initializing the Data TCM. The Data TCM load mode enables you to load data into ARM registers from either data cache or main memory, and then write to the same address but within the Data TCM. The operation of the load mode is described in *Initializing the Data TCM* on page 5-5.

At reset this bit is cleared.

#### Bit 16, Data TCM enable

This bit controls operation of the Data TCM. When the Data TCM is enabled, it takes precedence over the data cache and AHB for data accesses.

At reset this bit is cleared.

#### Bit 15, Disable loading TBIT

This bit controls the behavior of load PC instructions. When clear the ARMv5TE-specific behavior is enabled, and bit 0 of the loaded data is used to control the entry into Thumb state when the PC (r15) is the destination register. When set, this ARMv5TE behavior is disabled.

At reset this bit is cleared.

#### Bit 14, Round-robin replacement

This bit controls the cache replacement algorithm.

When set, round-robin replacement is used. When clear, a pseudo-random replacement algorithm is used.

At reset this bit is cleared.

#### Bit 13, Alternate vectors select

This bit controls the base address used for the exception vectors.

When clear, the base address for the exception vectors is 0x00000000. When set, the base address is 0xFFFF0000.

This bit is initialized either set or clear during system reset, depending on the value of the input pin, **VINITHI**. This enables you to define the exception vector location during reset to suit the boot mechanism of the application. You can then reprogram this bit as required following system reset.

#### Bit 12, Instruction cache enable

You must not enable the instruction cache if your implementation is configured with zero size cache. Enabling the instruction cache when no cache is present can lead to Unpredictable behavior.

Controls the behavior of the instruction cache. To use the instruction cache, both the protection unit enable bit (bit 0) and the instruction cache enable bit must be set. This can be done with a single write to register 1.

At reset this bit is cleared.

#### Bit 7, Endian configuration

Selects the endian configuration of the ARM946E-S processor. When this bit is set, big-endian configuration is selected. When clear, little-endian configuration is selected.

At reset this bit is cleared.

#### Bit 2, Data cache enable

You must not enable the data cache if your implementation is configured with zero size cache. Enabling the data cache when no cache is present can lead to Unpredictable behavior.

This bit controls the behavior of the data cache.

To use the data cache, both the protection unit enable bit (bit 0) and the data cache enable bit must be set. This can be done with a single write to register 1.

At reset this bit is cleared.

## Bit 0, Protection unit enable

This bit controls the operation of the ARM946E-S protection unit.

At reset this bit is cleared. This disables the protection unit, and as a result disables the instruction and data caches and the write buffer.

At least one protection region (see *Register 6, Protection Region Base and Size Registers* on page 2-20 and Chapter 4 *Protection Unit*) must be programmed before the protection unit is enabled.

## 2.3.6 Register 2, Cache Configuration Registers

These registers contain the cachable attributes for the eight areas of memory. Individual control is provided for the instruction and data caches. If the opcode\_2 field is 0, then the data cache bits are programmed. If the opcode\_2 field is 1, then the instruction cache bits are programmed. To read and write these registers:

```

MRC p15, 0, Rd, c2, c0, 0; read data cachable bits MRC p15, 0, Rd, c2, c0, 1; read instruction cachable bits MCR p15, 0, Rd, c2, c0, 0; write data cachable bits MCR p15, 0, Rd, c2, c0, 1; write instruction cachable bits

```

The format for the cachable bits in data and instruction areas is the same, and is given in Table 2-10.

Table 2-10 Programming instruction and data cachable bits

| Register bits | Function                      |

|---------------|-------------------------------|

| [7]           | Cachable bit (C_7) for area 7 |

| [6]           | Cachable bit (C_6) for area 6 |

| [5]           | Cachable bit (C_5) for area 5 |

| [4]           | Cachable bit (C_4) for area 4 |

| [3]           | Cachable bit (C_3) for area 3 |

| [2]           | Cachable bit (C_2) for area 2 |

| [1]           | Cachable bit (C_1) for area 1 |

| [0]           | Cachable bit (C_0) for area 0 |

# 2.3.7 Register 3, Write Buffer Control Register

This register contains the write buffer control (bufferable) attribute for the eight areas of memory.

—— Note ———— This register only applies to data accesses.

To read and write the write buffer control register:

MCR p15, 0, Rd, c3, c0, 0; write data bufferable bits MRC p15, 0, Rd, c3, c0, 0; read data bufferable bits

The format for the bufferable bits in the data areas is given in Table 2-11.

Table 2-11 Programming data bufferable bits

| Register bits | Function                             |

|---------------|--------------------------------------|

| [7]           | Bufferable bit (B_7) for data area 7 |

| [6]           | Bufferable bit (B_6) for data area 6 |

| [5]           | Bufferable bit (B_5) for data area 5 |

| [4]           | Bufferable bit (B_4) for data area 4 |

| [3]           | Bufferable bit (B_3) for data area 3 |

| [2]           | Bufferable bit (B_2) for data area 2 |

| [1]           | Bufferable bit (B_1) for data area 1 |

| [0]           | Bufferable bit (B_0) for data area 0 |

#### 2.3.8 Register 5, Access Permission Registers

There are four access permission registers. These contain the access permission bits for the instruction and data protection regions. The opcode\_2 field of the MCR/MRC instruction determines whether the standard or extended registers are accessed, and if the instruction or data access permissions are accessed. To read and write the extended registers:

```

MRC p15, 0, Rd, c5, c0, 2; read data access permission bits MRC p15, 0, Rd, c5, c0, 3; read instruction access permission bits MCR p15, 0, Rd, c5, c0, 2; write data access permission bits MCR p15, 0, Rd, c5, c0, 3; write instruction access permission bits

```

The format for the access permission bits in instruction and data areas is the same, and is given in Table 2-12.

Table 2-12 Programming instruction and data access permission bits (extended)

| Register bits | Function                 |

|---------------|--------------------------|

| [31:28]       | Ap7[3:0] bits for area 7 |

| [27:24]       | Ap6[3:0] bits for area 6 |

| [23:20]       | Ap5[3:0] bits for area 5 |

| [19:16]       | Ap4[3:0] bits for area 4 |

Table 2-12 Programming instruction and data access permission bits (extended)

| Register bits | Function                 |

|---------------|--------------------------|

| [15:12]       | Ap3[3:0] bits for area 3 |

| [11:8]        | Ap2[3:0] bits for area 2 |

| [7:4]         | Ap1[3:0] bits for area 1 |

| [3:0]         | Ap0[3:0] bits for area 0 |

The values of the IApn[3:0] and DApn[3:0] bits define the access permission for each area of memory, n. The encoding is shown in Table 2-13.

Table 2-13 Access permission encoding (extended)

| I/DApn[3:0] | Access permission<br>Privileged | User              |

|-------------|---------------------------------|-------------------|

| b0000       | No access                       | No access         |

| b0001       | Read/write access               | No access         |

| b0010       | Read/write access               | Read-only         |

| b0011       | Read/write access               | Read/write access |

| b0100       | UNP                             | UNP               |

| b0101       | Read-only                       | No access         |

| b0110       | Read-only                       | Read-only         |

| b0111       | UNP                             | UNP               |

| b1xxx       | UNP                             | UNP               |

The following instructions are supported for backwards compatibility with existing ARM processors with memory protection, and access the standard registers:

MRC p15, 0, Rd, c5, c0, 0; read data access permission bits

MRC p15, 0, Rd, c5, c0, 1; read instruction access permission bits

MCR p15, 0, Rd, c5, c0, 0; write data access permission bits

MCR p15, 0, Rd, c5, c0, 1; write instruction access permission bits

The data format for these registers is shown in Table 2-14.

Table 2-14 Instruction and data access permission bits (standard)

| Register bits | Function                 |

|---------------|--------------------------|

| [15:14]       | Ap7[1:0] bits for area 7 |

| [13:12]       | Ap6[1:0] bits for area 6 |

| [11:10]       | Ap5[1:0] bits for area 5 |

| [9:8]         | Ap4[1:0] bits for area 4 |

| [7:6]         | Ap3[1:0] bits for area 3 |

| [5:4]         | Ap2[1:0] bits for area 2 |

| [3:2]         | Ap1[1:0] bits for area 1 |

| [1:0]         | Ap0[1:0] bits for area 0 |

The values of the IApn[1:0] and DApn[1:0] bits define the access permission for each area of memory, n. The encoding is shown in Table 2-15.

Table 2-15 Access permission encoding (standard)

| 1/DA [1 -0] | Access permission |                   |

|-------------|-------------------|-------------------|

| I/DApn[1:0] | Privileged        | User              |

| b00         | No access         | No access         |

| b01         | Read/write access | No access         |

| b10         | Read/write access | Read-only         |

| b11         | Read/write access | Read/write access |

Note

On reset, the values of IApn and DApn bits are undefined. However, because on reset the protection unit is disabled, this is as though all areas are set to privileged mode read/write access and User read/write access. Therefore, you must program the access permission registers before you enable the protection unit.

If the access permissions are initially programmed using the extended access permissions (see Table 2-13 on page 2-18), and then reprogrammed using the standard access permissions (see Table 2-15 on page 2-19), the access permissions applied are as if Apn[3:2] are programmed to b00 in Table 2-13 on page 2-18.

## 2.3.9 Register 6, Protection Region Base and Size Registers

These registers define the protection region base address and size. You can define eight programmable regions using these registers. The values are ignored when the protection unit is disabled, and on reset only the region enable bit for each region is reset to 0. All other bits are undefined. You must program at least one memory region before you enable the protection unit.

The instructions used to access the eight Protection Region Base and Size Registers are listed in Table 2-16.

Table 2-16 Accessing Protection Region Base and Size Registers

| ARM instruction               | Protection Region Base and Size Register |

|-------------------------------|------------------------------------------|

| MCR/MRC p15, 0, Rd, c6, c7, 0 | Memory region 7                          |

| MCR/MRC p15, 0, Rd, c6, c6, 0 | Memory region 6                          |

| MCR/MRC p15, 0, Rd, c6, c5, 0 | Memory region 5                          |

| MCR/MRC p15, 0, Rd, c6, c4, 0 | Memory region 4                          |

| MCR/MRC p15, 0, Rd, c6, c3, 0 | Memory region 3                          |

| MCR/MRC p15, 0, Rd, c6, c2, 0 | Memory region 2                          |

| MCR/MRC p15, 0, Rd, c6, c1, 0 | Memory region 1                          |

| MCR/MRC p15, 0, Rd, c6, c0, 0 | Memory region 0                          |

Each Protection Region Base and Size Register has the format shown in Table 2-17.

Table 2-17 Protection Region Base and Size Register format

| Register bits | Function                                              |

|---------------|-------------------------------------------------------|

| [31:12]       | Region base address                                   |

| [5:1]         | Region size                                           |

| [0]           | 1 = Region enable<br>0 = Region disable<br>Reset to 0 |

You must align the region base to a region size boundary, where the region size is defined in its respective protection region register. The behavior is Unpredictable if this is not done.

Region sizes are encoded as shown in Table 2-18.

Table 2-18 Region size encoding

| Bit encoding     | Region size    |

|------------------|----------------|

| b00000 to b01010 | Reserved (UNP) |

| b01011           | 4KB            |

| b01100           | 8KB            |

| b01101           | 16KB           |

| b01110           | 32KB           |

| b01111           | 64KB           |

| b10000           | 128KB          |

| b10001           | 256KB          |

| b10010           | 512KB          |

| b10011           | 1MB            |

| b10100           | 2MB            |

| b10101           | 4MB            |

| b10110           | 8MB            |

Table 2-18 Region size encoding (continued)

| Bit encoding | Region size |

|--------------|-------------|

| b10111       | 16MB        |

| b11000       | 32MB        |

| b11001       | 64MB        |

| b11010       | 128MB       |

| b11011       | 256MB       |

| b11100       | 512MB       |

| b11101       | 1GB         |

| b11110       | 2GB         |

| b11111       | 4GB         |

#### **Example base setting**

An 8KB size region aligned to an 8KB boundary at 0x00002000 (covering the address range 0x00002000-0x00003FFF) is programmed as 0x00002019.

The following instruction is supported for backward compatibility with other ARM processors using a memory protection unit:

MRC p15, 0, Rd, c6, CRm, 1; returns protection region register

This instruction enables the protection region registers to be read.

You must not write to the protection region base and size registers with opcode\_2 set to 1 because the behavior is Unpredictable.

# 2.3.10 Register 7, Cache Operations Register

You can use a write to this register to perform the following operations:

- flush instruction cache and data cache

- prefetch an instruction cache line

- wait for interrupt

- drain the write buffer

- clean and flush the data cache.

The ARM946E-S processor uses a subset of the ARM architecture v4 functions (defined in the *ARM Architecture Reference Manual*). The available operations are summarized in Table 2-19.

**Table 2-19 Cache operations**

| ARM instruction            | Function                             | Value             |

|----------------------------|--------------------------------------|-------------------|

| MCR p15, 0, Rd, c7, c5, 0  | Flush instruction cache              | SBZa              |

| MCR p15, 0, Rd, c7, c5, 1  | Flush instruction cache single entry | Address           |

| MCR p15, 0, Rd, c7, c13, 1 | Prefetch instruction cache line      | Address           |

| MCR p15, 0, Rd, c7, c6, 0  | Flush data cache                     | $SBZ^a$           |

| MCR p15, 0, Rd, c7, c6, 1  | Flush data cache single entry        | Address           |

| MCR p15, 0, Rd, c7, c10, 1 | Clean data cache entry               | Address           |

| MCR p15, 0, Rd, c7, c14, 1 | Clean and flush data cache entry     | Address           |

| MCR p15, 0, Rd, c7, c10, 2 | Clean data cache entry               | Index and segment |

| MCR p15, 0, Rd, c7, c14, 2 | Clean and flush data cache entry     | Index and segment |

a. The value transferred in Rd Should Be Zero.

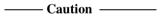

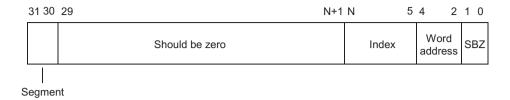

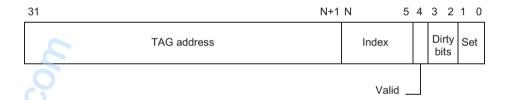

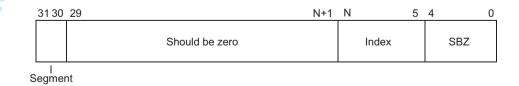

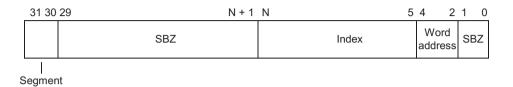

The data format for index and segment operations is shown in Figure 2-2.

Figure 2-2 Register 7, Index and segment format

The size of the index (N:5) varies depending on the implemented cache size. Table 2-20 shows how the index size changes for the cache sizes supported by the ARM946E-S processor.

Table 2-20 Index fields for supported cache sizes

| Cache size | Index  |

|------------|--------|

| 4KB        | [9:5]  |

| 8KB        | [10:5] |

| 16KB       | [11:5] |

| 32KB       | [12:5] |

| 64KB       | [13:5] |

| 128KB      | [14:5] |

| 256KB      | [15:5] |

| 512KB      | [16:5] |

| 1MB        | [17:5] |

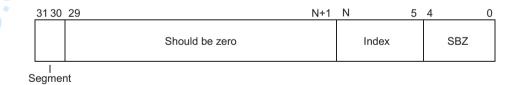

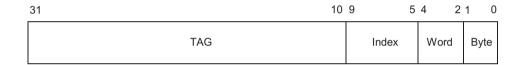

For the instruction cache prefetch operation, the data format is shown in Figure 2-3.

Figure 2-3 Instruction cache address format

# Cache clean and flush operations

Cache clean and flush operations can occur during instruction and data linefetches. In such circumstances the linefetch completes before the clean or flush operation is executed.

#### **Drain write buffer**

This operation stalls instruction execution until the write buffer is emptied. This is useful in real-time applications where the processor must be sure that a write to a peripheral has completed before program execution continues. An example is where a

peripheral in a bufferable region is the source of an interrupt. When the interrupt has been serviced, the request must be removed before interrupts can be re-enabled. This is ensured if a drain write buffer operation separates the store to the peripheral and the enable interrupt functions.

The drain write buffer operation is invoked by a write to register 7 using the following ARM instruction:

MCR p15, 0, Rd, c7, c10, 4; drain write buffer

This stalls the processor core until any outstanding accesses in the write buffer are completed, that is, until all data is written to external memory.

#### Wait for interrupt

This operation enables the ARM946E-S processor to enter a low-power standby mode. When you invoke this operation, the processor core is halted and the cache and TCMs are placed in a low-power state until either an interrupt or a debug request occurs. This function is invoked by a write to register 7. The following ARM instruction causes this to occur:

MCR p15, 0, Rd, c7, c0, 4; wait for interrupt

This is the preferred encoding for new software. For compatibility with existing software, the ARM946E-S processor also supports the following ARM instruction that has the same affect:

MCR p15, 0, Rd, c15, c8, 2; wait for interrupt

This stalls the processor from the time that this instruction is executed until either **nFIQ**, **nIRQ**, or **EDBGRQ** are asserted. Also, if the debugger sets the debug request bit in the EmbeddedICE-RT logic control register then this causes the *wait for interrupt* condition to terminate.

In the case of **nFIQ** and **nIRQ**, the processor operation continues regardless of whether the interrupts are enabled or disabled (that is, independent of the I and F bits in the processor CPSR). **DBGEN** must be set (debug enabled) if this operation of **EDBGRQ** or of the debug request bit is required.

If interrupts are enabled, the ARM9E-S core is guaranteed to take the interrupt before executing the instruction after the *wait for interrupt*. If debug request is used to wake up the system, the processor enters debug state before executing any more instructions.

The write buffer continues to drain until empty while the wait for interrupt operation is executing.

#### 2.3.11 Register 9, Cache Lockdown Registers

These registers enable you to lock down regions of the cache. To read and write these registers:

```

MCR p15, 0, Rd, c9, c0, 0; write data lockdown control MRC p15, 0, Rd, c9, c0, 0; read data lockdown control MCR p15, 0, Rd, c9, c0, 1; write instruction lockdown control MRC p15, 0, Rd, c9, c0, 1; read instruction lockdown control

```

The format of the register, Rd, transferred during this operation is shown in Table 2-21.

| Register bits | Function                      |

|---------------|-------------------------------|

| [31]          | Load bit, DL/IL               |

| [30:2]        | UNP/SBZ                       |

| [1:0]         | Cache segment, Dindex, Iindex |

**Table 2-21 Lockdown Register format**

Lockdown is described in *Cache lockdown* on page 3-12.

## 2.3.12 Register 9, Tightly-coupled Memory Region Registers

These registers enable you to modify the visible size of the TCMs.

You can either increase or decrease the size of the TCMs from the physical sizes described in Register 0 (see *Register 0, Tightly-coupled Memory Size Register* on page 2-10). Increasing the visible size of the TCMs above the physical size enables aliasing within the TCM space. This feature is useful for debugging multitasking systems.

There is a memory region register for each of the TCMs:

```

MRC p15, 0, Rd, c9, c1, 0; read data tightly-coupled memory

MCR p15, 0, Rd, c9, c1, 0; write data tightly-coupled memory

MRC p15, 0, Rd, c9, c1, 1; read instruction tightly-coupled memory

MCR p15, 0, Rd, c9, c1, 1; write instruction tightly-coupled memory

```

Each TCM region register has the format shown in Table 2-22.

**Table 2-22 TCM Region Register format**

| Register bits | Function                                                          |

|---------------|-------------------------------------------------------------------|

| [31:12]       | Region base                                                       |

| [5:1]         | Area size Minimum size = 4KB Maximum size = 4GB (See Table 2-23). |

| [0]           | SBZ                                                               |

For a given number of aliases for the physical memory size (set in register 0), the area size is calculated in the following way:

```

Number of required aliases = x (where x is a power of 2) N = log_2x (or 2^N = x) Area size = Physical size + N

```

The encodings for the supported TCM area sizes are shown in Table 2-23.

Table 2-23 TCM area size encoding

| Bit encoding | TCM area size |

|--------------|---------------|

| b00011       | 4KB           |

| b00100       | 8KB           |

| b00101       | 16KB          |

| b00110       | 32KB          |

| b00111       | 64KB          |