3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

# MCM6810

## 128 × 8-BIT STATIC RANDOM ACCESS MEMORY

The MCM6810 is a byte-organized memory designed for use in busorganized systems. It is fabricated with N-channel silicon-gate technology. For ease of use, the device operates from a single power supply, has compatibility with TTL and DTL, and needs no clocks or refreshing because of static operation.

The memory is compatible with the M6800 Microcomputer Family, providing random storage in byte increments. Memory expansion is provided through multiple Chip Select inputs.

- Organized as 128 Bytes of 8 Bits

- Static Operation

- Bidirectional Three-State Data Input/Output

- Six Chip Select Inputs (Four Active Low, Two Active High)

- Single 5-Volt Power Supply

- TTL Compatible

- Maximum Access Time = 450 ns − MCM6810

360 ns - MCM68A10

250 ns - MCM68B10

#### ORDERING INFORMATION

| Package Type | Frequency (MHz) | Temperature    | Order Number |

|--------------|-----------------|----------------|--------------|

| Ceramic      | 1.0             | 0°C to 70°C    | MCM6810L     |

| L Suffix     | 1.0             | -40°C to 85°C  | MCM6810CL    |

|              | 1.5             | 0°C to 70°C    | MCM68A10L    |

|              | 1.5             | -40°C to 85°C  | MCM68A10CL   |

|              | 2.0             | 0°C to 70°C    | MCM68B10L    |

| Plastic      | 1.0             | 0°C to 70°C    | MCM6810P     |

| P Suffix     | 1.0             | – 40°C to 85°C | MCM6810CP    |

|              | 1.5             | 0°C to 70°C    | MCM68A10P    |

|              | 1.5             | – 40°C to 85°C | MCM68A10CP   |

|              | 2.0             | 0°C to 70°C    | MCM68B10P    |

| Cerdip       | 1.0             | 0°C to 70°C    | MCM6810S     |

| S Suffix     | 1.0             | -40°C to 85°C  | MCM6810CS    |

|              | 1.5             | 0°C to 70°C    | MCM68A10S    |

|              | 1.5             | -40°C to 85°C  | MCM68A10CS   |

|              | 2.0             | 0°C to 70°C    | MCM68B10S    |

# MOS

(N-CHANNEL, SILICON-GATE)

128×8-BIT STATIC RANDOM ACCESS MEMORY

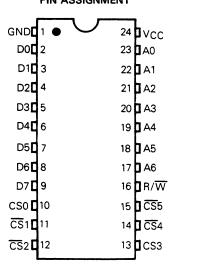

# PIN ASSIGNMENT

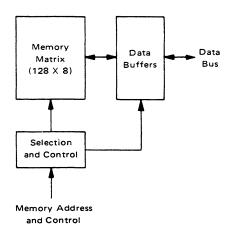

# MCM6810 RANDOM ACCESS MEMORY BLOCK DIAGRAM

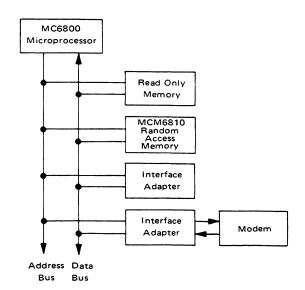

# M6800 MICROCOMPUTER FAMILY BLOCK DIAGRAM

#### **MAXIMUM RATINGS**

| Rating                                                                            | Symbol           | Value                                                      | Unit |

|-----------------------------------------------------------------------------------|------------------|------------------------------------------------------------|------|

| Supply Voltage                                                                    | Vcc              | -0.3 to $+7.0$                                             | ٧    |

| Input Voltage                                                                     | V <sub>in</sub>  | -0.3 to $+7.0$                                             | ٧    |

| Operating Temperature Range<br>MCM6810, MCM68A10, MCM68B10<br>MCM6810C, MCM68A10C | ТА               | T <sub>L</sub> to T <sub>H</sub><br>0 to +70<br>-40 to +85 | °C   |

| Storage Temperature Range                                                         | T <sub>stg</sub> | -65 to +150                                                | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage (e.g., either VSS or VCC).

#### THERMAL CHARACTERISTICS

| Characteristics    | Symbol           | Value | Unit |

|--------------------|------------------|-------|------|

| Thermal Resistance |                  |       |      |

| Ceramic            |                  | 60    |      |

| Plastic            | $\theta_{ m JA}$ | 120   | °C/W |

| Cerdip             |                  | 65    |      |

#### **POWER CONSIDERATIONS**

The average chip-junction temperature, T.J., in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D}.\theta_{JA}) \tag{1}$$

Where:

T<sub>A</sub> ≡ Ambient Temperature, °C

θ<sub>JA</sub>≡Package Thermal Resistance, Junction-to-Ambient, °C/W

PD≡PINT+PPORT

$P_{INT} = I_{CC} \times V_{CC}$ , Watts - Chip Internal Power

PPORT≡Port Power Dissipation, Watts — User Determined

For most applications PPORT ≪PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C) \tag{2}$$

Solving equations 1 and 2 for K gives:

$K = PD^{\bullet}(T_A + 273^{\circ}C) + \theta_{JA} \bullet PD^2$ (3)

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

#### **BLOCK DIAGRAM** D0 D1 A0 A1 23 22 D2 D3 D4 D5 D6 D7 Memory A2 A3 21 · 3-State Address Matrix Buffer Decode $(128 \times 8)$ 19 Α5 18 8 A6 17 <u>CS</u>5 <u>CS</u>4 15 14 . Memory CS3 13 Control CS2 12 $V_{CC} = Pin 24$ GND = Pin 1CS1 11 CS0 10-16 Read/Write

# DC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ Vdc } \pm 5\%$ , $V_{SS} = 0$ , $T_A = T_L$ to $T_H$ unless otherwise noted)

| Characteristic                                                                                                                                      |              | Symbol           | Min                   | Max                  | Unit  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----------------------|----------------------|-------|

| Input High Voltage                                                                                                                                  |              | VIH              | V <sub>SS</sub> + 2.0 | Vcc                  | V     |

| Input Low Voltage                                                                                                                                   |              | VIL              | V <sub>SS</sub> -0.3  | V <sub>SS</sub> +0.8 | V     |

| Input Current (A <sub>n</sub> , R/ $\overline{W}$ , $\overline{CS}_n$ ) (V <sub>in</sub> =0 to 5.25 V)                                              |              | lin              |                       | 2.5                  | μΑ    |

| Output High Voltage ( $I_{OH} = -205 \mu A$ )                                                                                                       |              | ∨он              | 2.4                   | -                    | V     |

| Output Low Voltage (IOL=1.6 mA)                                                                                                                     |              | VOL              | _                     | 0.4                  | V     |

| Output Leakage Current (Three-State) (CS = 0.8 V or $\overline{CS}$ = 2.0 V, V <sub>out</sub> = 0.4 V                                               | / to 2.4 V)  | <sup>I</sup> TSI | _                     | 10                   | μΑ    |

| Supply Current                                                                                                                                      | 1.0 MHz      |                  | _                     | 80                   | mA    |

| (V <sub>CC</sub> =5.25 V, All Other Pins Grounded)                                                                                                  | 1.5, 2.0 MHz | 1CC              |                       | 100                  | 11174 |

| Input Capacitance (A <sub>n</sub> , R/ $\overline{W}$ , CS <sub>n</sub> , $\overline{CS}_n$ ) (V <sub>in</sub> =0, T <sub>A</sub> =25°C, f=1.0 MHz) |              | Cin              | _                     | 7.5                  | рF    |

| Output Capacitance (D <sub>n</sub> ) ( $V_{out}=0$ , $T_A=25$ °C, $f=1.0$ MHz, $CSO=0$ )                                                            |              | C <sub>out</sub> | _                     | 12.5                 | рF    |

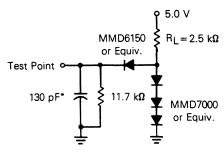

### AC TEST LOAD

\*Includes Jig Capacitance

### **AC OPERATING CONDITIONS AND CHARACTERISTICS**

**READ CYCLE** ( $V_{CC} = 5.0 \text{ V} \pm 5\%$ ,  $V_{SS} = 0$ ,  $T_A = T_L$  to  $T_H$  unless otherwise noted.)

|                            |                      | MCM | 16810 | мсм | 68A10 | MCM | 68B10 |      |

|----------------------------|----------------------|-----|-------|-----|-------|-----|-------|------|

| Characteristic             | Symbol               | Min | Max   | Min | Max   | Min | Max   | Unit |

| Read Cycle Time            | t <sub>cyc</sub> (R) | 450 | _     | 360 | _     | 250 | _     | ns   |

| Access Time                | tacc                 | T - | 450   | _   | 360   |     | 250   | ns   |

| Address Setup Time         | <sup>t</sup> AS      | 20  | -     | 20  | _     | 20  |       | ns   |

| Address Hold Time          | <sup>t</sup> AH      | 0   | _     | 0   | _     | 0   | _     | ns   |

| Data Delay Time (Read)     | †DDR                 | -   | 230   | _   | 220   | _   | 180   | ns   |

| Read to Select Delay Time  | tRCS                 | 0   | _     | 0   | _     | 0   | -     | ns   |

| Data Hold from Address     | tDHA                 | 10  | _     | 10  | _     | 10  | _     | ns   |

| Output Hold Time           | tн                   | 10  | _     | 10  | -     | 10  | _     | ns   |

| Data Hold from Read        | <sup>t</sup> DHR     | 10  | 80    | 10  | 60    | 10  | 60    | ns   |

| Read Hold from Chip Select | <sup>t</sup> RH      | 0   |       | 0   | _     | 0   | _     | ns   |

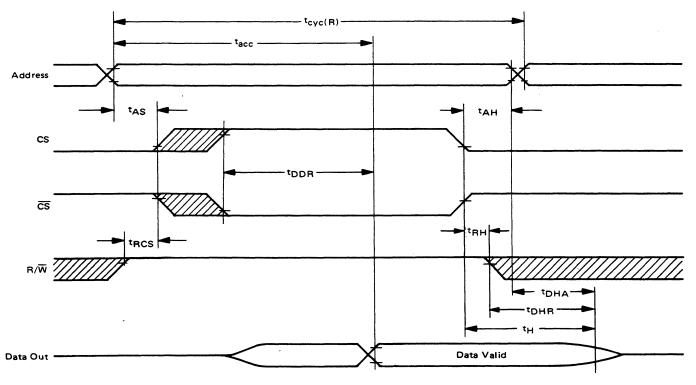

#### **READ CYCLE TIMING**

- Voltage levels shown are V<sub>L</sub>≤0.4 V, V<sub>H</sub>≥2.4 V, unless otherwise specified.

Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

- 3. CS and  $\overline{\text{CS}}$  have same timing.

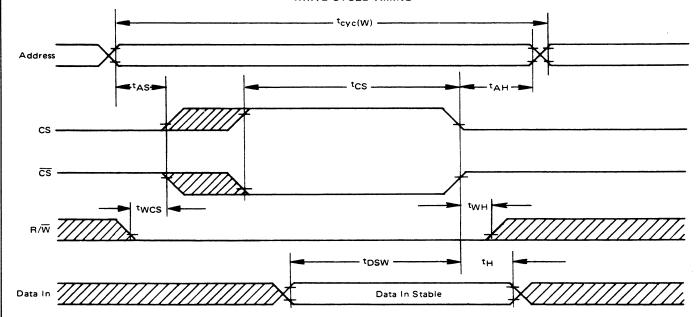

WRITE CYCLE (V<sub>CC</sub> = 5.0 V  $\pm$ 5%, V<sub>SS</sub> = 0, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub> unless otherwise noted.)

|                                  |                      | MCM6810 |     | MCM68A10 |     | MCM68B10 |     |      |

|----------------------------------|----------------------|---------|-----|----------|-----|----------|-----|------|

| Characteristic                   | Symbol               | Min     | Max | Min      | Max | Min      | Max | Unit |

| Write Cycle Time                 | t <sub>cyc</sub> (W) | 450     | -   | 360      | _   | 250      | _   | ns   |

| Address Setup Time               | <sup>t</sup> AS      | 20      | _   | 20       | _   | 20       | -   | ns   |

| Address Hold Time                | <sup>t</sup> AH      | 0       | -   | 0        |     | 0        | _   | ns   |

| Chip Select Pulse Width          | tcs                  | 300     | -   | 250      | -   | 210      |     | ns   |

| Write to Chip Select Delay Time  | twcs                 | 0       | -   | 0        | _   | 0        |     | ns   |

| Data Setup Time (Write)          | <sup>t</sup> DSW     | 190     | -   | 80       | _   | 60       | _   | ns   |

| Input Hold Time                  | tн                   | 10      | -   | 10       |     | 10       | -   | ns   |

| Write Hold Time from Chip Select | tWH                  | 0       | _   | 0        |     | 0        | _   | ns   |

#### WRITE CYCLE TIMING

# NOTES:

- 1. Voltage levels shown are  $V_L \le 0.4 \text{ V}$ ,  $V_H \ge 2.4 \text{ V}$ , unless otherwise specified. 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

- 3. CS and  $\overline{\text{CS}}$  have same timing.

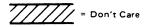

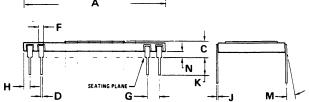

#### PACKAGE DIMENSIONS

- 1. LEADS, TRUE POSITIONED WITHIN 0.25 mm (0.010) DIA AT SEATING PLANE AT MAXIMUM MATERIAL CON DITION. (DIM. "D") 2. DIM "L" TO CENTER OF LEADS WHEN FORMED

- PARALLEL.

#### CASE 709-02 (PLASTIC)

|     | MILLIN | METERS          | INC   | HES             |

|-----|--------|-----------------|-------|-----------------|

| DIM | MIN    | MAX             | MIN   | MAX             |

| Α   | 31.37  | 32.13           | 1.235 | 1.265           |

| В   | 13.72  | 14.22           | 0.540 | 0.560           |

| C   | 4.57   | 5.08            | 0.180 | 0.200           |

| D   | 0.36   | 0.51            | 0.014 | 0.020           |

| F   | 1.02   | 1.52            | 0.040 | 0.060           |

| G   | 2.41   | 2.67            | 0.095 | 0.105           |

| H   | 1.78   | 2.03            | 0.070 | 0.080           |

| J   | 0.20   | 0.30            | 0.008 | 0.012           |

| K   | 3.05   | 3.56            | 0.120 | 0.140           |

| L   | 14.73  | 15.24           | 0.580 | 0.600           |

| M   | 00     | 10 <sup>0</sup> | 00    | 10 <sup>0</sup> |

| N   | 0.51   | 1.02            | 0.020 | 0.040           |

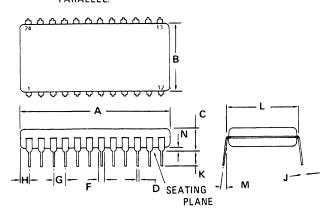

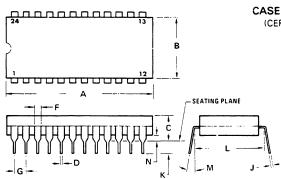

# **CASE 716-06**

(CERAMIC)

# NOTE:

1. LEADS TRUE POSITIONED WITHIN 0.25mm (0.010) DIA (AT SEATING PLANE) AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES             |  |

|-----|--------|--------|-----------|-----------------|--|

| DIM | MIN    | MAX    | MIN       | MAX             |  |

| Α   | 29.97  | 30.99  | 1.180     | 1.220           |  |

| В   | 14.88  | 15.62  | 0.585     | 0.615           |  |

| C   | 3.05   | 4.19   | 0.120     | 0.165           |  |

| D   | 0.38   | 0.53   | 0.015     | 0.021           |  |

| F   | 0.76   | 1.40   | 0.030     | 0.055           |  |

| G   | 2.54   | BSC    | 0.100 BSC |                 |  |

| Н   | 0.76   | 1.78   | 0.030     | 0.070           |  |

| J   | 0.20   | 0.30   | 800.0     | 0.012           |  |

| K   | 2.54   | 4.19   | 0.100     | 0.165           |  |

| L   | 14.88  | 15.37  | 0.585     | 0.605           |  |

| M   |        | 10°    | -         | 10 <sup>0</sup> |  |

| N   | 0.51   | 1.52   | 0.020     | 0.060           |  |

### **CASE 623-03**

(CERDIP)

|     | MILLIN    | RETERS          | INCHES |                 |  |

|-----|-----------|-----------------|--------|-----------------|--|

| DIM | MIN       | MAX             | MIN    | MAX             |  |

| А   | 31.24     | 32.77           | 1.230  | 1.290           |  |

| В   | 12.70     | 15.49           | 0.500  | 0.610           |  |

| C   | 4.06      | 5.59            | 0.160  | 0.220           |  |

| D   | 0.41      | 0.51            | 0.016  | 9.020           |  |

| F   | 1.27      | 1.52            | 0.050  | 0.060           |  |

| G   | 2.54      | 2.54 BSC 0.1    |        | BSC             |  |

| J   | 0.20      | 0.30            | 0.008  | 0.012           |  |

| K   | 2.29      | 4.06            | 0.090  | 0.160           |  |

| L   | 15.24 BSC |                 | 0.600  | BSC             |  |

| M   | Oo        | 15 <sup>0</sup> | 00     | 15 <sup>0</sup> |  |

| N   | 0.51      | 1.27            | 0.020  | 0.050           |  |

#### NOTES:

- 1. DIM "L" TO CENTER OF LEADS WHEN FORMED

- PARALLEL. 2. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE POSITION AT SEATING PLANE AT MAXIMUM MATERIAL CONDITION. (WHEN FORMED PARALLEL)

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (M) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

## **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.