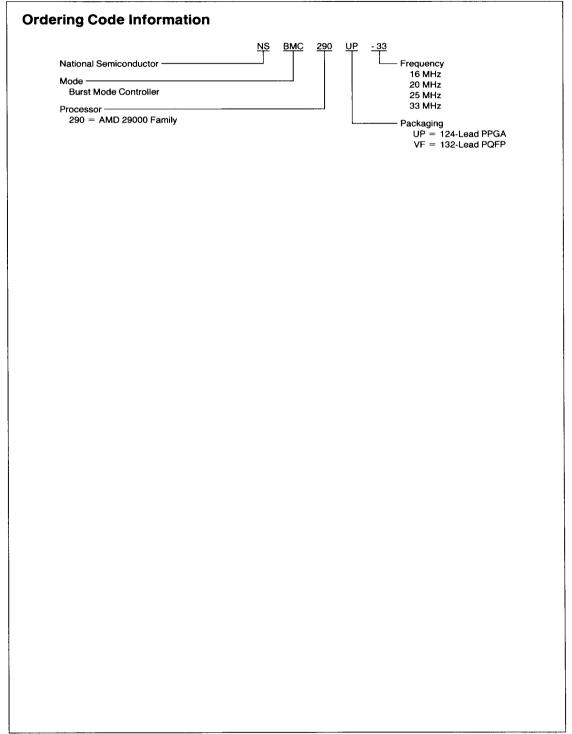

# NSBMC290<sup>™</sup>-16/-20/-25/-33 Burst Mode Memory Controller

# **General Description**

The NSBMC290 is functionally equivalent to the V29BMCTM. The NSBMC290 Burst Mode Memory Controller is a single chip device designed to simplify the implementation of burst mode access in high performance systems using the Am29000TM Streamlined Instruction Proces-

The extremely high instruction rate achieved by this processor places extraordinary demands on memory system designs if maximum throughput is to be sustained and costs minimized.

The most obvious solution to the problem of access speed is to implement system memory using high-speed static memories. However, the high cost and low density of these devices make them an expensive and space consumptive solution.

A more cost effective method of solving this problem is via the use of dynamic RAMs. Their high density and low cost make their use extremely attractive. The impediment to their use is their relatively slow access times.

However when operated in page mode, dynamic RAMs behave more like static memories. Properly managed, they can yield access times approaching those of fully static RAMs.

The function of NSBMC290 is to interface the page mode access protocol of dynamic RAMs with the more general burst mode access protocol supported by the Am29000 local channel. The device manages a double banked arrangment of dynamic RAMs such that when burst accesses are permitted data can be read, or written, at the rate of one word per system clock cycle.

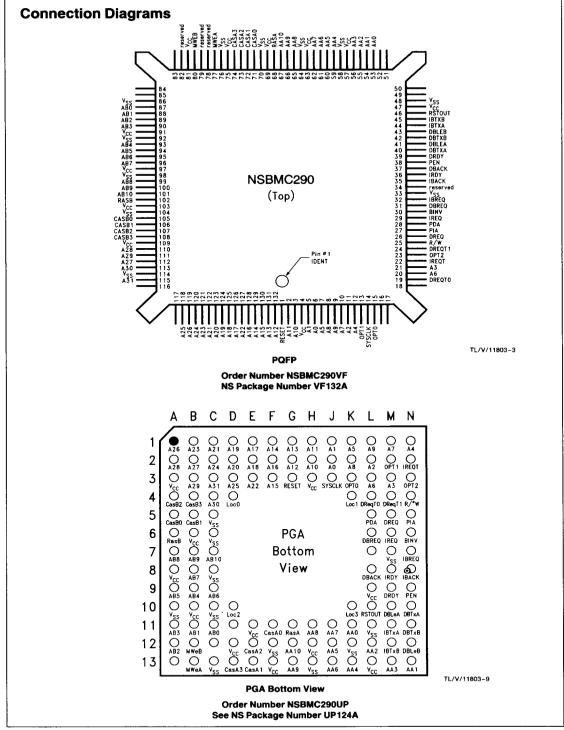

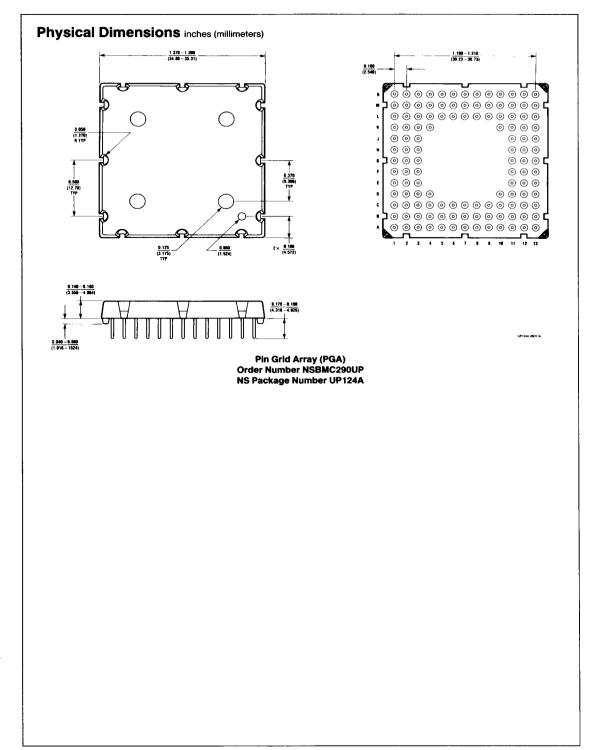

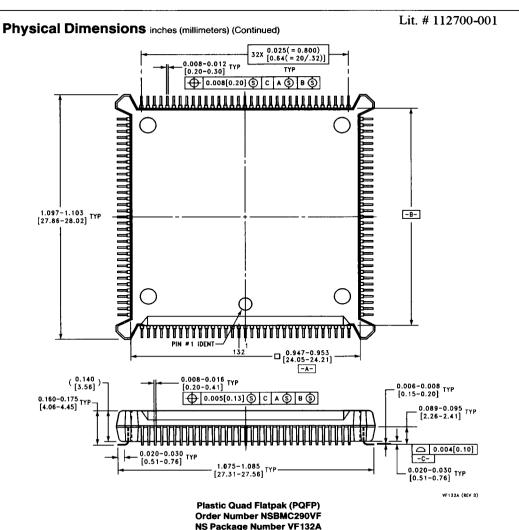

Packaged as a 124 pin PGA or 132 pin PQFP, the NSBMC290 drives memory arrays directly, thus minimizing design complexity and package count.

# **Features**

- Interfaces directly to Am29000 Local Channel

- Manages Page Mode Dynamic Memory devices

- Supports DRAMs from 64 KB to 16 MB

- Manages Instruction and/or Data Memory

- Very Low Power Consumption

- On-Chip Memory Address Multiplexer/Drivers

- Flexible Instruction/Data Bus Buffer Management

- Software-Configured operational parameters

- Auto-Configured Bank Size and Location

- High-Speed CMOS Technology

# **Block Diagram**

# **Typical System Configuration**

# A Bus Am 2900 Streamlined Instruction Processor Boot ROM SBMC290 Burst Memory Controller NSBMC290 Burst Memory Controller Instruction/Data Memory (DRAM) Instruction/Data Memory (DRAM)

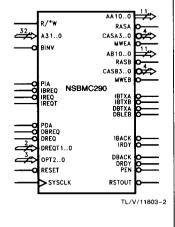

# **Logic Symbol**

This document contains information concerning a product that has been developed by National Semiconductor Corporation/V3 Corporation. This information is intended to help in evaluating this product. National Semiconductor Corporation/V3 Corporation reserves the right to change and improve the specifications of this product without notice.

TRI-STATE® is a registered trademark National Semiconductor Corporation

NSBMC290™ is a trademark of National Semiconductor Corporation

V29BMC™ is a trademark of V3 Corporation.

Am29000™ is a trademark of Advanced Micro Devices, Sunnyvale, California, USA.

1

RRD-B20M73/Printed in U. S. A

# **Pin Descriptions**

| Pin Descriptions |             |            |

|------------------|-------------|------------|

| PGA Pin          | QFP Pin     | Signal     |

| J2               | 6           | A0         |

| J1               | 5           | A1         |

| L2               | 11          | A2         |

| МЗ               | 21          | A3         |

| N1               | 12          | A4         |

| K1               | 7           | <b>A</b> 5 |

| L3               | 20          | A6         |

| M1               | 10          | A7         |

| K2               | 8           | A8         |

| L1               | 9           | A9         |

| H2               | 3           | A10        |

| H1               | 2           | A11        |

| G2               | 132         | A12        |

| G1               | 131         | A13        |

| F1               | 129         | A14        |

| F3               | 130         | A15        |

| F2               | 128         | A16        |

| E1               | 126         | A17        |

| E2               | 125         | A18        |

| D1               | 124         | A19        |

| D2               | 123         | A20        |

| C1               | 122         | A21        |

| E3<br>B1         | 127<br>121  | A22<br>A23 |

|                  | <del></del> | -          |

| C2               | 120         | A24        |

| D3               | 118         | A25        |

| A1               | 119         | A26        |

| B2               | 112         | A27        |

| A2               | 110         | A28        |

| B3               | 111         | A29        |

| C4               | 113         | A30        |

| C3               | 115         | A31        |

| K11<br>N13       | 53<br>54    | AA0<br>AA1 |

| L12              | 55          | AA2        |

| M13              | 56          | AA3        |

| K13              | 59          | AA4        |

| J12              | 60          | AA5        |

| J13              | 61          | AA6        |

| J11              | 62          | AA7        |

| H11              | 65          | AA8        |

| PGA Pin    | QFP Pin  | Signal         |

|------------|----------|----------------|

| G13        | 66       | AA9            |

| G12        | 67       | AA10           |

| C11        | 87       | AB0            |

| B11        | 88       | AB1            |

| A12        | 89       | AB2            |

| A11        | 90       | AB3            |

| B9         | 93       | AB4            |

| A9         | 94       | AB5            |

| C9         | 95       | AB6            |

| B8         | 96       | AB7            |

| A7         | 99       | AB8            |

| B7         | 100      | AB9            |

| C7         | 101      | AB10           |

| N6         | 30       | BINV           |

| F11        | 71       | CASA0          |

| E13        | 72       | CASA1          |

| E12        | 73       | CASA2          |

| D13        | 74       | CASA3          |

| <b>A</b> 5 | 105      | CASB0          |

| B5         | 106      | CASB1          |

| A4         | 107      | CASB2          |

| B4         | 108      | CASB3          |

| L8         | 37       | DBACK          |

| M10        | 41       | DBLEA          |

| N12        | 43       | DBLEB          |

| L6         | 31       | DBREQ          |

| N10        | 40       | DBTXA          |

| N11        | 42       | DBTXB          |

| M9         | 39       | DRDY           |

| M5         | 26       | DREQ           |

| L4         | 19       | DREQT0         |

| M4         | 24       | DREQT1         |

| N8         | 35       | IBACK          |

| N7         | 32       | IBREQ          |

| M11<br>M12 | 44<br>45 | IBTXA<br>IBTXB |

|            |          | -              |

| M8         | 36       | IRDY           |

| M6         | 29       | IREQ           |

| N2<br>B13  | 22<br>77 | IREQT<br>MWEA  |

|            |          |                |

| PGA Pin | QFP Pin | Signal          |

|---------|---------|-----------------|

| K3      | 15      | OPT0            |

| M2      | 13      | OPT1            |

| N3      | 23      | OPT2            |

| L5      | 28      | PDA             |

| N9      | 38      | PEN             |

| N5      | 27      | PIA             |

| N4      | 25      | R/*W            |

| G11     | 68      | RASA            |

| A6      | 102     | RASB            |

| A13     | 78      | Reserved        |

| C12     | 79      | Reserved        |

| D11     | 82      | Reserved        |

| L7      | 34      | Reserved        |

| G3      | 1       | RESET           |

| L10     | 46      | RSTOUT          |

| J3      | 14      | SYSCLK          |

| A3      | 4       | Vcc             |

| A8      | 47      | V <sub>CC</sub> |

| B6      | 57      | V <sub>CC</sub> |

| B10     | 63      | Vcc             |

| D12     | 69      | V <sub>CC</sub> |

| E11     | 75      | Vcc             |

| F13     | 81      | Vcc             |

| H3      | 91      | V <sub>CC</sub> |

| H12     | 97      | V <sub>CC</sub> |

| L9      | 103     | Vcc             |

| L13     | 109     | Vcc             |

| A10     | 33      | V <sub>SS</sub> |

| C5      | 48      | V <sub>SS</sub> |

| C6      | 58      | V <sub>SS</sub> |

| C8      | 64      | V <sub>SS</sub> |

| C10     | 70      | V <sub>SS</sub> |

| C13     | 76      | V <sub>SS</sub> |

| F12     | 86      | V <sub>SS</sub> |

| H13     | 92      | V <sub>SS</sub> |

| K12     | 98      | V <sub>SS</sub> |

| L11     | 104     | V <sub>SS</sub> |

| M7      | 114     | V <sub>SS</sub> |

Note: In order for the switching characteristics of this device to be guaranteed, it is necessary to connect all of the power pins (V<sub>CC</sub>, V<sub>SS</sub>) to the appropriate power levels. The use of low impedance wiring to the power pins is required. In systems using the Am29000 with its attendant high switching rates, multi-layer printed circuit boards with buried power and ground planes are required.

# **Pin Descriptions**

# Am29000 INTERFACE

The following pins have the same function as their counterparts on the Am29000 and are designed to be connected directly to the Am29000 Synchronous Channel Interface.

| Pin      | Description                                                                                                                                                                                                                                                                                            |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A0-31    | <b>Address Bus (Input):</b> The address bus transfers byte addresses for all accesses to the memory array except in burst mode. The NSBMC290 can be software configured to any memory block address within the 4 Gbyte address range.                                                                  |  |

| BINV     | <b>Bus Invalid (Input; Active Low):</b> This input indicates that the address bus and related control signals are invalid. This signal must be 0 (high) in order for the NSBMC290 to accept any data or instruction requests.                                                                          |  |

| R/*W)    | <b>READ/*WRITE (Input):</b> This input indicates whether data is being transferred to the data bus ( <b>R/*W</b> high) or to the memory array ( <b>R/*W</b> low).                                                                                                                                      |  |

| DBACK    | Data Burst Acknowledge (Output; 3-State, Active Low): This output signals that burst mode accesses between the memory array and the data bus can be continued.                                                                                                                                         |  |

| DBREQ    | Data Burst Request (Input, Active Low): This input is used to indicate when burst mode access for data is desired.                                                                                                                                                                                     |  |

| DRDY     | Data Ready (Output; 3-State, Active Low): This output is used to signal the completion of a data access cycle.                                                                                                                                                                                         |  |

| DREQ     | Data Request (Input; Active Low): This input signal the initiation of a memory access cycle for data.                                                                                                                                                                                                  |  |

| DREQT0-1 | Data Request Type (Input, Active Low): These inputs specify the address space of the data access. They must both be 0 (low) in order for the NSBMC290 to accept a data request.                                                                                                                        |  |

| OPT0-2   | Data Options (Input; Active Low): These inputs specify the data transfer size and operating mode. The NSBMC290 responds only to cycles in which the values 0, 1, 2 are asserted. The use of these signals is compatible with the specifications for In-Circuit Emulators.                              |  |

| PDA      | Pipelined Data Access (Input; Active Low): This input indicates that the address bus has the address for the next data access prior to the completion of the present data request.                                                                                                                     |  |

| IBACK    | Instruction Burst Acknowledge (Output; 3-State, Active Low): This output signals that burst mode accesses between the memory array and the instruction bus can be continued.                                                                                                                           |  |

| IBREQ    | Instruction Burst Request (Input; Active Low): This input is used to request burst mode instruction access.                                                                                                                                                                                            |  |

| IRDY     | Instruction Ready (Output; 3-state, Active Low): This output signals are completion of each instruction access.                                                                                                                                                                                        |  |

| IREQ     | Instruction Request (Input; Active Low): This input signals the beginning of an instruction access cycle.                                                                                                                                                                                              |  |

| IREQT    | Instruction Request Type (Input; Active High): This input specifies the address space of the instruction access. It must be 0 (low) in order for the NSBMC290 to accept an instruction request.                                                                                                        |  |

| PIA      | Pipelined Instruction Access (input; Active Low): This input indicates that the address bus has the address for the next instruction access prior to the completion of the present instruction request.                                                                                                |  |

| PEN      | Pipeline Enable (Output; 3-State, Active Low): This output indicates that the NSBMC290 is capable of accepting the address for the next access before completion of the present access.                                                                                                                |  |

| RESET    | Reset (Input; Active Low): This input initializes the NSBMC290 to accept the software configuration information If more than one NSBMC290 is used for controlling memory, the NSBMC290 chips should be daisy chained with RSTOUT from one NSBMC290 chip connecting to RESET of the next NSBMC290 Chip. |  |

| RSTOUT   | Reset Out (Output; Active Low): This output is active (low) whenever RESET is active and remains active until the NSBMC290 has been software configured.                                                                                                                                               |  |

| SYSCLK   | System Clock (Input): This input is used to synchronize the NSBMC290 to the Am29000 local channel interface.                                                                                                                                                                                           |  |

# Pin Descriptions (Continued)

# MEMORY INTERFACE

The NSBMC290 is designed to drive a memory array organized as 2 banks each of 32 bits. The address and control signals for the memory array are output through high current

drivers in order to minimize the propagation delay due to memory input impedance and trace capacitance. External array drivers are not required. The address and control signals, however, must be externally terminated.

| Pin         | Description                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(A,B)0-10  | Multiplexed Addresses (Output; High Current): These two buses transfer the multiplexed row and column addresses to the memory array banks A and B respectively.                                                                                                                |

| RAS(A,B)    | Row Address Strobes (Output; High Current, Active Low): These signals are strobes that indicate the existence of a valid row address on A(A,B)0-10. These signals are to be connected to the two interleaved banks of memory. One is assigned to each bank.                    |

| CAS(A,B)0-3 | Column Address Strobe (Output; High Current, Active Low): These signals are strobes that indicate a valid column address on A(A,B)0-10. A set of each of these (A,B) are assigned to each memory bank, and within each set, one is assigned to each byte of the 32-bit memory. |

| MWE(A,B)    | Memory Write Enable (Output; High Current, Active Low): These signals are the write strobes for the DRAM memories. One is supplied for each of the two banks of memory although they are logically identical.                                                                  |

# **BUFFER CONTROLS**

In order not to limit system implementation strategies vis à vis instruction and data bus organization, the NSBMC290 permits the designer to keep these busses separate or not

as performance criteria dictate. In order to maintain bus separation, data buffers are required. In order to maximize performance, these buffers are controlled directly by the NSBMC290.

| Pin       | Description                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBLE(A,B) | Data Bus Latch Enable A and B (Output; Active High): These outputs are used to enable transparent latches to latch data from the Processor data bus to each bank of memory during a write cycle (Data access only).               |

|           | The following buffer control outputs are multi-mode signals. The signal names, as they appear on the logic symbol are the default signal names (Mode = 0). A more complete description is presented in the configuration section. |

| DBTX(A,B) | Data Bus Transmit A and B (Output; Active Low): These outputs are used during read cycles to enable data from the individual banks of memory to drive the data bus.                                                               |

| IBTX(A,B) | Instruction Bus Transmit A and B (Output; Active Low): These outputs are used during instruction cycles to enable data from the individual banks of memory to drive the instruction bus.                                          |

# **Functional Description**

# PRODUCT OVERVIEW

The NSBMC290 is designed to simplify the interface between the Am29000 high-speed synchronous channel and dynamic memories. This integrated circuit responds to all defined instruction and data access modes of the Am29000 and handles all required address decoding and multiplexing for the DRAM memory array. In addition, the NSBMC290 automatically generates refresh cycles to the memory array. Software configuration is used to setup the memory block address, refresh rate, byte order, bus buffer control type and DRAM memory chip size parameters for the NSBMC290. If two or more memory blocks are used to implement an Am29000 memory sub-system, the processor can simultaneously access one memory block via the data bus and a second memory block via the instruction bus. If both accesses are directed to the same memory block the NSBMC290 will hold off the second access until the first has completed; only then will it process the second access.

# SYSTEM INTERFACE

The NSBMC290 connects directly to the Am29000 address bus, instruction and data bus controls signals. The interface handles simple, pipelined and burst mode access for both the data and instruction bus, according to the Am29000 channel specification. It requires no external logic to implement the synchronous channel connection. Thus, it avoids the propagation delays and signal skews that can detract from system performance and increase system complexity.

# **MEMORY INTERFACE**

The NSBMC290 directly drives an array of DRAM devices which can support page mode accesses. The array is organized as 2 banks of 32 bits each. The supported devices are all the standard memory size from 64 Kbit to 16 Mbit. Selection of the device in use is done via software.

During burst accesses, the NSBMC290 executes interleaved page mode accesses to 2 banks. This allows the memory to run at the full processor speed of 1 memory cycle per processor cycle. For data accesses, the NSBMC290 controls the memory as four independent of 8-bit bytes in order to allow 8-, 16- and 32-bit accesses.

The byte order for interpreting the byte address is software configurable. However, the NSBMC290 does not detect if the access overflows a word boundary. The software operating on the Am29000 should manage the correct alignment for memory accesses that are not word aligned. Systems using Am29000 processors whose revision level is previous to Revision "C" must manage alignment of byte data through software so that the data will retain correct justification.

The NSBMC290 allows for flexibility in the control of instruction and data buffers for the memory array. Propagation delay is minimized by providing these controls directly, and by allowing the control strategy to be software programmable. For example 74F245 or high current Am29861 bus buffers may be used without external "glue" circuitry.

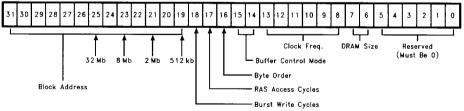

### CONFIGURATION

The NSBMC290 is configured by the first 32-bit memory read access following deassertion of the RESET signal. If multiple NSBMC290 devices are used in a circuit, they should be daisy chained together with RSTOUT from one chip connecting to RESET of the next chip. When a NSBMC290 has been configured, it deasserts the RSTOUT signal allowing the next NSBMC290 in the chain to then be configured. All NSBMC290 devices must be configured before memory accesses are attempted.

FIGURE 1. NSBMC290 Configuration Word

TL/V/11803-4

# Functional Description (Continued)

### BLOCK ADDRESS

Once configured, a NSBMC290 only responds to addresses within the block address range configured. The programmed value corresponds to the starting address of the block, while the size of the block is determined by the size of the devices used. For example, if 1M x 1 DRAM devices are selected, the memory block size is 8M bytes and is always located on an 8M byte boundary. Figure 1 shows the least significant bit of the block address for each block size.

# BYTE ORDER

When bit 16 of the configuration word is set to 0, the convention used for numbering sequential bytes in a word is that byte address 0 selects bits 0–7, byte address 1 selects bits 8–15 and so on. If bit 16 of the configuration word is set to 1, this ordering is reversed and byte address 0 selects 24–31 etc. The bit order of data within a byte is unaffected by the byte order selected. This feature facilitates the implementation of multi-processor systems in which programmable Big/Little Endian byte order is not supported by all processors.

# **BURST WRITE CYCLES**

The NSBMC290 supports instruction and data reads at a rate of one access per SYSCLK cycle during bursts. However, the flexibility of the data buffer strategy is such that buffer and memory device combinations may be selected for which the data hold time during single clock write cycles cannot be guaranteed across all system operating conditions of temperature and voltage. A two clock write cycle has thus been provided in order to support these combinations. Configuration Bit 18 is set to 0 if a two clock data burst write cycle is required, 1 if single clock write cycle is possible. The NSBMC290 Application Guide details the factors that influence the selection of this parameter.

# RAS ACCESS CYCLES

To maximize the choice of memory device speeds that may be used with various system clock rates, the NSBMC290 can be configured such that the Row Address Strobe (RAS) period lasts for either 3 or 4 clock periods during simple accesses. When set to 1, configuration bit 17 indicates that 3 clock cycles are to be used, when set to 0, 4 are required. Calculation of the number of cycles required is detailed in the NSBMC290 Application Guide.

### BUFFER CONTROL MODES

The combination of programmable RAS period and burst write cycle duration permit the system designer to trade memory device speed and organization in order to optimize system performance, cost, and storage capacity. This flexibility is further enhanced by providing multiple methods of buffering the memory sub-system and the Am29000 Local Channel.

TABLE I. Interpretation of the Buffer Control Signals for Various Control Modes

| Modes Bits | Signal 1 | Signal 2 | Signal 3 | Signal 4 |

|------------|----------|----------|----------|----------|

| 00         | DBTxA    | DBTxB    | IBTxA    | IBTxB    |

| 01         | DBCeA    | DBCeB    | IBTxA    | IBTxB    |

| 10         | DBTx     | BankB/*A | IBTx     | IBTx     |

| 11         | DBCe     | BankB/*A | IBTx     | IBTx     |

Note: The mode 00 signal names are the defaults used for reference purposes.

The transfer of Instructions and Data from the memory subsystem to the Local Channel occurs through buffers controlled by the NSBMC290. Of the six signals provided for this purpose, four operate in multiple modes; the remaining two (DBLeA, DBLeB) have fixed interpretation. These two signals provide latch enable controls for transparent latches for use during data transfers from the Am29000 to memory.

The functions performed by the remaining four signals change according to the programmed mode. Table I presents these signals using names that are function derived. Signals with a DB prefix are used to control Data Bus operations while those starting with IB control instruction bus operations. Signals containing TX are Buffer transmit controls which are typically used with buffers that have output enables (transmit relative to the memory system). Buffers such as 74F245 or 74F646 which have direction and enable pins are controlled with a CE (chip enable) signal (DBCE, DBCEa, DBCEb).

Signals ending with A or B are specific to one or the other of the two interleaved banks of memory controlled by the NSBMC290; signals without suffixes apply to both banks. The signal BankB/\*A, required in some configurations, indicates which DRAM memory bank will be next selected.

# Functional Description (Continued)

TABLE II. Buffer Control Signals and the Memory Bank for Which they are active

|                   | Simple/Pipeline Cycle                                |       | Burst Cycle  | Cycle         |

|-------------------|------------------------------------------------------|-------|--------------|---------------|

| Signal Name       | Read                                                 | Write | Read         | Write         |

| DBTX              | A,B                                                  |       | A,B (Note 1) |               |

| DBTXa             | Α                                                    |       | A (Note 2)   |               |

| DBTXb             | В                                                    |       | B (Note 2)   |               |

| DBCE              | A,B                                                  | A,B   | A,B (Note 1) | A,B (Note 1)  |

| DBCEa             | Α                                                    | Α     | A (Note 2)   | A, B (Note 1) |

| DBCEb             | В                                                    | В     | B (Note 2)   | A,B (Note 1)  |

| IBTX              | A,B                                                  |       | A,B (Note 1) |               |

| IBTXa             | A                                                    |       | A (Note 2)   |               |

| IBTXb             | В                                                    |       | B (Note 2)   |               |

| BankB/*A (Note 3) | 1 = Memory Bank B is next active, 0 = Bank A is next |       |              |               |

Note 1: Remains active over the entire burst cycle regardless of the bank being accessed.

Note 2: Asserted only when the specific bank is being accessed.

Note 3: Must be externally synchronized to SYSCLK.

The memory buffer strategy required will depend on the type of DRAMs being used (bit wide vs nibble wide components), the access time of these memories, the desired burst write speed, and the system clock speed. Table III presents some of the possible configurations with the corresponding mode settings. For a comprehensive discussion of the selection of a buffer strategy, lease refer to the NSBMC290 Application Guide. This document expands the rationale of the selection process and presents specific application examples and circuit diagrams.

TABLE III. Possible NSBMC290 Memory/Buffer Configurations

| Buffer Type    | DRAM<br>Organization | Burst<br>Write | BMC<br>Buffer Mode |

|----------------|----------------------|----------------|--------------------|

| 74F245         | Nibble               | 2 Cycle        | Mode 3             |

| 74F245         | Bit                  | 2 Cycle        | Mode 1             |

| 74F245, 74F646 | Nibble               | 1 Cycle        | Mode 3             |

| 74F245, 74F646 | Bit                  | 1 Cycle        | Mode 1             |

| Am29C983       | Bit                  | 1 Cycle        | Mode 2             |

| 29827, 29861   | Bit                  | 2 Cycle        | Mode 0             |

# SYSTEM CLOCK FREQUENCY

The system clock frequency is used to derive the period of DRAM refresh cycles. The refresh rate is given by (system clock frequency)/(16 x (programmed value + 1)). This meets the nominal refresh requirements for DRAM devices. For

example, if the system clock is 25 MHz and the programmed value is 24, the NSBMC20 will execute the 256 refresh cycles for a 256k DRAM in 4.096 ms. Bit 13 of the configuration word in the MSB of the frequency field while bit 8 is the LSB. The refresh algorithm employed by the NSBMC290 guarantees the time for complete device refresh, however, the time for individual row refreshes may be held off to prevent the preemption of a burst.

### DRAM SIZE

This two bit field, bit 7 and bit 6, configures the NSBMC290 for the correct memory address size, and hence total memory block size. Note that the memory in both banks of the block are required to be of the same size, and organization in order for correct operation to occur. Table IV lists the supported device sizes.

TABLE IV. Size Code Settings, DRAM Density and Address Range Size

| Memory<br>Size Code<br>(in Bits 7, 6) | DRAM<br>Address Size  | Memory<br>Block Size |

|---------------------------------------|-----------------------|----------------------|

| 0                                     | 64 kB x 1 64 kB x 4   | 512 KBytes           |

| 1                                     | 256 kB x 1 256 kB x 4 | 2 MBytes             |

| 2                                     | 1 MB x 1 1 MB x 4     | 8 MBytes             |

| 3                                     | 4 MB x 1 4 MB x 4     | 32 MBytes            |

# Functional Description (Continued)

# INTERCONNECT DETAILS

The NSBMC290 may be applied in designs where instruction and data memories are separated **or** in designs where a single memory space is used for both instruction and data. In split instruction/data designs, the control signals for the address space **not** required are simply pulled up to V<sub>CC</sub> levels and not connected to the corresponding local channel signals.

TABLE V. Control Signal Set Unique to Instruction Accesses

| Signal Type Signal Names |                              |  |

|--------------------------|------------------------------|--|

| Input                    | IREQ, IBREQ, IREQT, PIA      |  |

| Output                   | IBACK, IRDY                  |  |

| Buffer Control           | IBTXA, IBTXB, IBTX, BANKB/*A |  |

# TABLE VI. Control Signal Set Unique to Data Accesses

| Signal Type    | Signal Names                              |

|----------------|-------------------------------------------|

| Input          | DREQ, DBREQ, DREQT[10],<br>OPT[20] PDA    |

| Output         | DBACK, DRDY                               |

| Buffer Control | DBCEA,B, DBCE, DBTXA,B,<br>DBTX, BANKB/*A |

For mixed instruction and data designs, all local channel signals must be connected. Tables V and VI detail the control signal sets required for the NSBMC290 to control the corresponding address spaces. It is recommended that all control signals be connected and that instruction and data space segregation be done via software allocation and/or use of the Am29000 internal Translation Look-Aside Buffer.

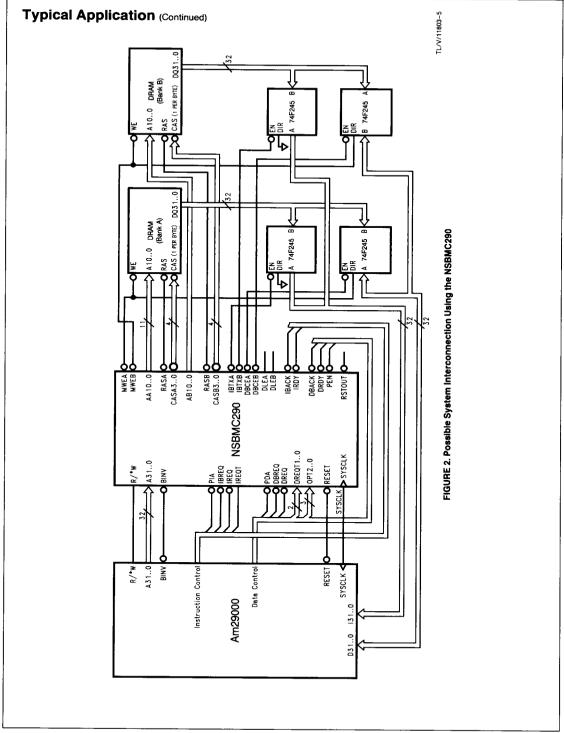

# **Typical Application**

# SYSTEM IMPLEMENTATION AND DESIGN

The ease with which the NSBMC290 may be integrated into a system design is illustrated in the diagram in *Figure 2*. The system shown supports an Am29000 with between 2 MB and 32 MB of memory (depending on the storage devices selected) managed by a single NSBMC290. This specific example accommodates 256k x 1, 1 MB x 1 or 4 MB x 1 devices

In a minimal system configuration only one NSBMC290 is required. This is because the NSBMC290 manages both instruction and data access to a memory block. However, with a single memory block, instruction and data accesses cannot be overlapped and the number of burst access restarts is a function of the way in which the software is designed. It is therefore difficult to predict performance degradation.

If maximum performance is required, the addition of one or more NSBMC290s is an effective solution. Our bench marks indicate that for systems with physically separated instruction and data space performance is degraded by approximately 5% over the theoretical rate achieved in system designs employing high speed static RAMs. The device count and cost of these solutions, however, differ by at least a factor of 6.

With the exception of data buffers external components are not required, except to terminate the address and control lines to the memory array. The use of passive components arranged in a serial or parallel terminating network is a simple but effective method of implementing this requirement.

### CPHINTERFACE

The NSBMC290 interface to the Am29000 has been designed for direct interconnect. Normally it is not necessary to place other logic devices between the processor, NSBMC290, and memory with the exception of Instruction/Data bus buffers. The introduction of intermediate buffers can result in skews or delays that will require that the system clock frequency be derated for operation under worst case conditions.

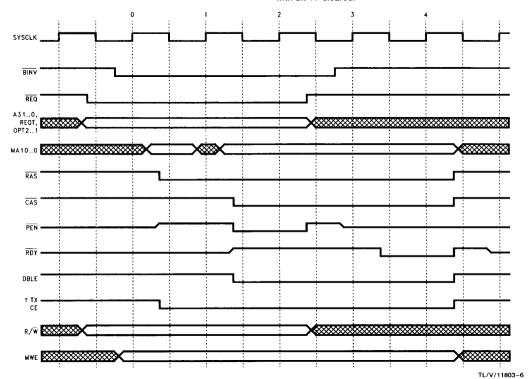

### SIMPLE ACCESS SEQUENCE

The NSBMC290 can return data to the processor in only 4 clocks or 5 clocks for a simple access depending on the mode chosen (Configuration Bit 17). If multiple access

cycles are requested back to back, then the BMC will pause for a minimum of 2 clocks between RAS cycles to insure that the RAS precharge time is met resulting in 5 clocks or 6 clocks between successive simple cycles (depending on Configuration bit 17).

All access modes begin their cycle in the same fashion as a simple access. A simple access can become either a pipelined or burst access if the appropriate inputs are driven. Figure 3 shows the timing relationship between the system clock, processor control signals and NSBMC290 outputs. All NSBMC290 outputs are derived synchronously with the exception of taRa<sup>7</sup> (processor address to memory address delay). The shaded section in Figure 3 represents the extra cycle inserted when the configuration register is initialized with bit 17 cleared.

†DBTX, DBTXa, DBTXb, DBCE, DBCEa, DBCEb, IBTX, IBTXa, IBTXb

FIGURE 3. Simple Access Sequence

# Typical Application (Continued)

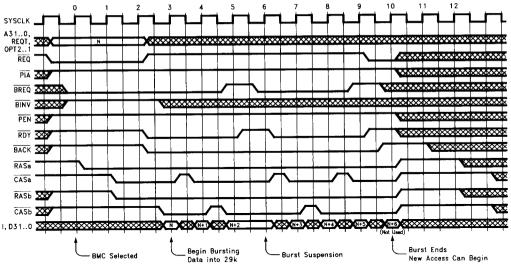

FIGURE 4. Burst Read Sequence (Illustrating Burst Suspension)

TL/V/11803-8

### BURST ACCESS SEQUENCE

When Burst access has been established, the NSBMC290 generates the signal sequence of Figure 5. This access sequence will continue until either canceled or suspended by the Am29000 or normal burst termination occurs. The NSBMC290 will preempt the burst sequence only in the case that a refresh cycle has been requested, and has been outstanding for a time in excess of 80% of the refresh period

# **FUNCTIONAL OVERVIEW OF BURST ACCESS**

Figure 4 diagrams the sequence of events that take place during a typical burst sequence. This specific example describes the operations surrounding instruction or data reads. The example illustrates how burst operation is established, suspended for a cycle, and subsequently terminated by the master.

The sequence commences at  $T_0$  when the NSBMC290 is selected. Once selected, the BMC drives RAS of the memory bank which contains data for the initial access of the burst cycle (Bank A in this case). During the next period ( $T_1$ ), CASa is asserted and the RAS for the other memory bank (RASb) is activated. Access to the second memory bank is offset by one cycle in order that bank interleave will occur correctly.

The first word of data is available to the processor by  $T_3$  as indicated by RDY asserted. Data from the memory must propagate through any data buffers and meet the setup time of the 29k processor by  $T_3$ . An extra cycle is inserted into the start-up phase of the burst sequence if bit 17 of the configuration register is programed to "0". This increases the RAS assertion time from 3 cycles to 4 cycles. The resulting delay is inserted during  $T_2$ .

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>)

-0.3V to +7V

Input Voltage (V<sub>IN</sub>)

Storage Temperature (T<sub>STG</sub>)

-0.3V to  $V_{CC} + 0.3V$

DC Input Current (I<sub>IN</sub>)

± 50 mA

-65°C to + 150°C

# Recommended Operating Conditions

Supply Voltage (V<sub>CC</sub>)

4.75V to 5.25V

Ambient Temperature (T<sub>A</sub>)

Plastic Package Ceramic Package 0°C to +70°C

-55°C to +85°C

# **DC Electrical Characteristics**

| Symbol           | Description                         | Description Conditions                                        |     | Max       | Units |  |

|------------------|-------------------------------------|---------------------------------------------------------------|-----|-----------|-------|--|

| $V_{IL}$         | Low Level Input Voltage             | V <sub>CC</sub> = 4.75V                                       |     | 0.8       | V     |  |

| V <sub>IH</sub>  | High Level Input Voltage            | V <sub>CC</sub> = 5.25V                                       | 2.0 |           | V     |  |

| I <sub>IL</sub>  | Low Level Input Current             | $V_{IN} = V_{SS}, V_{CC} = 5.25V$                             | -10 |           | μА    |  |

| l <sub>IH</sub>  | High Level Input Current            | $V_{IN} = V_{CC} = 5.25V$                                     |     | 10        | μΑ    |  |

| V <sub>OL</sub>  | Low Level Output Voltage            | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $I_{OL} = 24 \text{ mA}$ |     | 0.4       | V     |  |

| V <sub>OH</sub>  | High Level Output Voltage           | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $I_{OL} = 24 \text{ mA}$ | 3.7 |           | ٧     |  |

| lozL             | Low Level TRI-STATE® Output Current | $V_{IN} = V_{IL} \text{ or } V_{IH}$ $V_O = V_{SS}$           | -20 |           | μА    |  |

| lozн             | Low Level TRI-STATE Output Current  | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$V_{O} = 5.25V$       |     | 20        | μΑ    |  |

| ICC(Max)         | Maximum Supply Current              | Continuous Simple Access<br>Continuous Burst Access           |     | 100<br>30 | mA    |  |

| CIN              | Input Capacitance                   |                                                               |     | 20        | рF    |  |

| C <sub>OUT</sub> | Output Capacitance                  |                                                               |     | 20        | pF    |  |

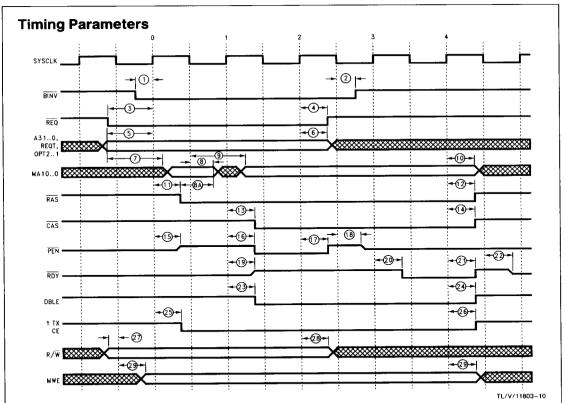

†DBTX, DBTXa, DBTXb, DBCE, DBCEa, DBCEb, IBTX, IBTXa, IBTXb

FIGURE 5. Simple Access Timing

# AC Timing Parameters (Unless otherwise stated V<sub>CC</sub> = 5.0V $\pm$ 5%, 0°C < T<sub>A</sub> < 70°C.)

| # Symbol | Description        | 16 MHz                                                              |                     | 20 MHz |                     | 25 MHz |                     | 33 MHz |                     | Units |          |

|----------|--------------------|---------------------------------------------------------------------|---------------------|--------|---------------------|--------|---------------------|--------|---------------------|-------|----------|

|          | Jy001              | Description                                                         | Min                 | Max    | Min                 | Max    | Min                 | Max    | Min                 | Max   | Units    |

| 1        | t <sub>BSU</sub>   | BINV Setup                                                          | 8                   |        | 7                   |        | 6                   |        | 5                   |       | ns       |

| 2        | t <sub>BH</sub>    | BINV Hold                                                           | 4                   | ŀ      | 3                   |        | 3                   |        | 2                   |       | ns       |

| 3        | tRQSU              | Request Sync. Setup Time                                            | 17                  |        | 13                  |        | 12                  |        | 10                  |       | ns       |

| 4        | t <sub>RQH</sub>   | Request Sync. Hold Time                                             | 4                   |        | 3                   |        | 3                   |        | 2                   |       | ns       |

| 5        | tsu                | Synchronous Input Setup                                             | 17                  |        | 13                  |        | 12                  |        | 10                  |       | ns       |

| 5A       | ts∪                | Synchronous Input Setup I/DBREQ only                                | 9                   |        | 8                   |        | 6                   |        | 4.5                 |       | ns       |

| 6        | t <sub>H</sub>     | Synchronous Input Hold                                              | 4                   |        | 3                   |        | 3                   |        | 2                   |       | ns       |

| 6A       | t <sub>BRH</sub>   | *SYSCLK to Burst Request Input Hold                                 | 4                   |        | 3                   |        | 3                   |        | 2                   |       | ns       |

| 7        | tARA               | Address Input to Row Address output delay                           |                     | 29     |                     | 24     |                     | 22     |                     | 18    | ns       |

|          |                    | (Note 1)                                                            | _                   |        | _                   |        | _                   |        | _                   |       | ĺ        |

| 8        | <sup>t</sup> RAH   | *SYSCLK to row address hold                                         | 9                   |        | 8                   |        | 7                   |        | 6                   |       | ns       |

| 8A       | <sup>t</sup> DRAH  | DRAM Row Address Hold (Note 2)                                      | t <sub>CLK</sub> -4 |        | t <sub>CLK</sub> -4 |        | t <sub>CLK</sub> -3 |        | t <sub>CLK</sub> -2 | ١     | ns       |

| 9        | tCAV               | *SYSCLK to Column Address Valid Delay (Note 1)                      | ]                   | 38     |                     | 32     |                     | 29     |                     | 24    | ns       |

|          |                    |                                                                     |                     |        |                     |        |                     | -      |                     |       |          |

| 10<br>11 | t <sub>CAH</sub>   | SYSCLK to Column Address Hold SYSCLK to RAS Asserted Delay (Note 1) | 6                   | 26     | 6                   | 22     | 5                   | 20     | 5                   | 17    | ns       |

| 12       | <sup>t</sup> RSHL  | SYSCLK to RAS De-asserted Delay (Note 1)                            |                     | 23     |                     | 19     |                     | 17     |                     | 14    | ns       |

| 13       | t <sub>RSLH</sub>  | SYSCLK to CAS Asserted Delay (Note 1)                               |                     | 32     | İ                   | 27     |                     | 24     |                     | 20    | ns<br>ns |

| 14       | t <sub>CHL</sub>   | SYSCLK to CAS Asserted Delay (Note 1)                               |                     | 40     | 1                   | 33     |                     | 30     |                     | 25    | ns       |

| 15       | t <sub>PZH</sub>   | PEN 3-state to Valid Delay Relative to                              | 1                   | 30     |                     | 25     |                     | 23     |                     | 19    | ns       |

|          | PZH                | *SYSCLK                                                             |                     | 30     |                     | 23     |                     | 23     |                     | '3    | 113      |

| 16       | t <sub>PHL</sub>   | PEN Synchronous Assertion Delay                                     |                     | 26     |                     | 22     |                     | 20     |                     | 17    | ns       |

| 17       | t <sub>PLH</sub>   | PEN Synchronous Deassertion Delay                                   |                     | 25     |                     | 21     |                     | 19     |                     | 16    | ns       |

| 18       | t <sub>PHZ</sub>   | PEN Valid to 3-state Delay Relative to<br>*SYSCLK                   |                     | 29     |                     | 24     |                     | 22     |                     | 18    | ns       |

| 19       | t <sub>RZH</sub>   | RDY 3-state to Valid Delay Relative to  *SYSCLK                     |                     | 30     |                     | 25     |                     | 23     |                     | 19    | ns       |

| 20       | t <sub>RHL</sub>   | RDY Synchronous Assertion Delay                                     |                     | 26     |                     | 22     |                     | 20     |                     | 17    | ns       |

| 21       | t <sub>RLH</sub>   | RDY Synchronous De-assertion Delay                                  |                     | 25     |                     | 21     |                     | 19     |                     | 16    | ns       |

| 22       | t <sub>RHZ</sub>   | RDY Valid to 3-state Delay Relative to *SYSCLK                      |                     | 29     |                     | 24     |                     | 22     |                     | 18    | ns       |

| 23       | tLEHL              | Synchronous Latch Enable Assertion delay                            |                     | 32     |                     | 27     |                     | 24     | 1                   | 20    | ns       |

| 24       | tLELH              | Synchronous Latch Enable De-assertion Delay                         |                     | 42     |                     | 35     |                     | 32     | j                   | 26    | ns       |

| 25       | t <sub>BHL</sub>   | Synchronous Buffer Enable Assertion Delay                           |                     | 49     |                     | 41     |                     | 37     |                     | 31    | ns       |

| 26       | t <sub>BLH</sub>   | Synchronous Buffer Enable De-assertion Delay                        |                     | 38     |                     | 32     |                     | 29     |                     | 24    | ns       |

| 27       | trwsu              | Synchronous R/*W Input Setup Time                                   | 8                   |        | 7                   |        | 6                   |        | 5                   |       | ns       |

| 28       | t <sub>RWH</sub>   | Synchronous R/*W Input Hold Time                                    | 4                   |        | 3                   |        | 3                   |        | 2                   |       | ns       |

| 29       | twev               | Synchronous Write Enable Valid Delay<br>Relative to *SYSCLK         |                     | 59     |                     | 49     |                     | 44     |                     | 37    | ns       |

| 30       | t <sub>BKZH</sub>  | Synchronous I/DBACK Valid Delay                                     |                     | 25     |                     | 21     |                     | 19     |                     | 16    | ns       |

| 31       | t <sub>BKHL</sub>  | Synchronous I/DBACK Assertion Delay                                 |                     | 29     |                     | 24     |                     | 22     |                     | 18    | ns       |

| 32       | t <sub>BKLH</sub>  | Synchronous I/DBACK Deassertion Delay                               |                     | 24     |                     | 20     |                     | 18     |                     | 15    | ns       |

| 33       | t <sub>BKHZ</sub>  | Synchronous I/DBACK Valid to 3-state Delay                          |                     | 24     |                     | 20     |                     | 18     |                     | 15    | ns       |

| 34       | t <sub>ABKLH</sub> | Asynchronous I/DBACK Deassertion delay relative to I/DREQ           |                     | 22     |                     | 18     |                     | 14     |                     | 12    | ns       |

<sup>\*</sup>Signal output delays are measured relative to SYSCLK (except as indicated) using a 50 pF load.

Note 1: Derate the given delays by 0.06 ns per pF of load in excess of 50 pF.

Note 2: Where t<sub>CLK</sub> = 1/(2 \* Clock Frequency)

†TXa = IBTXa, DBTXa; CEa = IBCEa, DBCE; TXb = IBTXb, DBTXb; CEb = IBCEb, DBCEb and BANKb/\*a.

Note: Buffer control signal timing is illustrated using the mode dependent signal naming convention. (See page 7.) As shown, the switching behavior is typical of modes 0 and 1. In modes 2 and 3 the timing of signals DBTX, DBCE and IBTX remain unchanged.

TL/V/11803-7

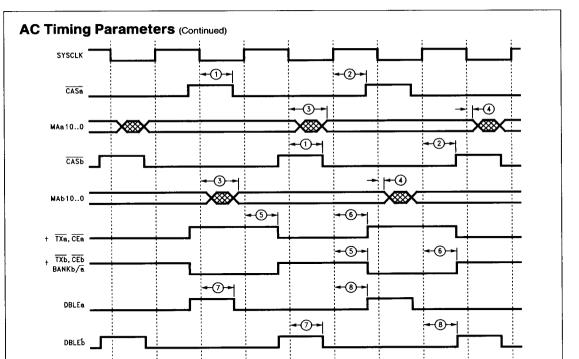

FIGURE 6. Burst Access Timing

# **TABLE VIII. Burst Access Timing Parameters**

| # Symbol | Description      | 16 MHz                                         |     | 20 MHz |     | 25 MHz |     | 33 MHz |     | Units |    |

|----------|------------------|------------------------------------------------|-----|--------|-----|--------|-----|--------|-----|-------|----|

|          | Symbol           | Description                                    | Min | Max    | Min | Max    | Min | Max    | Min | Max   |    |

| 1        | tCHL             | *SYSCLK to CAS Assertion (Note 1)              |     | 25     |     | 21     |     | 19     |     | 15.5  | ns |

| 2        | tCLH             | SYSCLK to CAS De-Assertion (Note 1)            |     | 24     |     | 20     |     | 18     |     | 15    | ns |

| 3        | tCAV             | *SYSCLK to Column Address Valid Delay (Note 1) | ļ   | 38     | 1   | 32     | İ   | 29     | 1   | 24    | ns |

| 4        | tCAH             | *SYSCLK to Column Address Hold Time (Note 1)   | 6   | 34     | 5   | 28     | 5   | 25     | 3   | 21    | ns |

| 5        | t <sub>BHL</sub> | SYSCLK to Buffer Control Assertion Delay       |     | 25     |     | 21     |     | 19     |     | 15.5  | ns |

| 6        | t <sub>BLH</sub> | *SYSCLK to Buffer Control De-Assertion Delay   |     | 24     |     | 20     |     | 18     |     | 15    | ns |

| 7        | tLEHL            | *SYSCLK to Latch Enable Assertion              |     | 26     |     | 22     |     | 20     |     | 16.5  | ns |

| 8        | tLELH            | SYSCLK to Latch Enable De-Assertion            |     | 26     |     | 22     |     | 20     |     | 16.5  | ns |

<sup>\*</sup>Signal output delays are measured relative to SYSCLK (except as indicated) using a 50 pF load.

Note 1: Derate given the delays by 0.06 ns per pF or load in excess of 50 pF.

# Release Notes for NSBMC290 Revision "A"

# A NOTE ON THE OPERATION OF THE Am29000

It is a characteristic of the Am29000 (Rev D) that it can deassert the \*IBREQ signal independently of the current state of \*IRDY and \*IBACK. The V29BMC (Rev A) accommodates this behavior in all cases with one exception.

### ERRATUM #1

If \*IBREQ is de-asserted 1 or two clock cycles before \*IRDY is returned and the instruction access cycle is followed in the next clock cycle by a data write, the write enable signals from the V29BMC to memory are asserted ½ clock cycle before \*RAS/\*CAS are de-asserted. The memory location following the last completed instruction access may be corrupted.

# RECOMMENDED FIX

The "write enables" to memory must be delay by a clock cycle. This may be achieved in the following ways:

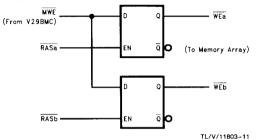

- The \*RAS signals may be used to latch the write enable from the V29BMC as shown in Figure 7.

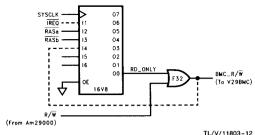

- 2. The write enable into the V29BMC may be delayed. See Figure 8.

FIGURE 7

The logic shown in *Figure 7* can be implemented in a PAL using the following positive true logic equation:

WEa = !RASa & MWE # RASa & WEA;

MWE is MWEa or MWEb since they are identical.

FIGURE 8

The PAL shown in  $Figure \ \theta$  can be programmed with one of the two following equations depending on which of the two dotted paths is connected:

RD\_ONLY.d = RASa & RASb & BMC\_R/W; or RD\_ONLY.d = RASa & RASb & IREQ:

The primary difference between the two recommended solutions is that the one given in *Figure 8* makes use of the high current drivers on the V29BMC for driving the write enable signal to the memory array. For systems using bit organized memories, this type of drive capability is desired. The "or" function implemented by the 'F32 may be moved inside the PAL by appropriately modifying the equations. For maximum performance, it should be a discrete gate as shown

This modification is only required for a V29BMC controlling memories from which instructions are being run. This modification, however implemented, will affect the timing of Pipeline Cycles. Do not connect PEN to a V29BMC whose write timing is modified, and connect PIA, PDA only to a pull-up resistor. For a V29BMC controlling data only memory, no changes to the write enable timing are required and pipeline access may be used. Using data pipelining, performance improvements of the order of 2% have been observed.

### FRRATUM #2

If buffer mode 3 (or 1) is selected, then it is possible for \*DBCE(a,b) to be asserted during a refresh cycle. This will happen if a data write cycle not accessing the BMC is followed in the next cycle by a read cycle also not accessing the BMC such that refresh on the BMC starts with the read. The result is that the data bus can be driven by the buffers controlled by the V29BMC when other devices are using it.

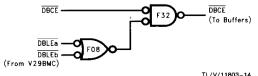

### RECOMMENDED FIX

There are a number of possible fixes of which 2 are outlined below. The first solution is to use the mode 2 (or 0) buffer control signals and generate a \*DBCE(a,b) signal from \*WE(a,b) and \*DBTX(a,b). Make sure that mode 2(or 0) operation is selected in the V29BMC configuration word.

$$\frac{\overline{WE}}{\overline{DBTX}} = \overline{DBCE}$$

(From V29BMC)

TL/V/11803-13

# FIGURE 9. Generation of \*DBCE from \*WE and \*DBTX Signals

The second solution is to use the DBCE(a,b) signal and qualify it using the DBLE signals as shown below.

TL/V/1180

FIGURE 10. Modification of \*DBCE Signal Using the V29BMC Latch Enable Signals

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Comoration 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959

TWX: (910) 339-9240

National Semiconductor Industriestrasse 10 D-8080 Fürstenfeldbruck Germany Tel: (0-81-41) 103-0 5276 Fax: (0-81-41) 10-35-06

National Semiconductor Japan Ltd. Sanseido Bldg. 5F 4-15-3 Nishi Shinjuku Shinjuku-Ku, Tokyo 160, Japan Tel: 3-3299-7001 FAX: 3-3299-7000

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 737-1600 Telex: 51292 NSHKL Fax: (852) 736-9960

National Semiconduc Do Brazil Ltda. Do Brazzi Ltda. Av. Brig. Faria Lima, 1409 6 Andar Cep-01451, Paulistano, Sao Paulo, SP, Brazil Tel: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fay: (55-11) 212-1181

Fax: (55-11) 212-1181

039020

(Australia) Pty, Ltd. 16 Business Park Dr. Notting Hill, VIC 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications