## Quad Channel, 16-Bit, Serial Input, 4 mA to 20 mA and Voltage Output DAC, Dynamic Power Control

# AD5755

### FEATURES

16-bit resolution and monotonicity

Dynamic power control for thermal management

Current and voltage output pins connectable to a single terminal

Current output ranges: 0 mA to 20 mA, 4 mA to 20 mA, or 0 mA to 24 mA ±0.05% total unadjusted error (TUE) maximum

Voltage output ranges (with 20% overrange): 0 V to 5 V, 0 V to 10 V, ±5 V, and ±10 V ±0.04% total unadjusted error (TUE) maximum

User programmable offset and gain

On-chip diagnostics

On-chip reference (±10 ppm/°C maximum) -40°C to +105°C temperature range

#### **APPLICATIONS**

Process control Actuator control PLCs

### **GENERAL DESCRIPTION**

The AD5755 is a quad, voltage and current output DAC that operates with a power supply range from -26.4 V to +33 V.

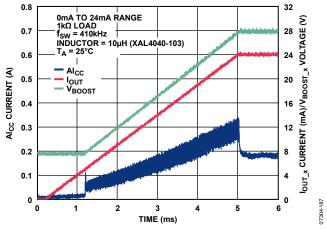

On-chip dynamic power control minimizes package power dissipation in current mode. This is achieved by regulating the voltage on the output driver from 7.4 V to 29.5 V using a dc-to-dc boost converter optimized for minimum on chip power dissipation.

The part uses a versatile 3-wire serial interface that operates at clock rates of up to 30 MHz and is compatible with standard SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup>, DSP, and microcontroller interface standards. The interface also features optional CRC-8 packet error checking, as well as a watchdog timer that monitors activity on the interface.

### **PRODUCT HIGHLIGHTS**

- 1. Dynamic power control for thermal management.

- 2. 16-bit performance.

- 3. Multichannel.

## **COMPANION PRODUCTS**

Product Family: AD5755-1, AD5757 External References: ADR445, ADR02 Digital Isolators: ADuM1410, ADuM1411 Power: ADP2302, ADP2303 Additional companion products on the AD5755 product page

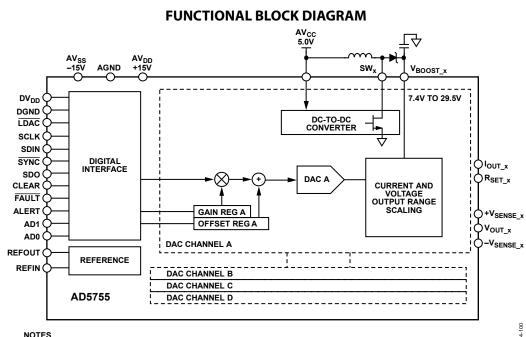

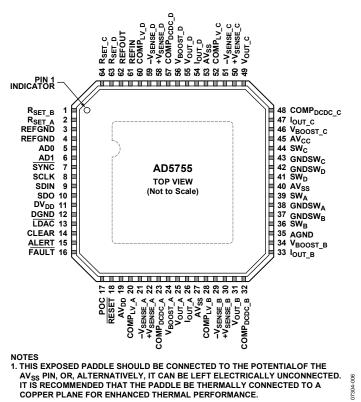

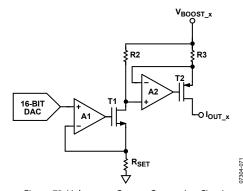

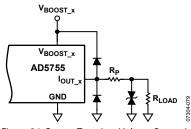

NOTES 1. x = A, B, C, AND D.

Figure 1.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2011 Analog Devices, Inc. All rights reserved.

## TABLE OF CONTENTS

| Features 1                                                   |

|--------------------------------------------------------------|

| Applications1                                                |

| General Description                                          |

| Product Highlights 1                                         |

| Companion Products1                                          |

| Functional Block Diagram 1                                   |

| Revision History                                             |

| Detailed Functional Block Diagram                            |

| Specifications                                               |

| AC Performance Characteristics7                              |

| Timing Characteristics                                       |

| Absolute Maximum Ratings11                                   |

| ESD Caution11                                                |

| Pin Configuration and Function Descriptions12                |

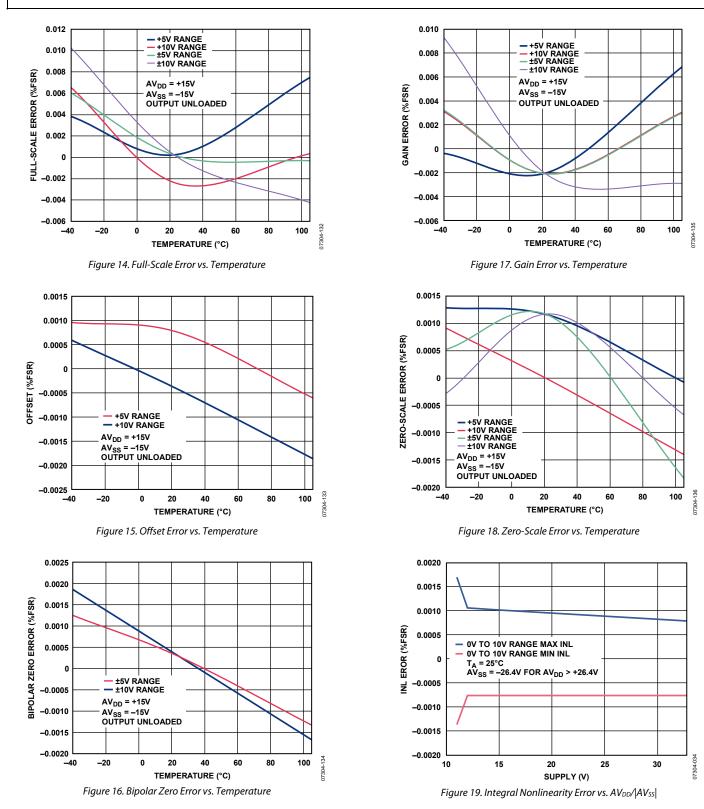

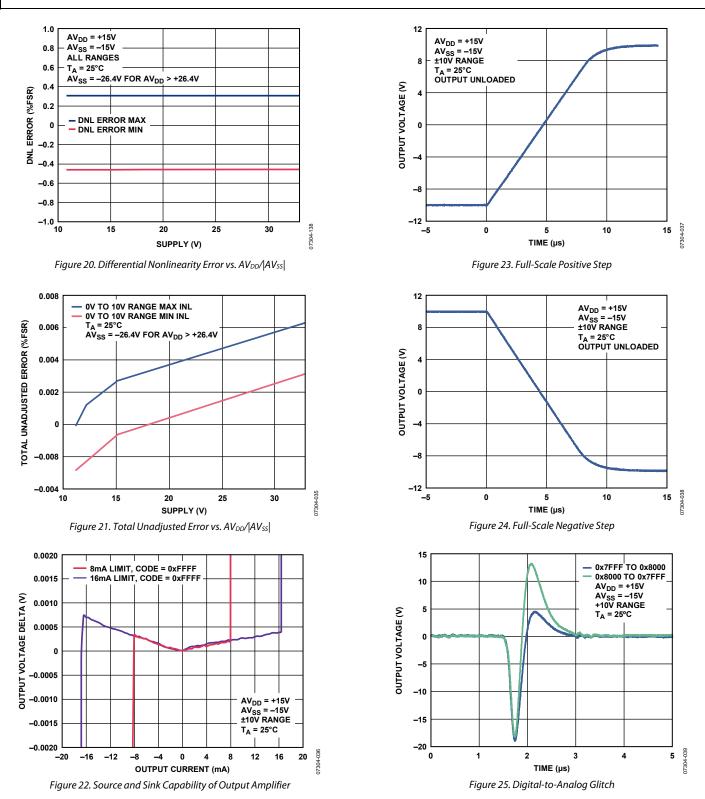

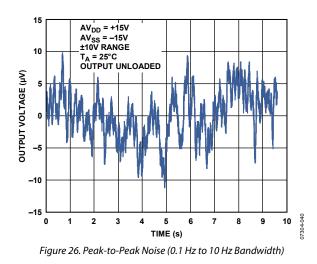

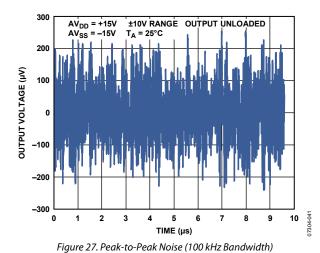

| Typical Performance Characteristics                          |

| Voltage Outputs15                                            |

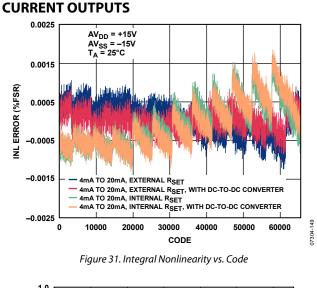

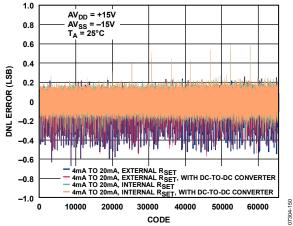

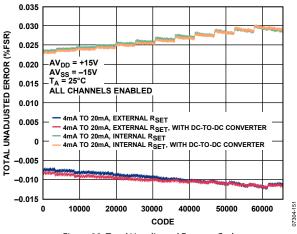

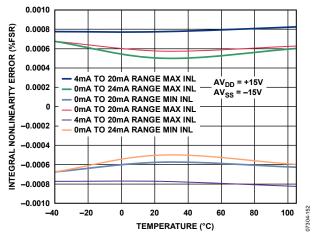

| Current Outputs                                              |

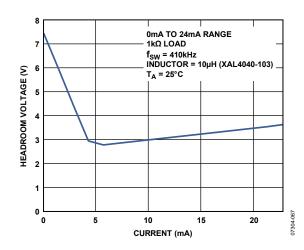

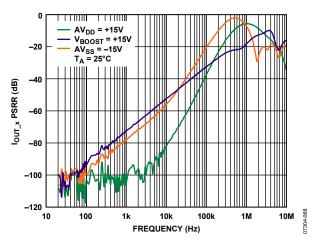

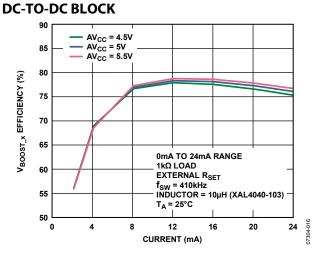

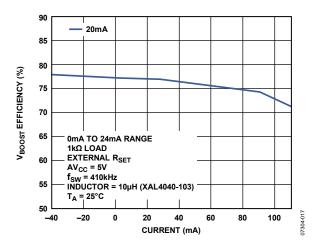

| DC-to-DC Block                                               |

| Reference                                                    |

| General                                                      |

| Terminology                                                  |

| Theory of Operation                                          |

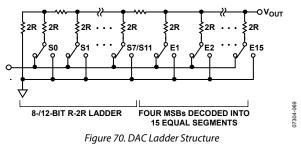

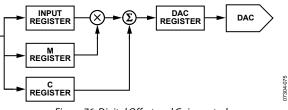

| DAC Architecture                                             |

| Power-On State of AD5755                                     |

| Serial Interface                                             |

| Transfer Function                                            |

| Registers                                                    |

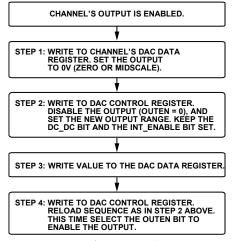

| Programming Sequence to Write/Enable the Output<br>Correctly |

| Changing and Reprogramming the Range                         |

## **REVISION HISTORY**

5/11—Revision 0: Initial Version

|   | Data Registers                                         | 32 |

|---|--------------------------------------------------------|----|

|   | Control Registers                                      | 34 |

|   | Readback Operation                                     | 37 |

| D | Pevice Features                                        | 39 |

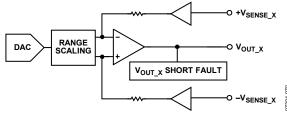

|   | Output Fault                                           | 39 |

|   | Voltage Output Short-Circuit Protection                | 39 |

|   | Digital Offset and Gain Control                        | 39 |

|   | Status Readback During a Write                         | 39 |

|   | Asynchronous Clear                                     | 40 |

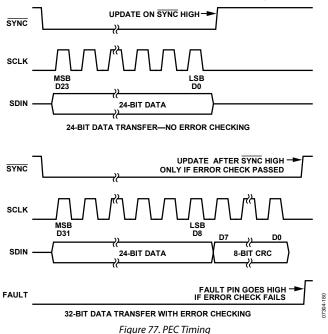

|   | Packet Error Checking                                  | 40 |

|   | Watchdog Timer                                         | 40 |

|   | Output Alert                                           | 40 |

|   | Internal Reference                                     | 40 |

|   | External Current Setting Resistor                      | 40 |

|   | Digital Slew Rate Control                              | 41 |

|   | Power Dissipation control                              | 41 |

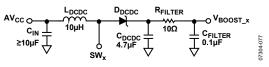

|   | DC-to-DC Converters                                    | 41 |

|   | AIcc Supply Requirements—Static                        | 43 |

|   | AI <sub>CC</sub> Supply Requirements—Slewing           | 43 |

| А | pplications Information                                | 45 |

|   | Voltage and Current Output Ranges on the Same Terminal | 45 |

|   | Current Output Mode with Internal R <sub>SET</sub>     | 45 |

|   | Precision Voltage Reference Selection                  | 45 |

|   | Driving Inductive Loads                                | 46 |

|   | Transient Voltage Protection                           | 46 |

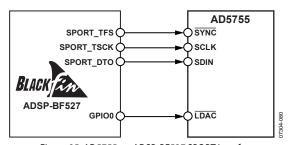

|   | Microprocessor Interfacing                             | 46 |

|   | Layout Guidelines                                      | 46 |

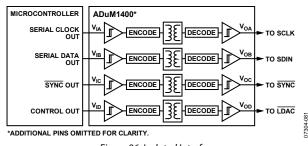

|   | Galvanically Isolated Interface                        | 47 |

| С | Putline Dimensions                                     | 48 |

|   | Ordering Guide                                         | 48 |

|   |                                                        |    |

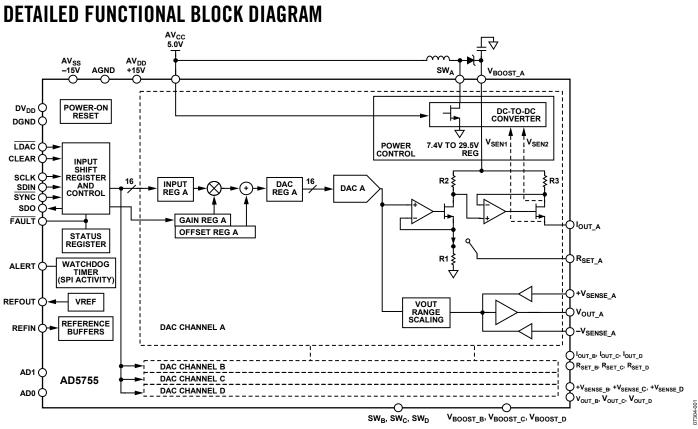

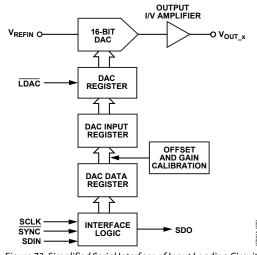

Figure 2.

## **SPECIFICATIONS**

$AV_{DD} = V_{BOOST_x} = 15 \text{ V}; AV_{SS} = -15 \text{ V}; DV_{DD} = 2.7 \text{ V}$  to 5.5 V;  $AV_{CC} = 4.5 \text{ V}$  to 5.5 V; dc-to-dc converter disabled;  $AGND = DGND = GNDSW_x = 0 \text{ V}; REFIN = 5 \text{ V};$  voltage outputs:  $R_L = 1 \text{ k}\Omega$ ,  $C_L = 220 \text{ pF};$  current outputs:  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 1.

| Parameter <sup>1</sup>              | Min    | Тур     | Max    | Unit          | Test Conditions/Comments                                                                     |

|-------------------------------------|--------|---------|--------|---------------|----------------------------------------------------------------------------------------------|

| VOLTAGE OUTPUT                      |        | 1       | 1      |               |                                                                                              |

| Output Voltage Ranges               | 0      |         | 5      | V             |                                                                                              |

|                                     | 0      |         | 10     | V             | AV <sub>DD</sub> must have minimum 2.2 V headroom on output                                  |

|                                     | -5     |         | +5     | V             |                                                                                              |

|                                     | -10    |         | +10    | V             | AV <sub>DD</sub> /AV <sub>ss</sub> must have minimum 2.2 V headroom on output                |

|                                     | 0      |         | 6      | V             |                                                                                              |

|                                     | 0      |         | 12     | V             | AV <sub>DD</sub> must have minimum 2.2 V headroom on output                                  |

|                                     | -6     |         | +6     | V             |                                                                                              |

|                                     | -12    |         | +12    | V             | AV <sub>DD</sub> /AV <sub>ss</sub> must have minimum 2.2 V headroom on output                |

| Resolution                          | 16     |         |        | Bits          |                                                                                              |

| ACCURACY                            |        | 1       | 1      |               | $AV_{SS} = -15$ V, loaded and unloaded                                                       |

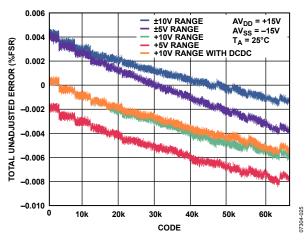

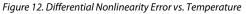

| Total Unadjusted Error (TUE)        |        |         |        |               |                                                                                              |

| B Version                           | -0.04  |         | +0.04  | % FSR         |                                                                                              |

|                                     | -0.03  | ±0.0032 | +0.03  | % FSR         | $T_A = 25^{\circ}C$                                                                          |

| A Version                           | -0.25  |         | +0.25  | % FSR         |                                                                                              |

|                                     | -0.075 | ±0.02   | +0.075 | % FSR         | $T_A = 25^{\circ}C$                                                                          |

| TUE Long-Term Stability             |        | 35      |        | ppm FSR       | Drift after 1000 hours, T <sub>J</sub> = 150°C                                               |

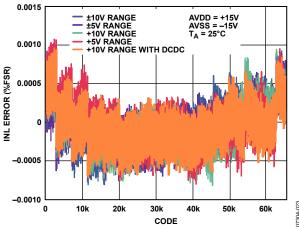

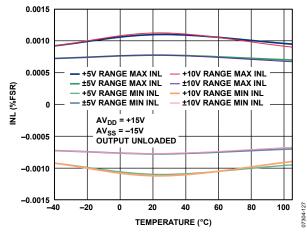

| Relative Accuracy (INL)             | -0.006 | ±0.0012 | +0.006 | % FSR         | 0 V to 5 V, 0 V to 10 V, ±5 V, ±10 V ranges                                                  |

|                                     | -0.008 | ±0.0012 | +0.008 | % FSR         | On overranges                                                                                |

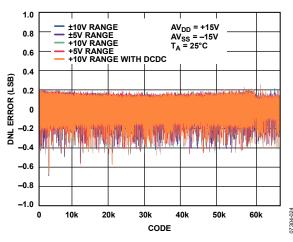

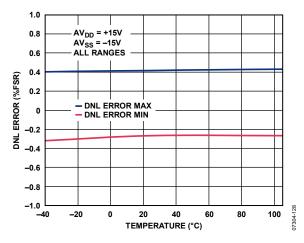

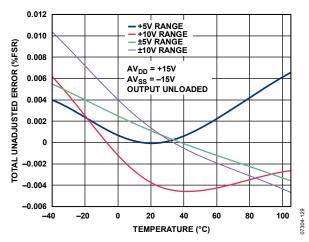

| Differential Nonlinearity (DNL)     | -1     |         | +1     | LSB           | Guaranteed monotonic                                                                         |

| Zero-Scale Error                    | -0.03  | ±0.002  | +0.03  | % FSR         |                                                                                              |

| Zero-Scale TC <sup>2</sup>          |        | ±2      |        | ppm<br>FSR/°C |                                                                                              |

| Bipolar Zero Error                  | -0.03  | ±0.002  | +0.03  | % FSR         |                                                                                              |

| Bipolar Zero TC <sup>2</sup>        |        | ±1      |        | ppm<br>FSR/°C |                                                                                              |

| Offset Error                        | -0.03  | ±0.002  | +0.03  | % FSR         |                                                                                              |

| Offset TC <sup>2</sup>              |        | ±2      |        | ppm<br>FSR/°C |                                                                                              |

| Gain Error                          | -0.03  | ±0.004  | +0.03  | % FSR         |                                                                                              |

| Gain TC <sup>2</sup>                |        | ±3      |        | ppm<br>FSR/°C |                                                                                              |

| Full-Scale Error                    | -0.03  | ±0.002  | +0.03  | % FSR         |                                                                                              |

| Full-Scale TC <sup>2</sup>          |        | ±2      |        | ppm<br>FSR/°C |                                                                                              |

| OUTPUT CHARACTERISTICS <sup>2</sup> |        |         |        |               |                                                                                              |

| Headroom                            |        | 1       | 2.2    | V             |                                                                                              |

| Footroom                            |        | 1       | 1.4    | V             |                                                                                              |

| Output Voltage Drift vs. Time       |        | 20      |        | ppm FSR       | Drift after 1000 hours, $\frac{3}{4}$ scale output, $T_J = 150^{\circ}$ C, $AV_{SS} = -15$ V |

| Short-Circuit Current               | 12/6   | 16/8    |        | mA            | Programmable by user, defaults to 16 mA typical level                                        |

| Load                                | 1      |         |        | kΩ            | For specified performance                                                                    |

| Parameter <sup>1</sup>                       | Min           | Тур           | Max           | Unit           | Test Conditions/Comments                            |

|----------------------------------------------|---------------|---------------|---------------|----------------|-----------------------------------------------------|

| Capacitive Load Stability                    |               |               | 10            | nF             |                                                     |

|                                              |               |               | 2             | μF             | External compensation capacitor of 220 pF connected |

| DC Output Impedance                          |               | 0.06          |               | Ω              |                                                     |

| DC PSRR                                      |               | 50            |               | μV/V           |                                                     |

| DC Crosstalk                                 |               | 24            |               | μV             |                                                     |

| CURRENT OUTPUT                               |               |               |               |                |                                                     |

| Output Current Ranges                        | 0             |               | 24            | mA             |                                                     |

| . 2                                          | 0             |               | 20            | mA             |                                                     |

|                                              | 4             |               | 20            | mA             |                                                     |

| Resolution                                   | 16            |               |               | Bits           |                                                     |

| ACCURACY (EXTERNAL RSET)                     |               |               |               |                | Assumes ideal resistor                              |

| Total Unadjusted Error (TUE)                 |               |               |               |                |                                                     |

| B Version                                    | -0.05         | ±0.009        | +0.05         | % FSR          |                                                     |

| A Version                                    | -0.2          | ±0.04         | +0.2          | % FSR          |                                                     |

| TUE Long-Term Stability                      |               | 100           |               | ppm FSR        | Drift after 1000 hours, T <sub>J</sub> = 150°C      |

| Relative Accuracy (INL)                      | -0.006        |               | +0.006        | % FSR          |                                                     |

| Differential Nonlinearity (DNL)              | -1            |               | +1            | LSB            | Guaranteed monotonic                                |

| Offset Error                                 | -0.05         | ±0.005        | +0.05         | % FSR          |                                                     |

| Offset Error Drift <sup>2</sup>              |               | ±4            |               | ppm            |                                                     |

|                                              |               |               |               | FSR/°C         |                                                     |

| Gain Error                                   | -0.05         | ±0.004        | +0.05         | % FSR          |                                                     |

| Gain TC <sup>2</sup>                         |               | ±3            |               | ppm<br>FSR/°C  |                                                     |

| Full-Scale Error                             | -0.05         | ±0.008        | +0.05         | % FSR          |                                                     |

| Full-Scale TC <sup>2</sup>                   |               | ±5            |               | ppm            |                                                     |

|                                              |               |               |               | FSR/°C         |                                                     |

| DC Crosstalk                                 |               | 0.0005        |               | % FSR          | External R <sub>SET</sub>                           |

| ACCURACY (INTERNAL R <sub>SET</sub> )        |               |               |               |                |                                                     |

| Total Unadjusted Error (TUE) <sup>3, 4</sup> |               |               |               |                |                                                     |

| B Version                                    | -0.14         |               | +0.14         | % FSR          |                                                     |

|                                              | -0.11         | ±0.009        | +0.11         | % FSR          | $T_A = 25^{\circ}C$                                 |

| A Version                                    | -0.35         |               | +0.35         | % FSR          |                                                     |

|                                              | -0.2          | +0.04         | +0.2          | % FSR          | $T_A = 25^{\circ}C$                                 |

| TUE Long-Term Stability                      |               | 180           |               | ppm FSR        | Drift after 1000 hours, T <sub>J</sub> = 150°C      |

| Relative Accuracy (INL)                      | -0.006        |               | +0.006        | % FSR          |                                                     |

| Relative Accuracy (INL)                      | -0.004        |               | +0.004        | % FSR          | $T_A = 25^{\circ}C$                                 |

| Differential Nonlinearity (DNL)              | -1            |               | +1            | LSB            | Guaranteed monotonic                                |

| Offset Error <sup>3, 4</sup>                 | -0.05         |               | +0.05         | % FSR          |                                                     |

|                                              | -0.04         | ±0.007        | +0.04         | % FSR          | $T_A = 25^{\circ}C$                                 |

| Offset Error Drift <sup>2</sup>              |               | ±6            |               | ppm<br>FSR/°C  |                                                     |

| Gain Error                                   | -0.12         |               | +0.12         | % FSR          |                                                     |

|                                              | -0.06         | ±0.002        | +0.06         | % FSR          | T <sub>A</sub> = 25°C                               |

| Gain TC <sup>2</sup>                         | 0.00          | ±9            |               | ppm<br>FSR/°C  |                                                     |

| Full-Scale Error <sup>3, 4</sup>             | -0.14         |               | +0.14         | % FSR/ C       |                                                     |

|                                              | -0.14<br>-0.1 | ±0.007        | +0.14<br>+0.1 | % FSR<br>% FSR | $T_{\rm c} = 25^{\circ}C$                           |

| Full-Scale TC <sup>2</sup>                   | -0.1          | ±0.007<br>±14 | +0.1          | ppm            | $T_A = 25^{\circ}C$                                 |

|                                              |               | 0.011         |               | FSR/°C         |                                                     |

| DC Crosstalk <sup>4</sup>                    |               | -0.011        |               | % FSR          | Internal R <sub>SET</sub>                           |

| Parameter <sup>1</sup>                      | Min           | Тур                           | Max                           | Unit    | Test Conditions/Comments                                                                                                               |

|---------------------------------------------|---------------|-------------------------------|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT CHARACTERISTICS <sup>2</sup>         |               |                               |                               |         |                                                                                                                                        |

| Current Loop Compliance Voltage             |               | V <sub>BOOST_x</sub><br>- 2.4 | V <sub>BOOST_x</sub> –<br>2.7 | v       |                                                                                                                                        |

| Output Current Drift vs. Time               |               |                               |                               |         | Drift after 1000 hours, ¾ scale output, T <sub>J</sub> = 150°C                                                                         |

|                                             |               | 90                            |                               | ppm FSR | External R <sub>SET</sub>                                                                                                              |

|                                             |               | 140                           |                               | ppm FSR | Internal RsFT                                                                                                                          |

| Resistive Load                              |               | 110                           | 1000                          | Ω       | The dc-to-dc converter has been characterized                                                                                          |

|                                             |               |                               |                               |         | with a maximum load of 1 k $\Omega$ , chosen such that<br>compliance is not exceeded; see Figure 52 and<br>DC-DC MaxV bits in Table 25 |

| Output Impedance                            |               | 100                           |                               | MΩ      |                                                                                                                                        |

| DC PSRR                                     |               | 0.02                          | 1                             | μA/V    |                                                                                                                                        |

| REFERENCE INPUT/OUTPUT                      |               |                               |                               |         |                                                                                                                                        |

| Reference Input <sup>2</sup>                |               |                               |                               |         |                                                                                                                                        |

| Reference Input Voltage                     | 4.95          | 5                             | 5.05                          | v       | For specified performance                                                                                                              |

| DC Input Impedance                          | 45            | 150                           |                               | MΩ      |                                                                                                                                        |

| Reference Output                            |               |                               |                               |         |                                                                                                                                        |

| Output Voltage                              | 4.995         | 5                             | 5.005                         | v       | T <sub>A</sub> = 25°C                                                                                                                  |

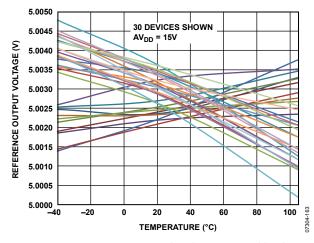

| Reference TC <sup>2</sup>                   | -10           | ±5                            | +10                           | ppm/°C  |                                                                                                                                        |

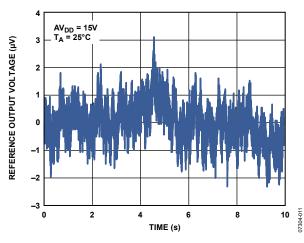

| Output Noise (0.1 Hz to 10 Hz) <sup>2</sup> | 10            | 7                             | 110                           | μV p-p  |                                                                                                                                        |

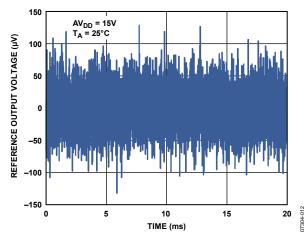

| Noise Spectral Density <sup>2</sup>         |               | 100                           |                               | nV/√Hz  | At 10 kHz                                                                                                                              |

| Output Voltage Drift vs. Time <sup>2</sup>  |               | 180                           |                               | ppm     | Drift after 1000 hours, $T_J = 150^{\circ}C$                                                                                           |

| Capacitive Load <sup>2</sup>                |               | 1000                          |                               | nF      |                                                                                                                                        |

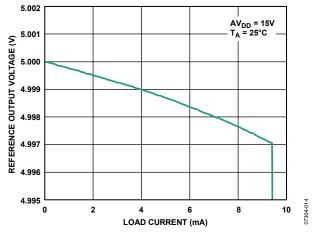

| Load Current                                |               | 9                             |                               | mA      | See Figure 63                                                                                                                          |

| Short-Circuit Current                       |               | 10                            |                               | mA      | See righte 05                                                                                                                          |

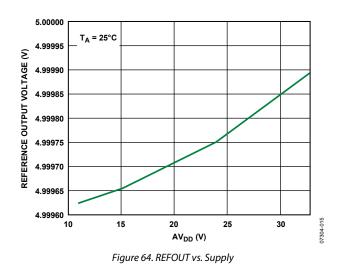

| Line Regulation <sup>2</sup>                |               | 3                             |                               | ppm/V   | See Figure 64                                                                                                                          |

| -                                           |               | 5<br>95                       |                               |         | -                                                                                                                                      |

| Load Regulation <sup>2</sup>                |               |                               |                               | ppm/mA  | See Figure 63                                                                                                                          |

| Thermal Hysteresis <sup>2</sup>             |               | 160<br>5                      |                               | ppm     | First temperature cycle                                                                                                                |

|                                             |               | 5                             |                               | ppm     | Second temperature cycle                                                                                                               |

| DC-TO-DC                                    |               |                               |                               |         |                                                                                                                                        |

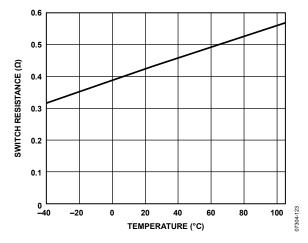

| Switch                                      |               | 0.425                         |                               | 0       |                                                                                                                                        |

| Switch On Resistance                        |               | 0.425                         |                               | Ω       |                                                                                                                                        |

| Switch Leakage Current                      |               | 10                            |                               | nA      |                                                                                                                                        |

| Peak Current Limit                          |               | 0.8                           |                               | A       |                                                                                                                                        |

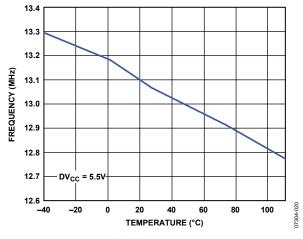

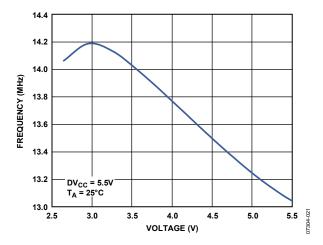

| Oscillator                                  |               |                               |                               |         |                                                                                                                                        |

| Oscillator Frequency                        | 11.5          | 13                            | 14.5                          | MHz     | This oscillator is divided down to give the dc-to-dc converter switching frequency                                                     |

| Maximum Duty Cycle                          |               | 89.6                          |                               | %       | At 410 kHz dc-to-dc switching frequency                                                                                                |

| DIGITAL INPUTS <sup>2</sup>                 |               |                               |                               |         | JEDEC compliant                                                                                                                        |

| V⊪, Input High Voltage                      | 2             |                               |                               | V       |                                                                                                                                        |

| V⊩, Input Low Voltage                       |               |                               | 0.8                           | V       |                                                                                                                                        |

| Input Current                               | -1            |                               | +1                            | μA      | Per pin                                                                                                                                |

| Pin Capacitance                             |               | 2.6                           |                               | pF      | Per pin                                                                                                                                |

| DIGITAL OUTPUTS <sup>2</sup>                |               |                               |                               |         |                                                                                                                                        |

| SDO, ALERT                                  |               |                               |                               |         |                                                                                                                                        |

| Vol, Output Low Voltage                     |               |                               | 0.4                           | V       | Sinking 200 μA                                                                                                                         |

| V <sub>OH</sub> , Output High Voltage       | DVDD –<br>0.5 |                               |                               | v       | Sourcing 200 μA                                                                                                                        |

| High Impedance Leakage<br>Current           | -1            |                               | +1                            | μΑ      |                                                                                                                                        |

| High Impedance Output<br>Capacitance        |               | 2.5                           |                               | pF      |                                                                                                                                        |

| Parameter <sup>1</sup>          | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                                                                   |

|---------------------------------|-------|------|-------|------|------------------------------------------------------------------------------------------------------------|

| FAULT                           |       |      |       |      |                                                                                                            |

| Vol, Output Low Voltage         |       |      | 0.4   | V    | 10 k $\Omega$ pull-up resistor to DV <sub>DD</sub>                                                         |

| Vol, Output Low Voltage         |       | 0.6  |       | V    | At 2.5 mA                                                                                                  |

| Voн, Output High Voltage        | 3.6   |      |       | V    | 10 k $\Omega$ pull-up resistor to DV <sub>DD</sub>                                                         |

| POWER REQUIREMENTS              |       |      |       |      |                                                                                                            |

| AV <sub>DD</sub>                | 9     |      | 33    | V    |                                                                                                            |

| AV <sub>ss</sub>                | -26.4 |      | -10.8 | V    |                                                                                                            |

| DV <sub>DD</sub>                | 2.7   |      | 5.5   | V    |                                                                                                            |

| AV <sub>CC</sub>                | 4.5   |      | 5.5   | V    |                                                                                                            |

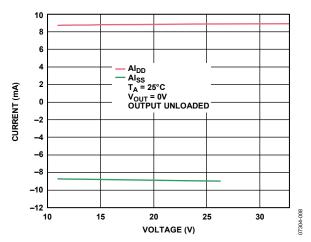

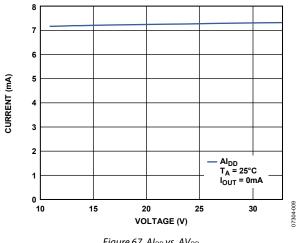

| Aldd                            |       | 8.6  | 10.5  | mA   | Voltage output mode on all channels, output unloaded, over supplies                                        |

|                                 |       | 7    | 7.5   | mA   | Current output mode on all channels,                                                                       |

| Alss                            | -11   | -8.8 |       | mA   | Voltage output mode on all channels, output unloaded, over supplies                                        |

|                                 | -1.7  |      |       | mA   | Current output mode on all channels                                                                        |

| Dlcc                            |       | 9.2  | 11    | mA   | $V_{IH} = DV_{DD}$ , $V_{IL} = DGND$ , internal oscillator running, over supplies                          |

| Alcc                            |       |      | 1     | mA   | Output unloaded, over supplies                                                                             |

| I <sub>BOOST</sub> <sup>5</sup> |       |      | 2.7   | mA   | Per channel, voltage output mode, output unloaded, over supplies                                           |

|                                 |       |      | 1     | mA   | Per channel, current output mode                                                                           |

| Power Dissipation               |       | 173  |       | mW   | $AV_{DD} = 15 V$ , $AV_{SS} = -15 V$ , dc-to-dc converter<br>enable, current output mode, outputs disabled |

<sup>1</sup>Temperature range: -40°C to +105°C; typical at +25°C.

<sup>2</sup> Guaranteed by design and characterization; not production tested.

<sup>3</sup> For current outputs with internal R<sub>SET</sub>, the offset, full-scale, and TUE measurements exclude dc crosstalk. The measurements are made with all four channels enabled loaded with the same code.

$^{\rm 4}$  See the Current Output Mode with Internal  $R_{\text{SET}}$  section for more explanation of the dc crosstalk.

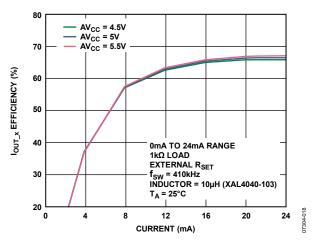

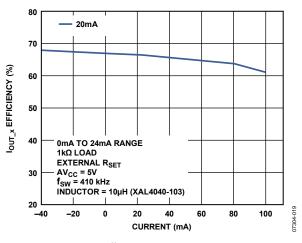

<sup>5</sup> Efficiency plots in Figure 54, Figure 55, Figure 56, and Figure 57 include the I<sub>BOOST</sub> quiescent current.

### **AC PERFORMANCE CHARACTERISTICS**

$AV_{DD} = V_{BOOST_x} = 15 \text{ V}; AV_{SS} = -15 \text{ V}; DV_{DD} = 2.7 \text{ V}$  to 5.5 V;  $AV_{CC} = 4.5 \text{ V}$  to 5.5 V; dc-to-dc converter disabled;  $AGND = DGND = GNDSW_x = 0 \text{ V}; REFIN = 5 \text{ V};$  voltage outputs:  $R_L = 2 \text{ k}\Omega$ ,  $C_L = 220 \text{ pF};$  current outputs:  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 2.

| Parameter <sup>1</sup>                      | Min | Тур  | Max | Unit    | Test Conditions/Comments                                          |

|---------------------------------------------|-----|------|-----|---------|-------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                         |     |      |     |         |                                                                   |

| Voltage Output                              |     |      |     |         |                                                                   |

| Output Voltage Settling Time                |     | 11   |     | μs      | 5 V step to $\pm 0.03\%$ FSR, 0 V to 5 V range                    |

|                                             |     |      | 18  | μs      | 10 V step to $\pm 0.03\%$ FSR, 0 V to 10 V range                  |

|                                             |     |      | 13  | μs      | 100 mV step to 1 LSB (16-bit LSB), 0 V to 10 V                    |

|                                             |     |      |     |         | range                                                             |

| Slew Rate                                   |     | 1.9  |     | V/µs    | 0 V to 10 V range                                                 |

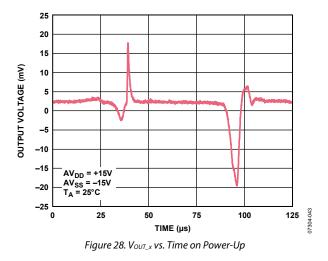

| Power-On Glitch Energy                      |     | 150  |     | nV-sec  |                                                                   |

| Digital-to-Analog Glitch Energy             |     | 6    |     | nV-sec  |                                                                   |

| Glitch Impulse Peak Amplitude               |     | 25   |     | mV      |                                                                   |

| Digital Feedthrough                         |     | 1    |     | nV-sec  |                                                                   |

| DAC to DAC Crosstalk                        |     | 2    |     | nV-sec  | 0 V to 10 V range                                                 |

| Output Noise (0.1 Hz to 10 Hz<br>Bandwidth) |     | 0.15 |     | LSB p-p | 16-bit LSB, 0 V to 10 V range                                     |

| Output Noise Spectral Density               |     | 150  |     | nV/√Hz  | Measured at 10 kHz, midscale output, 0 V to 10 V range            |

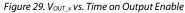

| AC PSRR                                     |     | 83   |     | dB      | 200 mV 50 Hz/60 Hz sine wave superimposed on power supply voltage |

| Parameter <sup>1</sup>                      | Тур | Max                              | Unit | Test Conditions/Comments |                                                          |

|---------------------------------------------|-----|----------------------------------|------|--------------------------|----------------------------------------------------------|

| Current Output                              |     |                                  |      |                          |                                                          |

| Output Current Settling Time                |     | 15                               |      | μs                       | To 0.1% FSR (0 mA to 24 mA)                              |

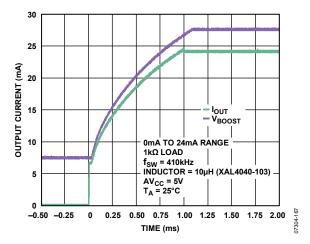

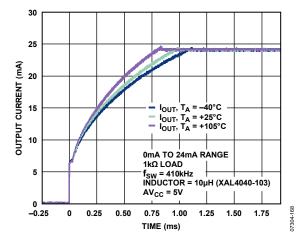

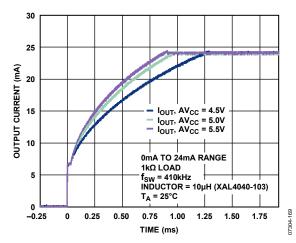

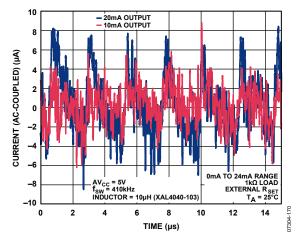

|                                             |     | See test conditions/<br>comments |      | ms                       | See Figure 48, Figure 49, and Figure 50                  |

| Output Noise (0.1 Hz to 10 Hz<br>Bandwidth) |     | 0.15                             |      | LSB p-p                  | 16-bit LSB, 0 mA to 24 mA range                          |

| Output Noise Spectral Density               |     | 0.5                              |      | nA/√Hz                   | Measured at 10 kHz, midscale output, 0 mA to 24 mA range |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

### **TIMING CHARACTERISTICS**

$AV_{DD} = V_{BOOST_x} = 15 V$ ;  $AV_{SS} = -15 V$ ;  $DV_{DD} = 2.7 V$  to 5.5 V;  $AV_{CC} = 4.5 V$  to 5.5 V; dc-to-dc converter disabled; AGND = DGND = 100 VGNDSW<sub>x</sub> = 0 V; REFIN = 5 V; voltage outputs:  $R_L = 1 \text{ k}\Omega$ ,  $C_L = 220 \text{ pF}$ ; current outputs:  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

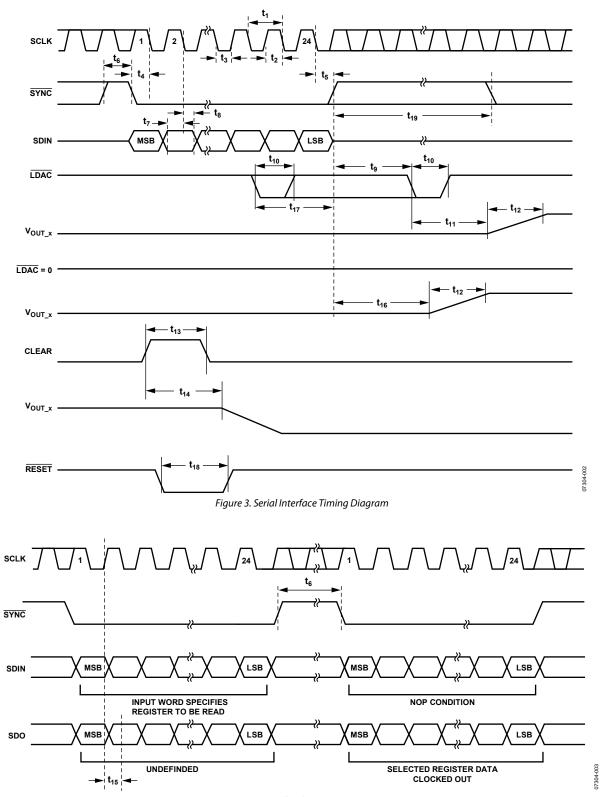

Table 3.

| Parameter <sup>1, 2, 3</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub>      | Unit   | Description                                                                                                                  |

|------------------------------|---------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| t <sub>1</sub>               | 33                                                | ns min | SCLK cycle time                                                                                                              |

| t <sub>2</sub>               | 13                                                | ns min | SCLK high time                                                                                                               |

| t <sub>3</sub>               | 13                                                | ns min | SCLK low time                                                                                                                |

| t <sub>4</sub>               | 13                                                | ns min | SYNC falling edge to SCLK falling edge setup time                                                                            |

| t <sub>5</sub>               | 13                                                | ns min | 24 <sup>th</sup> /32 <sup>nd</sup> SCLK falling edge to SYNC rising edge (see Figure 77)                                     |

| t <sub>6</sub>               | 198                                               | ns min | SYNC high time                                                                                                               |

| t <sub>7</sub>               | 5                                                 | ns min | Data setup time                                                                                                              |

| t <sub>8</sub>               | 5                                                 | ns min | Data hold time                                                                                                               |

| t9                           | 20                                                | µs min | SYNC rising edge to LDAC falling edge (all DACs updated or any channel has digital slew rate control enabled)                |

|                              | 5                                                 | µs min | SYNC rising edge to LDAC falling edge (single DAC updated)                                                                   |

| t <sub>10</sub>              | 10                                                | ns min | LDAC pulse width low                                                                                                         |

| t11                          | 500                                               | ns max | LDAC falling edge to DAC output response time                                                                                |

| t <sub>12</sub>              | See the AC Performance<br>Characteristics section | µs max | DAC output settling time                                                                                                     |

| <b>t</b> <sub>13</sub>       | 10                                                | ns min | CLEAR high time                                                                                                              |

| t <sub>14</sub>              | 5                                                 | µs max | CLEAR activation time                                                                                                        |

| t <sub>15</sub>              | 40                                                | ns max | SCLK rising edge to SDO valid                                                                                                |

| t <sub>16</sub>              | 21                                                | µs min | $\overline{SYNC}$ rising edge to DAC output response time ( $\overline{LDAC} = 0$ ) (all DACs updated)                       |

|                              | 5                                                 | µs min | $\overline{\text{SYNC}}$ rising edge to DAC output response time ( $\overline{\text{LDAC}} = 0$ ) (single DAC updated)       |

| t <sub>17</sub>              | 500                                               | ns min | LDAC falling edge to SYNC rising edge                                                                                        |

| t <sub>18</sub>              | 800                                               | ns min | RESET pulse width                                                                                                            |

| t <sub>19</sub> <sup>4</sup> | 20                                                | µs min | SYNC high to next SYNC low (digital slew rate control enabled) (all DACs updated)                                            |

|                              | 5                                                 | µs min | $\overline{\text{SYNC}}$ high to next $\overline{\text{SYNC}}$ low (digital slew rate control disabled) (single DAC updated) |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

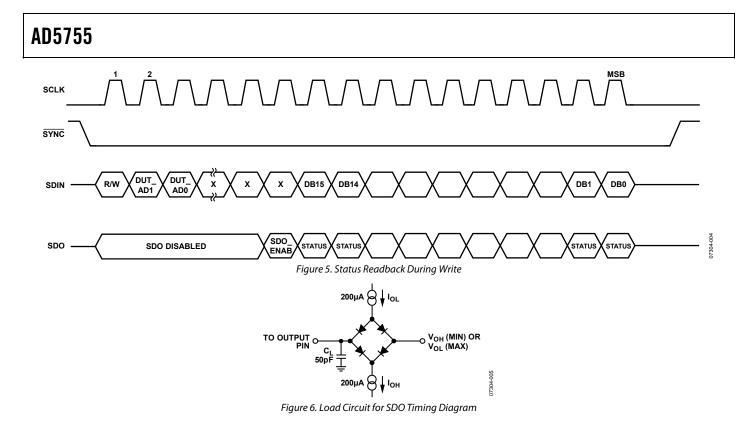

<sup>2</sup> All input signals are specified with  $t_{RISE} = t_{FALL} = 5$  ns (10% to 90% of DV<sub>DD</sub>) and timed from a voltage level of 1.2 V. <sup>3</sup> See Figure 3, Figure 4, Figure 5, and Figure 6.

<sup>4</sup> This specification applies if LDAC is held low during the write cycle; otherwise, see t<sub>9</sub>.

Figure 4. Readback Timing Diagram

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 4.

| Parameter         Rating           AV <sub>DD</sub> , V <sub>BOOST_x</sub> to AGND, DGND         -0.3 V to +33 V           AV <sub>SS</sub> to AGND, DGND         +0.3 V to -28 V           AV <sub>DD</sub> to AV <sub>SS</sub> -0.3 V to +60 V           AV <sub>CC</sub> to AGND         -0.3 V to +7 V           DV <sub>DD</sub> to DGND         -0.3 V to +7 V           Digital Inputs to DGND         -0.3 V to DV <sub>DD</sub> + 0.3 V or +7 V           Digital Outputs to DGND         -0.3 V to DV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           Digital Outputs to DGND         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V           (whichever is less)         AV <sub>SS</sub> to V <sub>BOOST_x</sub> or 33 V if using the dc-to-dc circuitry           +V <sub>SENSE_x</sub> , -V <sub>SENSE_x</sub> to AGND         -0.3 to +33 V           AGND, GNDSW <sub>x</sub> to DGND         -0.3 V to +0.3 V           Oper                                                                                 | Table 4.                                              |                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------|

| AV <sub>5S</sub> to AGND, DGND $+0.3$ V to $-28$ VAV <sub>bD</sub> to AV <sub>5S</sub> $-0.3$ V to $+60$ VAV <sub>cC</sub> to AGND $-0.3$ V to $+7$ VDV <sub>bD</sub> to DGND $-0.3$ V to $+7$ VDigital Inputs to DGND $-0.3$ V to DV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to DV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to AV <sub>bD</sub> $+ 0.3$ V or $+7$ V(whichever is less) $-0.3$ V to $-0.3$ V if using the dc-to-dc circuitry $+V_{SENSE_x}$ , $-V_{SENSE_x}$ to AGND $-0.3$ to $+33$ V $-0.3$ V to $+0.3$ V $-0.3$ V to $+0.3$ VOperating Temperature Range $-65^{\circ}$ C to $+105^{\circ}$ C $10$ Industrial <sup>1</sup> $-40^{\circ}$ C to $+105^{\circ}$ C $10$ Industrial <sup>1</sup> $-40^{\circ}$ C to $+105^{\circ}$ C $0_{A}$ Thermal Impedance <sup>2</sup> $20^{\circ}$ C/W $0_{A}$ Thermal Impedance <sup>2</sup> $20^{\circ}$ C/WPower Dissipation $(T_{J}$ max $-T_{A})/\theta_{JA}$ Lead Temperature< | Parameter                                             | Rating                                |

| AV_{DD} to AVss $-0.3 V to +60 V$ AV <sub>CC</sub> to AGND $-0.3 V to +7 V$ DV <sub>DD</sub> to DGND $-0.3 V to +7 V$ Digital Inputs to DGND $-0.3 V to DV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to DV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to DV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to AV_{DD} + 0.3 V or +7 V$ (whichever is less) $-0.3 V to BOOST_x or 33 V if using the dc-to-dc circuitryI_{OUT_x} to AGND-0.3 to +33 VI_{OUT_x} to AGND-0.3 to +33 VAGND, GNDSW_x to DGND-0.3 V to +0.3 VOperating Temperature Range-65^{\circ}C to +105^{\circ}CI_{Industrial}^{1}-40^{\circ}C to +105^{\circ}CI_{UT_x} to AGND-0.5^{\circ}C to +150^{\circ}CI_{UT_x} to AGND-0.5^{\circ}C to +150^{\circ}CI_{UT_x} to AGND-0.5^{\circ}C to +10.5^{\circ}C<$                                                                                                                                                                                                                                                       | AVDD, VBOOST_x to AGND, DGND                          | –0.3 V to +33 V                       |

| AV <sub>CC</sub> to AGND $-0.3 V$ to $+7 V$ DV <sub>DD</sub> to DGND $-0.3 V$ to $+7 V$ Digital Inputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$ (whichever is less) $V$ our_x to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using the dc-to-dc circuitry $I_{OUT_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using the dc-to-dc circuitry $I_{OUT_x}$ to AGND $-0.3 V to +0.3 VOperating Temperature Range (T_A)-40^{\circ}C to +105^{\circ}CIndustrial^1-40^{\circ}C to +105^{\circ}CIunction Temperature Range-65^{\circ}C to +150^{\circ}CJunction Temperature (T_1 max)125^{\circ}C64-Lead LFCSP20^{\circ}C/WP_{Ower} Dissipation(T_1 max - T_A)/\theta_{JA}Lead TemperatureJEDEC industry standard$                                                                                                                                                                                                                                                                                                                                          | AVss to AGND, DGND                                    | +0.3 V to -28 V                       |

| DV<br>DDto DGND $-0.3 V$ to $+7 V$ Digital Inputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)Digital Outputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)REFIN, REFOUT to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)VouT_x to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)VouT_x to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)VouT_x to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $+V_{SENSE_x}, -V_{SENSE_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $ ouT_x$ to AGND $-0.3 V$ to $+0.3 V$ $0_{OT_x}$ to AGND $-0.3 V = 0.3 V$ $0_{OT_x}$ to AGND $-0.3 V = 0.3 V$ $0_{OT_$                                                                                                                                                                                                                                                                             | AV <sub>DD</sub> to AV <sub>ss</sub>                  | –0.3 V to +60 V                       |

| Digital Inputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)Digital Outputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)REFIN, REFOUT to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less) $V_{OUT_x}$ to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less) $V_{OUT_x}$ to AGND $AV_{55}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $+V_{SENSE_x}$ , $-V_{SENSE_x}$ to AGND $AV_{55}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $ ouT_x$ to AGND $AV_{55}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $ ouT_x$ to AGND $-0.3 to +33 V$ $aGND$ , $GNDSW_x$ to DGND $-0.3 V$ to $+0.3 V$ Operating Temperature Range<br>Junction Temperature (T_J max) $-40^\circ$ C to $+105^\circ$ C $64$ -Lead LFCSP $-65^\circ$ C to $+150^\circ$ C $\theta_{JA}$ Thermal Impedance2 $20^\circ$ C/WPower Dissipation $(T_J max - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AV <sub>cc</sub> to AGND                              | –0.3 V to +7 V                        |

| Joint State(whichever is less)Digital Outputs to DGND $-0.3 V$ to $DV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less)REFIN, REFOUT to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less) $V_{OUT_x}$ to AGND $AV_{5S}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $+V_{SENSE_x}$ , $-V_{SENSE_x}$ to AGND $AV_{5S}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $ _{OUT_x}$ to AGND $AV_{5S}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $ _{OUT_x}$ to AGND $-0.3 \text{ to } +33 V$ $ _{OUT_x}$ to AGND $-0.3 \text{ to } +33 V$ $ _{OUT_x}$ to AGND $-0.3 V$ to $+0.3 V$ $Operating Temperature Range (T_A)$ $-40^{\circ}$ C to $+105^{\circ}$ C $ _{Industrial^1}$ $-40^{\circ}$ C to $+105^{\circ}$ C $ _{Junction Temperature}(T_J max)$ $125^{\circ}$ C $64$ -Lead LFCSP $20^{\circ}$ C/W $Power Dissipation$ $(T_J max - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DV <sub>DD</sub> to DGND                              | –0.3 V to +7 V                        |

| Sector(whichever is less)REFIN, REFOUT to AGND $-0.3 V$ to $AV_{DD} + 0.3 V$ or $+7 V$<br>(whichever is less) $V_{OUT_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $+V_{SENSE_x}$ , $-V_{SENSE_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $I_{OUT_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $I_{OUT_x}$ to AGND $AV_{SS}$ to $V_{BOOST_x}$ or $33 V$ if using<br>the dc-to-dc circuitry $I_{OUT_x}$ to AGND $-0.3 \text{ to } +33 V$ $AGND$ , $GNDSW_x$ to DGND $-0.3 V$ to $+0.3 V$ Operating Temperature Range<br>Junction Temperature (T_J max) $-40^{\circ}$ C to $+105^{\circ}$ C $64$ -Lead LFCSP $-65^{\circ}$ C to $+150^{\circ}$ C $\theta_{JA}$ Thermal Impedance2 $20^{\circ}$ C/WPower Dissipation $(T_J max - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Digital Inputs to DGND                                |                                       |

| $\begin{array}{ll} & (\mbox{whichever is less}) \\ V_{OUT_x} to AGND & AV_{SS} to V_{BOOST_x} or 33 V if using the dc-to-dc circuitry \\ +V_{SENSE_x}, -V_{SENSE_x} to AGND & AV_{SS} to V_{BOOST_x} or 33 V if using the dc-to-dc circuitry \\ l_{OUT_x} to AGND & AV_{SS} to V_{BOOST_x} or 33 V if using the dc-to-dc circuitry \\ SW_x to AGND & -0.3 to +33 V \\ AGND, GNDSW_x to DGND & -0.3 V to +0.3 V \\ Operating Temperature Range (T_A) \\ Industrial^1 & -40^{\circ}C to +105^{\circ}C \\ Storage Temperature (T_J max) & 125^{\circ}C \\ 64-Lead LFCSP & -65^{\circ}C to +150^{\circ}C \\ \theta_{JA} Thermal Impedance^2 & 20^{\circ}C/W \\ Power Dissipation & (T_J max - T_A)/\theta_{JA} \\ Lead Temperature W \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Digital Outputs to DGND                               |                                       |

| the dc-to-dc circuitry $+V_{SENSE_x}$ , $-V_{SENSE_x}$ to AGNDAVss to V_{BOOST_x} or 33 V if using<br>the dc-to-dc circuitry $I_{OUT_x}$ to AGNDAVss to V_{BOOST_x} or 33 V if using<br>the dc-to-dc circuitrySWx to AGND $-0.3$ to $+33$ VAGND, GNDSWx to DGND $-0.3$ V to $+0.3$ VOperating Temperature Range (TA)<br>Industrial1 $-40^{\circ}$ C to $+105^{\circ}$ CStorage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ CJunction Temperature (TJ max) $125^{\circ}$ C $64$ -Lead LFCSP $20^{\circ}$ C/WPower Dissipation(TJ max $- T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REFIN, REFOUT to AGND                                 |                                       |

| Ithe dc-to-dc circuitryIIIIIAGNDSWx to AGND-0.3 to +33 VAGND, GNDSWx to DGND-0.3 V to +0.3 VOperating Temperature Range (TA)Industrial1-40°C to +105°CStorage Temperature Range-65°C to +150°CJunction Temperature (TJ max)125°C64-Lead LFCSP20°C/WPower Dissipation(TJ max – TA)/ $\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{OUT_x}$ to AGND                                   |                                       |

| the dc-to-dc circuitrySWx to AGND $-0.3$ to $+33$ VAGND, GNDSWx to DGND $-0.3$ V to $+0.3$ VOperating Temperature Range (TA) $-40^{\circ}$ C to $+105^{\circ}$ CIndustrial <sup>1</sup> $-40^{\circ}$ C to $+150^{\circ}$ CStorage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ CJunction Temperature (TJ max) $125^{\circ}$ C64-Lead LFCSP $\theta_{JA}$ Thermal Impedance <sup>2</sup> $0^{\circ}$ C/W $C/W$ Power Dissipation $(T_{J} max - T_{A})/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | +V <sub>SENSE_x</sub> , -V <sub>SENSE_x</sub> to AGND | · · · · · · · · · · · · · · · · · · · |

| AGND, GNDSWx to DGND $-0.3 V$ to $+0.3 V$ Operating Temperature Range (TA) $-40^{\circ}$ C to $+105^{\circ}$ CIndustrial1 $-40^{\circ}$ C to $+105^{\circ}$ CStorage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ CJunction Temperature (TJ max) $125^{\circ}$ C $64$ -Lead LFCSP $20^{\circ}$ C/WPower Dissipation $(T_J max - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $I_{OUT_x}$ to AGND                                   | - 5                                   |

| Operating Temperature Range (T_A) $-40^{\circ}$ C to $+105^{\circ}$ CIndustrial1 $-40^{\circ}$ C to $+105^{\circ}$ CStorage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ CJunction Temperature (T_J max) $125^{\circ}$ C64-Lead LFCSP $20^{\circ}$ C/W $\theta_{JA}$ Thermal Impedance2 $20^{\circ}$ C/WPower Dissipation $(T_J max - T_A)/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SW <sub>x</sub> to AGND                               | –0.3 to +33 V                         |

| Industrial1 $-40^{\circ}$ C to $+105^{\circ}$ CStorage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ CJunction Temperature (T <sub>J</sub> max) $125^{\circ}$ C64-Lead LFCSP $\theta_{JA}$ Thermal Impedance2 $0^{\circ}$ C/W $20^{\circ}$ C/WPower Dissipation $(T_{J} max - T_{A})/\theta_{JA}$ Lead TemperatureJEDEC industry standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AGND, GNDSW <sub>x</sub> to DGND                      | –0.3 V to +0.3 V                      |