**ISSUE 2**

8 LINK CES/DBCES AAL1 SAR

# PM73123

# **AAL1GATOR-8**

# 8 LINK CES/DBCES ATM ADAPTATION LAYER 1 (AAL1) SEGMENTATION AND REASSEMBLY PROCESSOR

# **DATASHEET**

PROPRIETARY AND CONFIDENTIAL

RELEASED

ISSUE 2: AUGUST 2001

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

## **REVISION HISTORY**

| Issue<br>No. | Issue<br>Date   | Details of Change                                 |

|--------------|-----------------|---------------------------------------------------|

| 1            | January<br>2000 | Document created.                                 |

| 2            | August<br>2001  | Updated with additional detail and clarification. |

ISSUE 2

8 LINK CES/DBCES AAL1 SAR

# **CONTENTS**

| 1 | FEA   | TURES                                    | 20  |  |

|---|-------|------------------------------------------|-----|--|

| 2 | APP   | APPLICATIONS                             |     |  |

| 3 | REF   | REFERENCES                               |     |  |

| 4 | APP   | APPLICATION EXAMPLES                     |     |  |

|   | 4.1   | INTEGRATED ACCESS DEVICE                 | 29  |  |

|   | 4.2   | ATM PASSIVE OPTICAL NETWORKS (APON)      | 30  |  |

| 5 | BLO   | CK DIAGRAM                               | 31  |  |

| 6 | DES   | CRIPTION                                 | 32  |  |

| 7 | PIN I | DIAGRAM                                  | 33  |  |

| 8 | PIN I | DESCRIPTION                              | 35  |  |

| 9 | FUN   | CTIONAL DESCRIPTION                      | 64  |  |

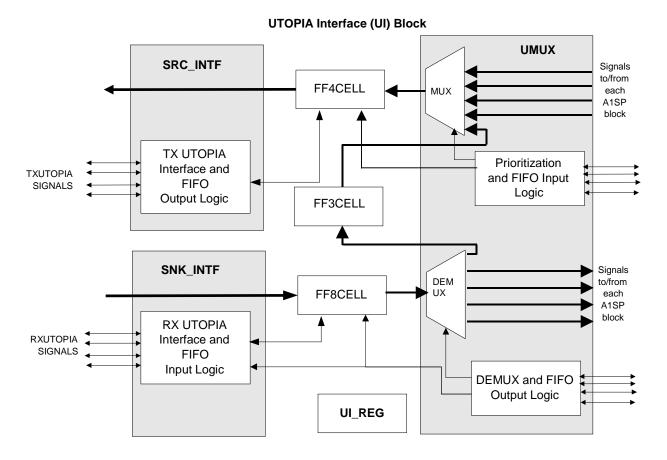

|   | 9.1   | UTOPIA INTERFACE BLOCK (UI)              | 64  |  |

|   |       | 9.1.1 UTOPIA SOURCE INTERFACE (SRC_INTF) | 66  |  |

|   |       | 9.1.2 UTOPIA SINK INTERFACE (SNK_INTF)   | 69  |  |

|   |       | 9.1.3 UTOPIA MUX BLOCK (UMUX)            | 72  |  |

|   | 9.2   | AAL1 SAR PROCESSING BLOCK (A1SP)         | 73  |  |

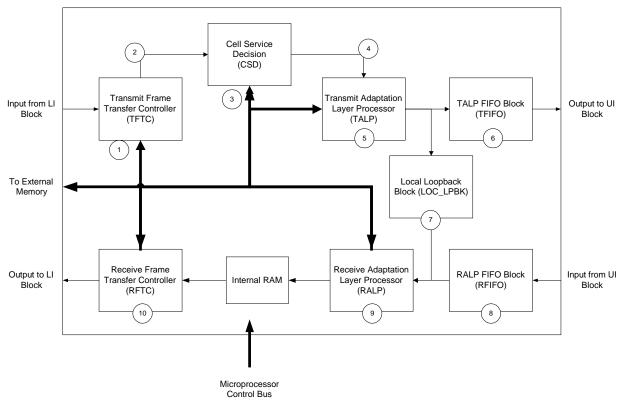

|   |       | 9.2.1 AAL1 SAR TRANSMIT SIDE (TXA1SP)    | 75  |  |

|   |       | 9.2.2 AAL1 SAR RECEIVE SIDE (RXA1SP)     | 102 |  |

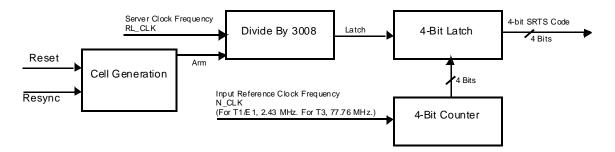

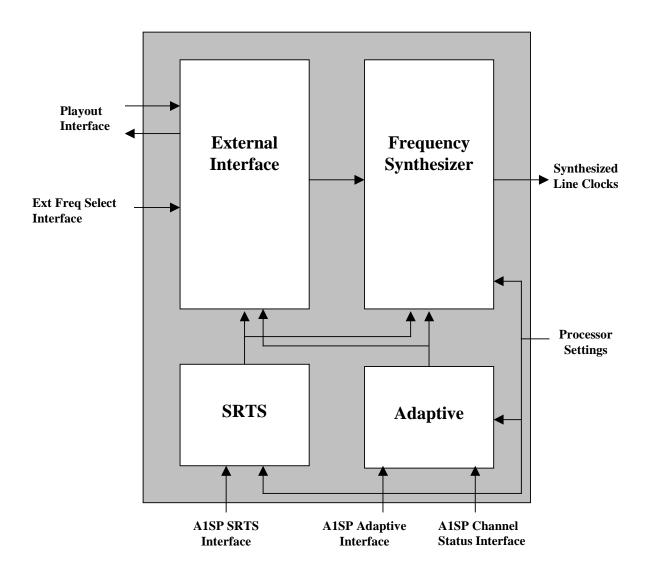

|   | 9.3   | AAL1 CLOCK GENERATION CONTROL            | 137 |  |

|   |       | 9.3.1 DESCRIPTION                        | 137 |  |

|   |       | 9.3.2 CGC BLOCK DIAGRAM                  | 139 |  |

|   |       | 9.3.3 FUNCTIONAL DESCRIPTION             | 139 |  |

ISSUE 2

|    | 9.4  | PROCESSOR INTERFACE BLOCK (PROCI)             | . 151 |

|----|------|-----------------------------------------------|-------|

|    |      | 9.4.1 INTERRUPT DRIVEN ERROR/STATUS REPORTING | . 156 |

|    |      | 9.4.2 ADD QUEUE FIFO                          | . 159 |

|    | 9.5  | RAM INTERFACE BLOCK (RAMI)                    | . 161 |

|    | 9.6  | LINE INTERFACE BLOCK (AAL1_LI)                | . 162 |

|    |      | 9.6.1 CONVENTIONS                             | . 162 |

|    |      | 9.6.2 FUNCTIONAL DESCRIPTION                  | . 162 |

|    |      | 9.6.3 TRANSMIT DIRECTION                      | . 167 |

|    | 9.7  | JTAG TEST ACCESS PORT                         | . 171 |

| 10 | MEMO | ORY MAPPED REGISTER DESCRIPTION               | . 172 |

|    | 10.1 | INITIALIZATION                                | . 173 |

|    | 10.2 | A1SP AND LINE CONFIGURATION STRUCTURES        | . 173 |

|    |      | 10.2.1 HS_LIN_REG                             | . 174 |

|    | 10.3 | TRANSMIT STRUCTURES SUMMARY                   | . 179 |

|    |      | 10.3.1 P_FILL_CHAR                            | . 181 |

|    |      | 10.3.2 T_SEQNUM_TBL                           | . 181 |

|    |      | 10.3.3 T_COND_SIG                             | . 182 |

|    |      | 10.3.4 T_COND_DATA                            | . 184 |

|    |      | 10.3.5 RESERVED (TRANSMIT SIGNALING BUFFER)   | . 185 |

|    |      | 10.3.6 T_OAM_QUEUE                            | . 186 |

|    |      | 10.3.7 T_QUEUE_TBL                            | . 187 |

|    |      | 10.3.8 RESERVED (TRANSMIT DATA BUFFER)        | 200   |

|    | 10.4 | RECEIVE DATA STRUCTURES SUMMARY               | . 201 |

|    |      | 10.4.1 R_OAM_QUEUE_TBL                        | . 203 |

|    |      |                                               |       |

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

|    |      | 10.4.2 R_OAM_CELL_CNT                         | 204 |

|----|------|-----------------------------------------------|-----|

|    |      | 10.4.3 R_DROP_OAM_CELL                        | 204 |

|    |      | 10.4.4 R_SRTS_CONFIG                          | 205 |

|    |      | 10.4.5 R_CRC_SYNDROME                         | 206 |

|    |      | 10.4.6 R_CH_TO_QUEUE_TBL                      | 209 |

|    |      | 10.4.7 R_COND_SIG                             | 212 |

|    |      | 10.4.8 R_COND_DATA                            | 213 |

|    |      | 10.4.9 RESERVED (RECEIVE SRTS QUEUE)          | 214 |

|    |      | 10.4.10 RESERVED (RECEIVE SIGNALING BUFFER)   | 215 |

|    |      | 10.4.11 R_QUEUE_TBL                           | 217 |

|    |      | 10.4.12 R_OAM_QUEUE                           | 234 |

|    |      | 10.4.13 RESERVED (RECEIVE DATA BUFFER)        | 235 |

| 11 | NOR  | MAL MODE REGISTER DESCRIPTION                 | 237 |

|    | 11.1 | COMMAND REGISTERS                             | 238 |

|    | 11.2 | RAM INTERFACE REGISTERS                       | 244 |

|    | 11.3 | UTOPIA INTERFACE REGISTERS                    | 246 |

|    | 11.4 | LINE INTERFACE REGISTERS                      | 255 |

|    | 11.5 | DIRECT MODE REGISTERS                         | 255 |

|    | 11.6 | INTERRUPT AND STATUS REGISTERS                | 258 |

|    | 11.7 | IDLE CHANNEL DETECTION CONFIGURATION AND STAT |     |

|    | 11.8 | DLL CONTROL AND STATUS REGISTERS              | 288 |

| 12 | OPER | RATION                                        | 293 |

|    | 12.1 | HARDWARE CONFIGURATION                        | 293 |

| ISSUE 2 | 8 LINK CES/DBCES AAL1 SAR   |

|---------|-----------------------------|

| IOGOL Z | O ENTR OLO, DE OLO AALT GAR |

|    | 12.2 | START-UP                                    | . 293 |

|----|------|---------------------------------------------|-------|

|    |      | 12.2.1 LINE CONFIGURATION                   | . 294 |

|    |      | 12.2.2 QUEUE CONFIGURATION                  | . 294 |

|    |      | 12.2.3 ADDING QUEUES                        | . 294 |

|    |      | 12.2.4 LINE CONFIGURATION DETAILS           | . 294 |

|    | 12.3 | UTOPIA INTERFACE CONFIGURATION              | . 297 |

|    | 12.4 | SPECIAL QUEUE CONFIGURATION MODES           | . 297 |

|    |      | 12.4.1 AAL0                                 | . 297 |

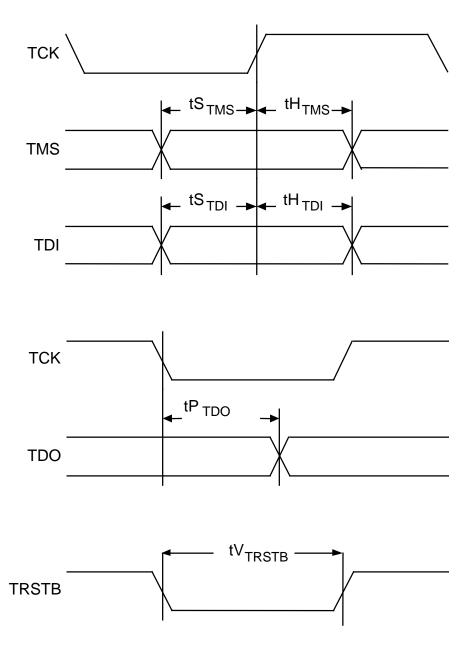

|    | 12.5 | JTAG SUPPORT                                | . 298 |

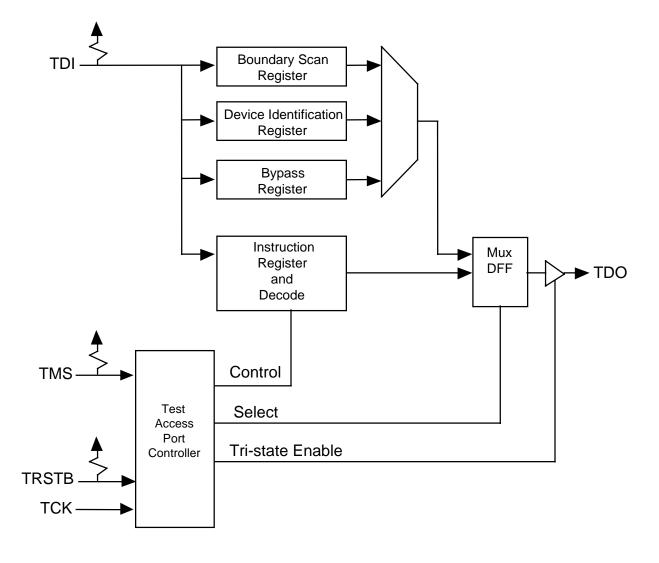

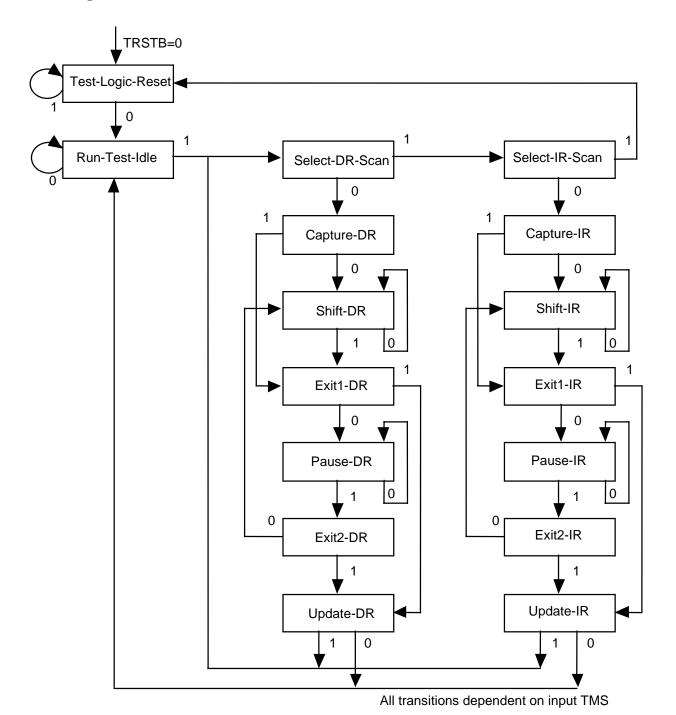

|    |      | 12.5.1 TAP CONTROLLER                       | . 299 |

| 13 | FUNC | CTIONAL TIMING                              | . 306 |

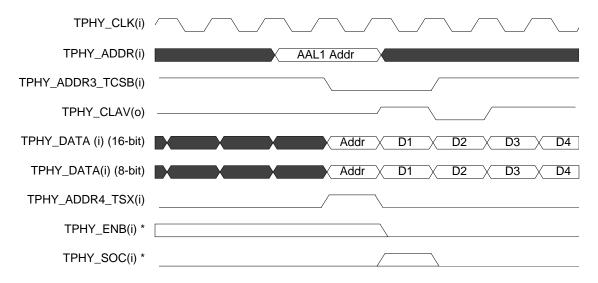

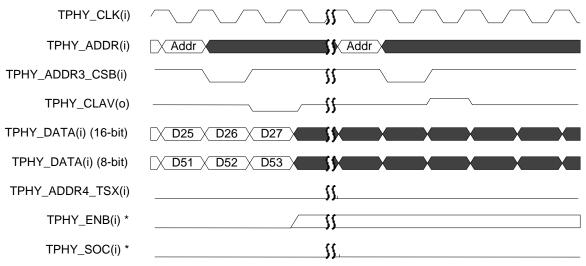

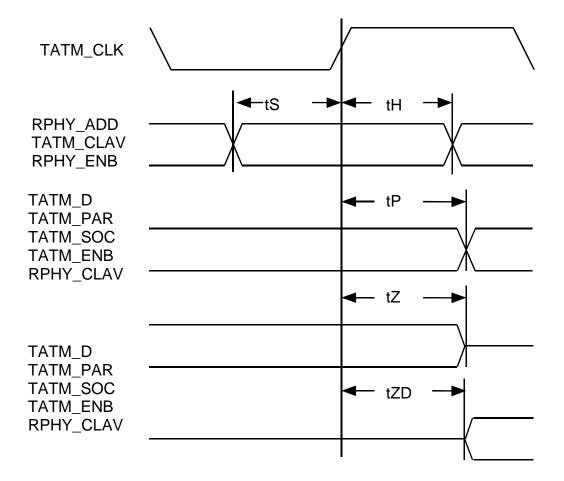

|    | 13.1 | SOURCE UTOPIA                               | . 307 |

|    | 13.2 | SINK UTOPIA                                 | . 312 |

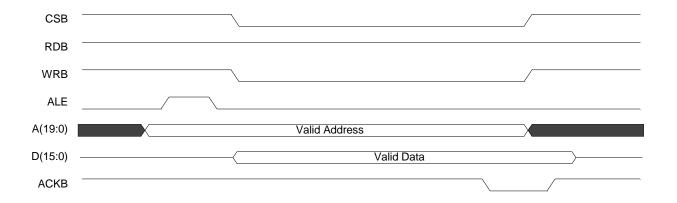

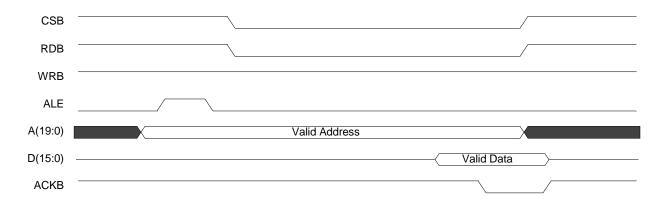

|    | 13.3 | PROCESSOR I/F                               | . 318 |

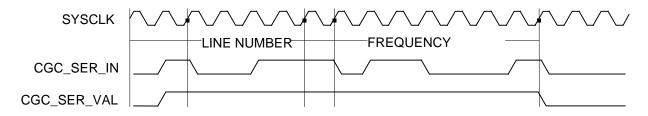

|    | 13.4 | EXTERNAL CLOCK GENERATION CONTROL I/F (CGC) | . 320 |

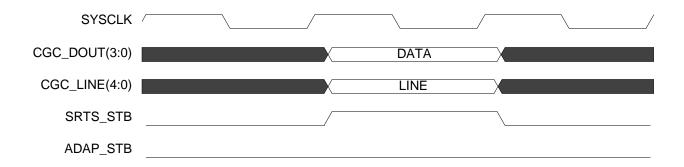

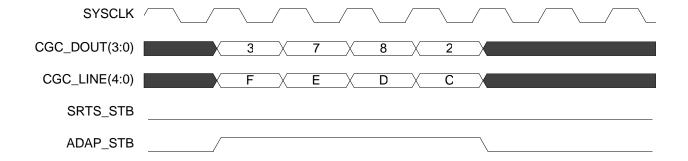

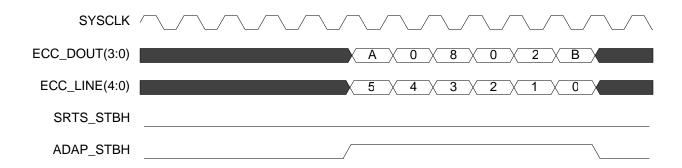

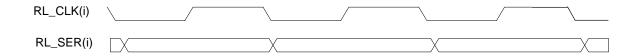

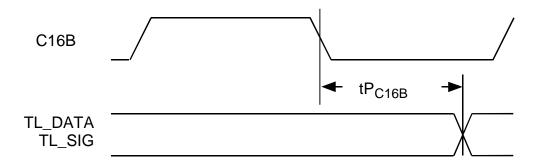

|    |      | 13.4.1 SRTS DATA OUTPUT                     | . 320 |

|    |      | 13.4.2 CHANNEL UNDERRUN STATUS OUTPUT       | . 321 |

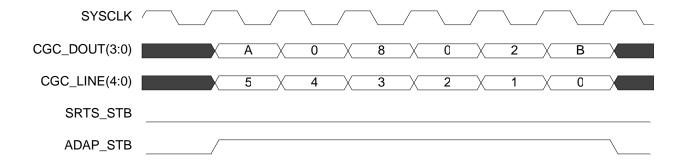

|    |      | 13.4.3 ADAPTIVE STATUS OUTPUT               | . 322 |

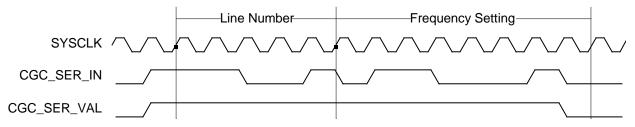

|    | 13.5 | EXT FREQ SELECT INTERFACE                   | . 323 |

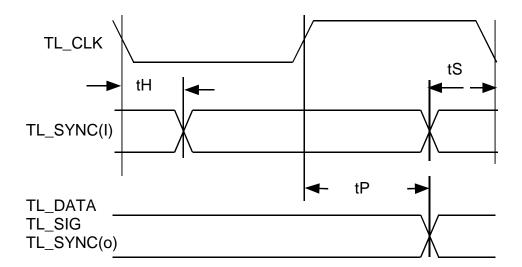

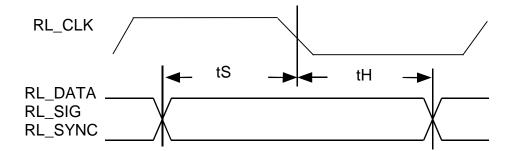

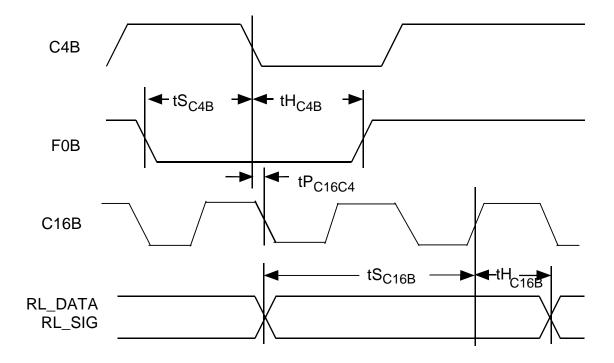

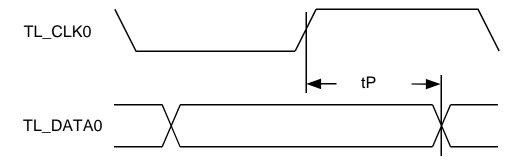

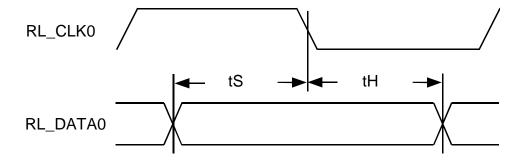

|    | 13.6 | LINE INTERFACE TIMING                       | . 324 |

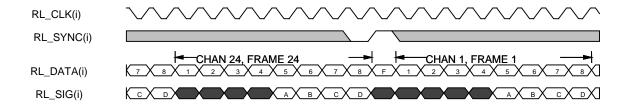

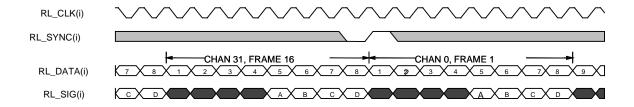

|    |      | 13.6.1 16 LINE MODE                         | . 324 |

|    |      | 13.6.2 H-MVIP TIMING                        | . 327 |

|    |      | 13.6.3 DS3/E3 TIMING                        | . 331 |

| 14 | ABSC | DLUTE MAXIMUM RATINGS                       | . 333 |

| ISSUE 2 | 8 LINK CES/DBCES AAL1 SAR |

|---------|---------------------------|

|         |                           |

| 15 | D.C.  | CHARACTERISTICS334                              |

|----|-------|-------------------------------------------------|

| 16 | A.C.  | TIMING CHARACTERISTICS336                       |

|    | 16.1  | RESET TIMING                                    |

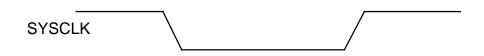

|    | 16.2  | SYS_CLK TIMING337                               |

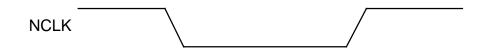

|    | 16.3  | NCLK TIMING                                     |

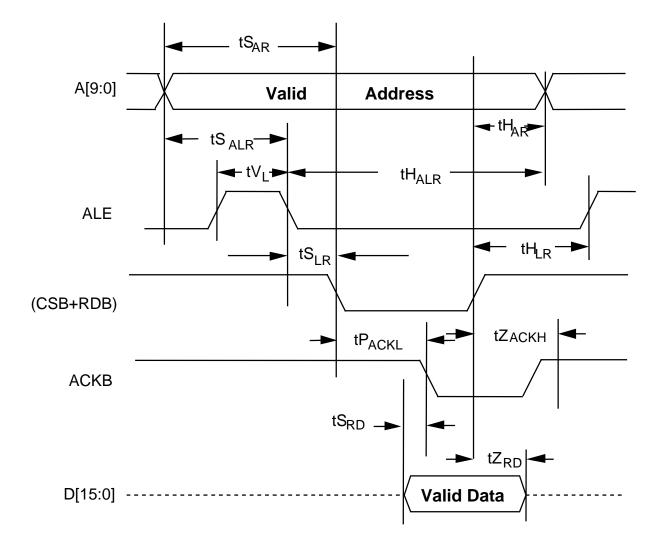

|    | 16.4  | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS |

|    | 16.5  | EXTERNAL CLOCK GENERATION CONTROL INTERFACE 343 |

|    | 16.6  | RAM INTERFACE344                                |

|    | 16.7  | UTOPIA INTERFACE                                |

|    | 16.8  | LINE I/F TIMING                                 |

|    |       | 16.8.1 DIRECT LOW SPEED TIMING                  |

|    |       | 16.8.2 H-MVIP TIMING                            |

|    |       | 16.8.3 HIGH SPEED TIMING                        |

|    | 16.9  | JTAG TIMING                                     |

| 17 | ORDI  | ERING AND THERMAL INFORMATION                   |

| 18 | MECH  | HANICAL INFORMATION357                          |

| 19 | DEFII | NITIONS359                                      |

8 LINK CES/DBCES AAL1 SAR

## **LIST OF REGISTERS**

ISSUE 2

| REGISTER 0X80000: RESET AND DEVICE ID REGISTER (DEV_ID_REG)239                         |

|----------------------------------------------------------------------------------------|

| REGISTER 0X80010: A1SP COMMAND REGISTER (A_CMD_REG) 240                                |

| REGISTER 0X80020 : A1SP ADD QUEUE FIFO REGISTER (A_ADDQ_FIFO)242                       |

| REGISTER 0X80030 : A1SP CLOCK CONFIGURATION REGISTER (A_CLK_CFG)243                    |

| REGISTER 0X80100: RAM CONFIGURATION REGISTER (RAM_CFG_REG)245                          |

| REGISTER 0X80120: UI COMMON CONFIGURATION REGISTER (UI_COMN_CFG)247                    |

| REGISTER 0X80121: UI SOURCE CONFIG REG (UI_SRC_CFG)249                                 |

| REGISTER 0X80122: UI SINK CONFIG REG (UI_SNK_CFG)251                                   |

| REGISTER 0X80123: SLAVE SOURCE ADDRESS CONFIG REGISTER (UI_SRC_ADD_CFG)253             |

| REGISTER 0X80124: SLAVE SINK ADDRESS CONFIG REGISTER (UI_SNK_ADD_CFG)254               |

| REGISTER 0X80125: UI TO UI LOOPBACK VCI (U2U_LOOP_VCI) 255                             |

| REGISTER 0X80200H, 01H 07H: LOW SPEED LINE N CONFIGURATION REGISTERS(LS_LN_CFG_REG)256 |

| REGISTER 0X80210H: LINE MODE REGISTER(LINE_MODE_REG) 257                               |

| REGISTER 0X81000: MASTER INTERRUPT REGISTER (MSTR_INTR_REG)259                         |

| REGISTER 0X81010: A1SP INTERRUPT REGISTER (A1SP_INTR_REG) 261                          |

| REGISTER 0X81020: A1SP STATUS REGISTER (A1SP_STAT_REG) 263                             |

| REGISTER 0X81030: A1SP TRANSMIT IDLE STATE FIFO (A1SP_TIDLE_FIFO)                      |

ISSUE 2

| REGISTER 0X81040: A1SP RECEIVE STATUS FIFO (A1SP_RSTAT_FIFO)268                    |

|------------------------------------------------------------------------------------|

| REGISTER 0X81100: MASTER INTERRUPT ENABLE REGISTER (MSTR_INTR_EN_REG)270           |

| REGISTER 0X81110: A1SP INTERRUPT ENABLE REGISTER (A1SP_EN_REG)271                  |

| REGISTER 0X81150: RECEIVE QUEUE ERROR ENABLE (RCV_Q_ERR_EN)273                     |

| REGISTER 0X82000-0X8200F: A1SP RX CHANNEL ACTIVE TABLE 275                         |

| REGISTER 0X82010-0X8201F: A1SP RX PENDING TABLE277                                 |

| REGISTER 0X82100-0X821FF: A1SP RX CHANGE POINTER TABLE (RX_CHG_PTR)279             |

| REGISTER 0X82200-0X8220F: A1SP TX CHANNEL ACTIVE TABLE 281                         |

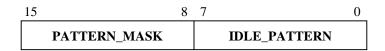

| REGISTER 0X82210-0X82217: A1SP PATTERN MATCHING LINE CONFIGURATION (PAT_MTCH_CFG ) |

| REGISTER 0X82220: A1SP IDLE DETECTION CONFIGURATION TABLE 284                      |

| REGISTER 0X82300-0X823FF: A1SP CAS/PATTERN MATCHING CONFIGURATION TABLE            |

| REGISTER 0X84000H: DLL CONFIGURATION REGISTER (DLL_CFG_REG)                        |

| REGISTER 0X84002H: DLL SW RESET REGISTER (DLL_SW_RST_REG) 290                      |

| REGISTER 0X84003H: DLL CONTROL STATUS REGISTER (DLL_STAT_REG)291                   |

ISSUE 2

8 LINK CES/DBCES AAL1 SAR

# **LIST OF FIGURES**

|             | AL1GATOR-8 IN AN INTEGRATED ACCESS DEVICE (IAD)<br>N | . 29 |

|-------------|------------------------------------------------------|------|

| FIGURE 3. A | AL1GATOR-8 IN AN APON ONU APPLICATION                | . 30 |

| FIGURE 5 -  | AAL1GATOR-8 INTERNAL BLOCK DIAGRAM                   | . 31 |

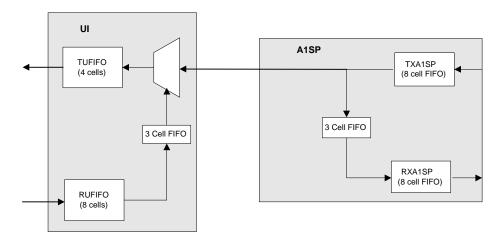

| FIGURE 6 E  | DATA FLOW AND BUFFERING IN THE UI AND THE A1SP<br>5  |      |

| FIGURE 8    | JI BLOCK DIAGRAM                                     | . 66 |

| FIGURE 10   | A1SP BLOCK DIAGRAM                                   | . 74 |

| FIGURE 12   | CAPTURE OF T1 SIGNALING BITS (SHIFT_CAS=0)           | . 76 |

| FIGURE 14   | CAPTURE OF E1 SIGNALING BITS (SHIFT_CAS=0)           | . 76 |

| FIGURE 16   | TRANSMIT FRAME TRANSFER CONTROLLER                   | . 76 |

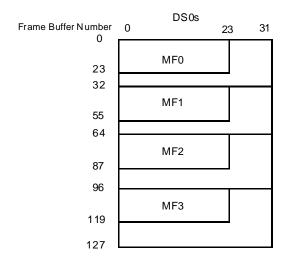

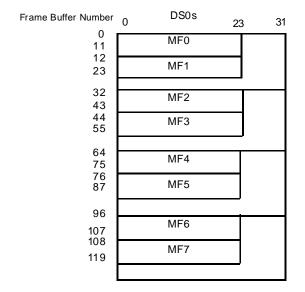

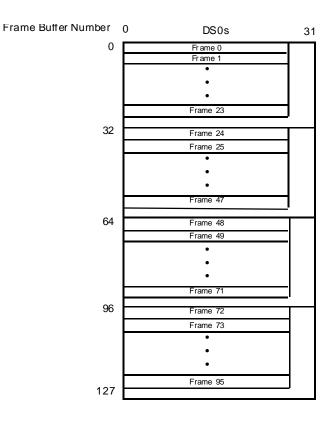

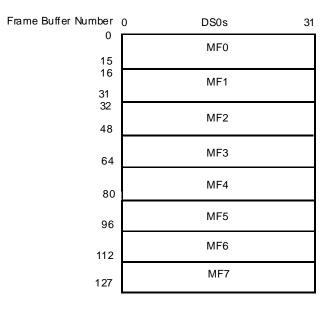

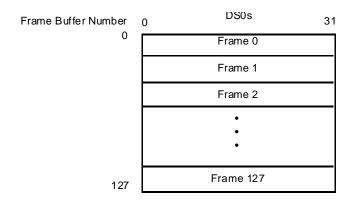

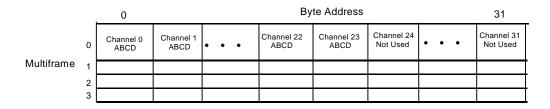

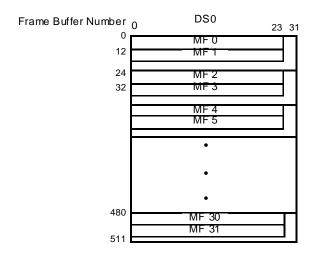

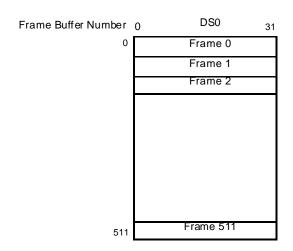

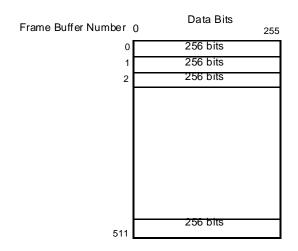

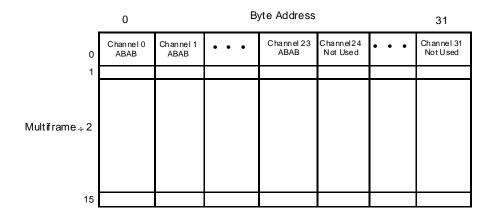

| FIGURE 18   | T1 ESF SDF-MF FORMAT OF THE T_DATA_BUFFER            | . 78 |

| FIGURE 20   | T1 SF-SDF-MF FORMAT OF THE T_DATA_BUFFER             | . 78 |

| FIGURE 22   | T1 SDF-FR FORMAT OF THE T_DATA_BUFFER                | . 79 |

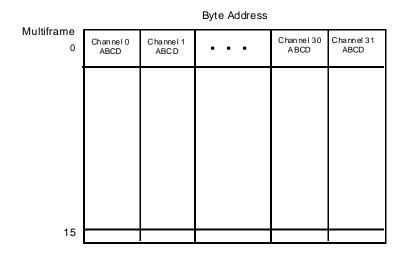

| FIGURE 24   | E1 SDF-MF FORMAT OF THE T_DATA_BUFFER                | . 80 |

|             | E1 SDF-MF WITH T1 SIGNALING FORMAT OF THE FFER       | . 80 |

| FIGURE 28   | E1 SDF-FR FORMAT OF THE T_DATA_BUFFER                | . 81 |

| FIGURE 30   | UNSTRUCTURED FORMAT OF THE T_DATA_BUFFER             | . 81 |

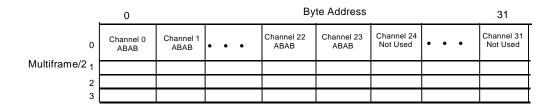

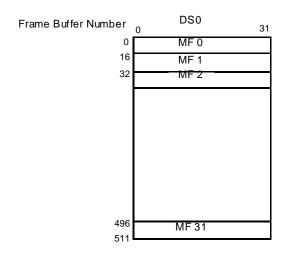

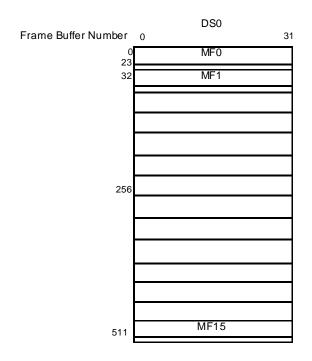

| FIGURE 32   | SDF-MF T1 ESF FORMAT OF THE T_SIGNALING_BUFFER       | . 82 |

| FIGURE 34   | SDF-MF T1 SF FORMAT OF THE T_SIGNALING BUFFER        | . 82 |

| FIGURE 36   | SDF-MF E1 FORMAT OF THE T_SIGNALING_BUFFER           | . 82 |

|             | SDF-MF E1 WITH T1 SIGNALING FORMAT OF THE G_BUFFER   | . 83 |

ISSUE 2

| FIGURE 40 | TRANSMIT SIDE SRTS FUNCTION                    | . 84 |

|-----------|------------------------------------------------|------|

|           | CAS IDLE DETECTION CONFIGURATION REGISTER      | . 85 |

| FIGURE 44 | CAS IDLE DETECTION INTERRUPT WORD              | . 86 |

|           | PROCESSOR CONTROLLED IDLE DETECTION INTERRUPT  |      |

|           | PROCESSOR CONTROLLED CONFIGURATION REGISTER    | . 87 |

| FIGURE 50 | TX CHANNEL ACTIVE/IDLE BIT TABLE STRUCTURE     | . 87 |

| FIGURE 52 | PAT_MTCH_CFG REGISTER STRUCTURE                | . 88 |

| FIGURE 53 | PATTERN MATCH IDLE DETECTION REGISTER STRUCTUR | E89  |

| FIGURE 55 | PATTERN MATCH IDLE DETECTION INTERRUPT WORD    | . 89 |

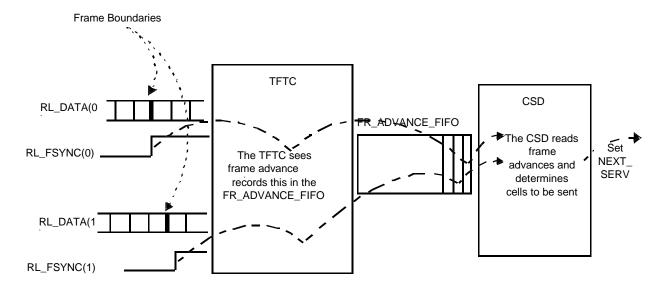

| FIGURE 57 | FRAME ADVANCE FIFO OPERATION                   | . 91 |

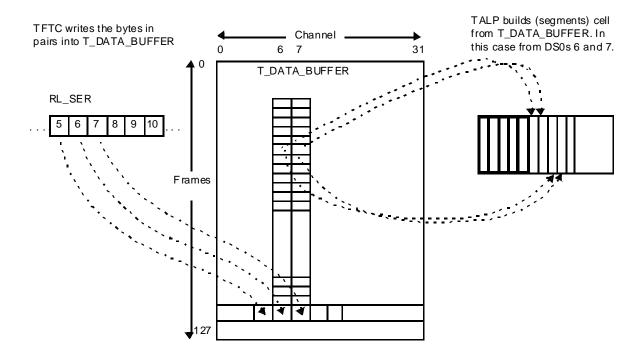

| FIGURE 59 | PAYLOAD GENERATION                             | . 99 |

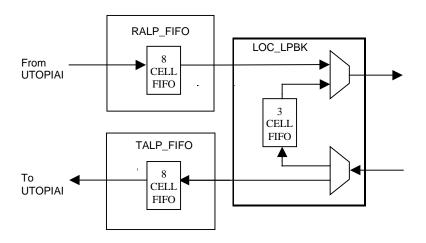

| FIGURE 61 | LOCAL LOOPBACK                                 | 102  |

| FIGURE 63 | CELL HEADER INTERPRETATION                     | 104  |

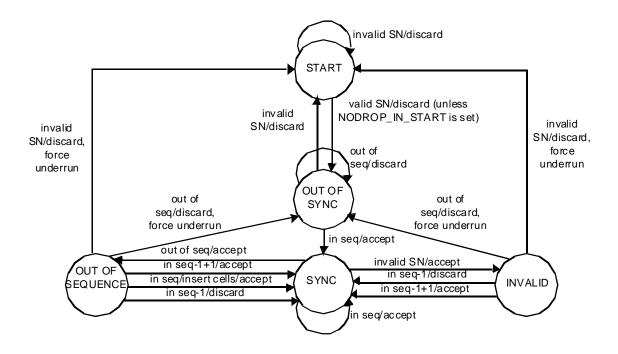

| FIGURE 65 | FAST SN ALGORITHM                              | 110  |

| FIGURE 67 | RECEIVE CELL PROCESSING FOR FAST SN            | 111  |

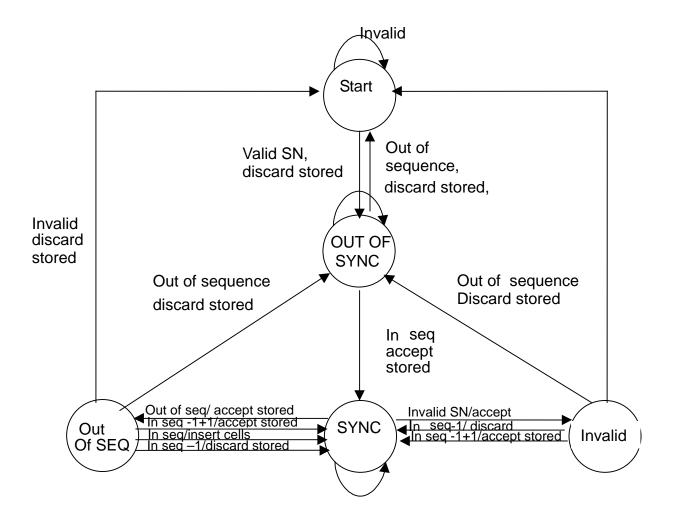

| FIGURE 69 | ROBUST SN ALGORITHM                            | 114  |

| FIGURE 71 | CELL RECEPTION                                 | 116  |

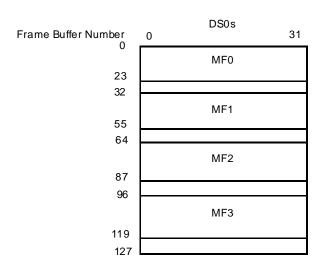

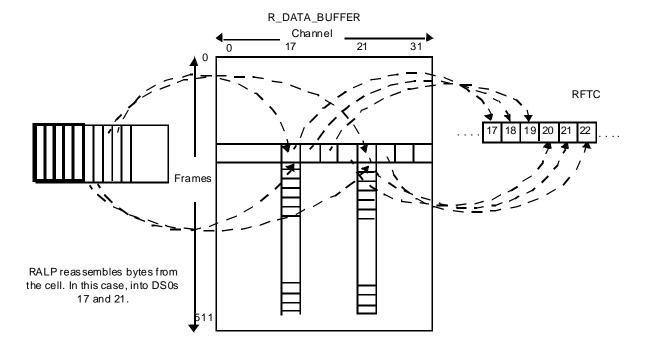

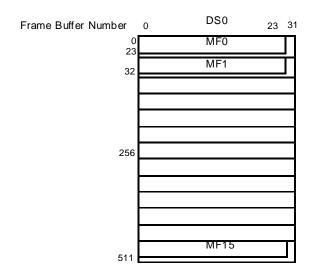

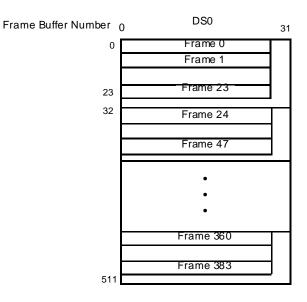

| FIGURE 73 | T1 ESF SDF-MF FORMAT OF THE R_DATA_BUFFER      | 117  |

| FIGURE 75 | T1 SF SDF-MF FORMAT OF THE R_DATA_BUFFER       | 117  |

| FIGURE 77 | T1 SDF-FR FORMAT OF THE R_DATA_BUFFER          | 118  |

| FIGURE 79 | E1 SDF-MF FORMAT OF THE R_DATA_BUFFER          | 118  |

|           | E1 SDF-MF WITH T1 SIGNALING FORMAT OF THE      | 119  |

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

| FIGURE 83 | E1 SDF-FR FORMAT OF THE R_DATA_BUFFER         | 119 |

|-----------|-----------------------------------------------|-----|

| FIGURE 85 | UNSTRUCTURED FORMAT OF THE R_DATA_BUFFER      | 120 |

| FIGURE 87 | T1 ESF SDF-MF FORMAT OF THE R_SIG_BUFFER      | 120 |

| FIGURE 89 | T1 SF SDF-MF FORMAT OF THE R_SIG_BUFFER       | 121 |

| FIGURE 91 | E1 SDF-MF FORMAT OF THE R_SIG_BUFFER          | 121 |

|           | E1 SDF-MF WITH T1 SIGNALING FORMAT OF THE FER | 122 |

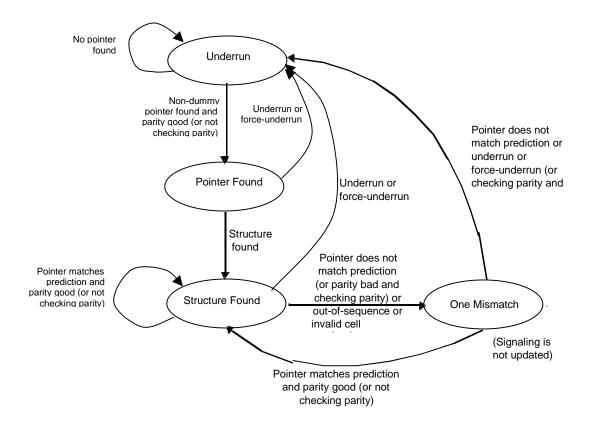

| FIGURE 49 | POINTER/STRUCTURE STATE MACHINE               | 127 |

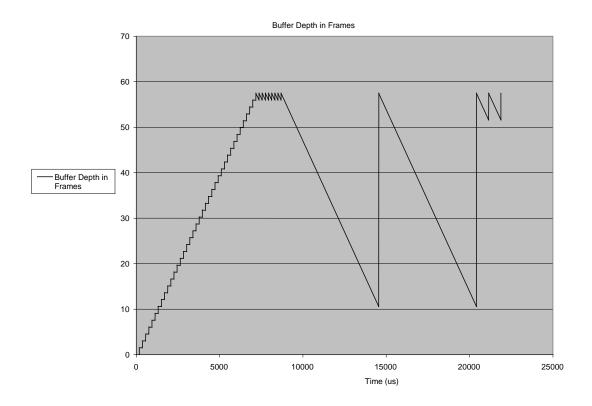

| FIGURE 96 | OVERRUN DETECTION                             | 129 |

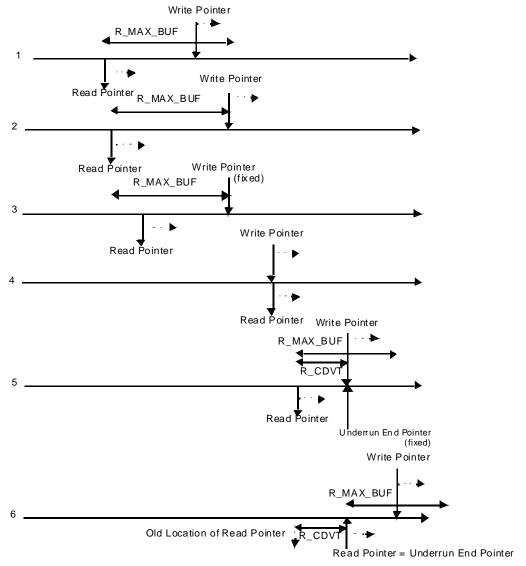

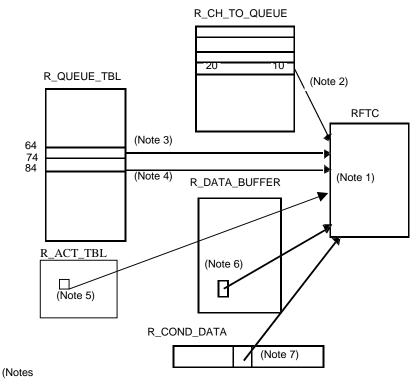

| FIGURE 52 | DBCES RECEIVE SIDE BUFFERING                  | 132 |

| FIGURE 54 | OUTPUT OF T1 SIGNALING BITS (SHIFT_CAS=0)     | 134 |

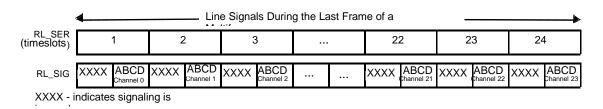

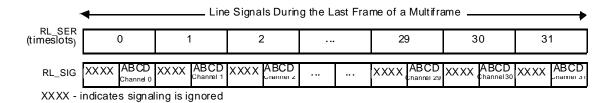

| FIGURE 56 | OUTPUT OF E1 SIGNALING BITS (SHIFT_CAS=0)     | 134 |

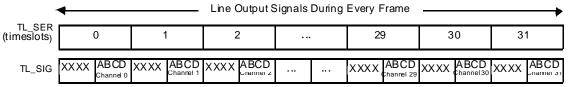

| FIGURE 58 | CHANNEL-TO-QUEUE TABLE OPERATION              | 136 |

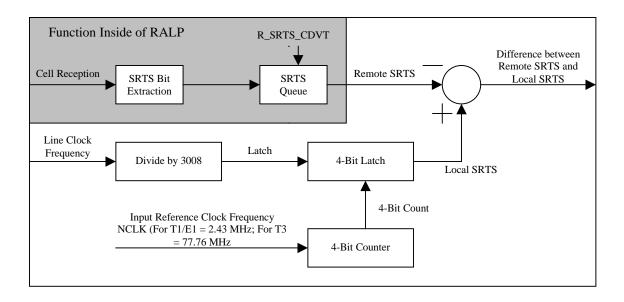

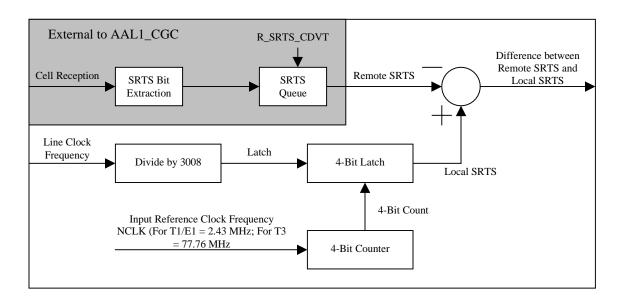

| FIGURE 60 | RECEIVE SIDE SRTS SUPPORT                     | 137 |

| FIGURE 62 | SRTS DATA                                     | 141 |

| FIGURE 64 | CHANNEL STATUS FUNCTIONAL TIMING              | 141 |

| FIGURE 66 | ADAPTIVE DATA FUNCTIONAL TIMING               | 143 |

| FIGURE 67 | EXT FREQ SELECT FUNCTIONAL TIMING             | 144 |

| FIGURE 69 | RECEIVE SIDE SRTS SUPPORT                     | 145 |

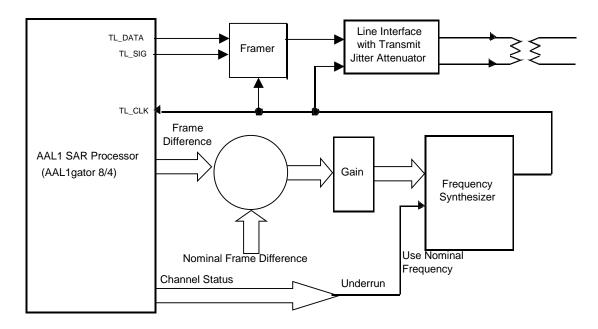

| FIGURE 71 | DIRECT ADAPTIVE CLOCK OPERATION               | 147 |

| FIGURE 73 | MEMORY MAP                                    | 152 |

| FIGURE 75 | A1SP SRAM MEMORY MAP                          | 152 |

| FIGURE 77 | CONTROL REGISTERS MEMORY MAP                  | 153 |

| FIGURE 79 | TRANSMIT DATA STRUCTURES MEMORY MAP           | 154 |

ISSUE 2

| FIGURE 81 RECEIVE DATA STRUCTURES                                       |

|-------------------------------------------------------------------------|

| FIGURE 83 NORMAL MODE REGISTERS MEMORY MAP 156                          |

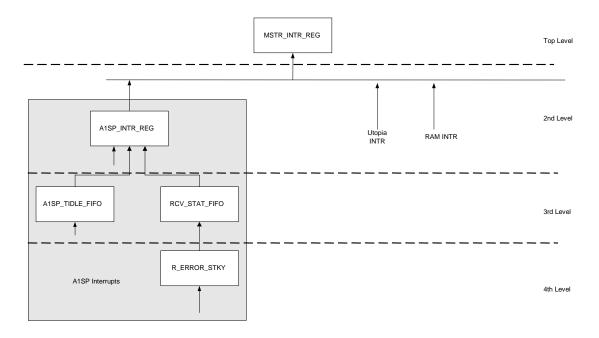

| FIGURE 85 INTERRUPT HIERARCHY                                           |

| FIGURE 87 ADDQ_FIFO WORD STRUCTURE                                      |

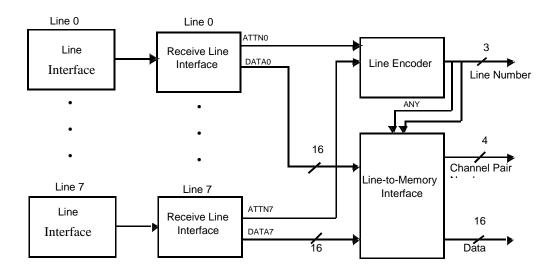

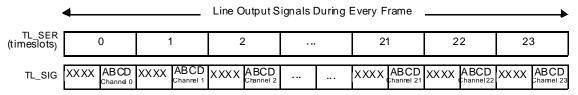

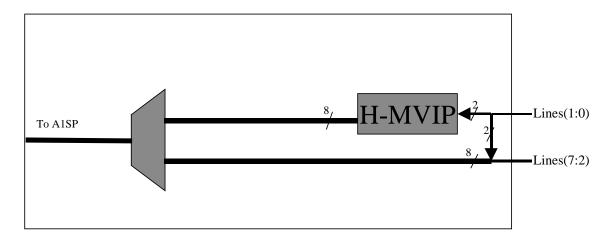

| FIGURE 89 LINE INTERFACE BLOCK ARCHITECTURE 164                         |

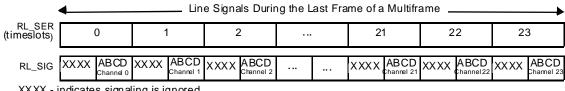

| FIGURE 91 CAPTURE OF T1 SIGNALING BITS167                               |

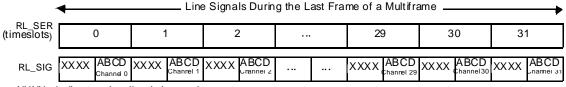

| FIGURE 93 CAPTURE OF E1 SIGNALING BITS                                  |

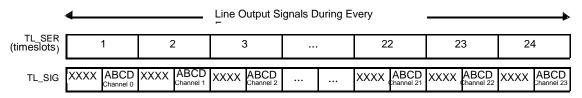

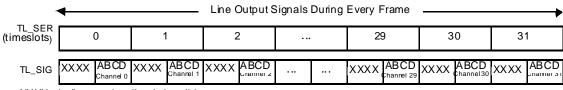

| FIGURE 95 OUTPUT OF T1 SIGNALING BITS                                   |

| FIGURE 97 OUTPUT OF E1 SIGNALING BITS                                   |

| FIGURE 99 SDF-MF FORMAT OF THE T_SIGNALING BUFFER 186                   |

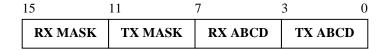

| FIGURE 100 R_CRC_SYNDROME MASK BIT TABLE LEGEND 207                     |

| FIGURE 101 BOUNDARY SCAN ARCHITECTURE                                   |

| FIGURE 102 TAP CONTROLLER FINITE STATE MACHINE300                       |

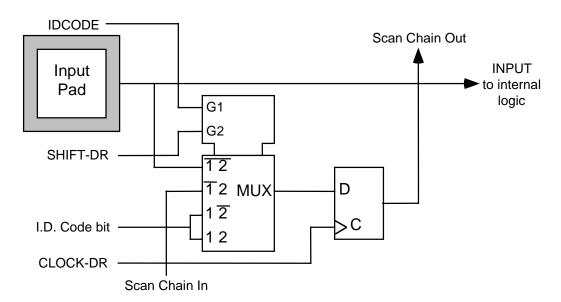

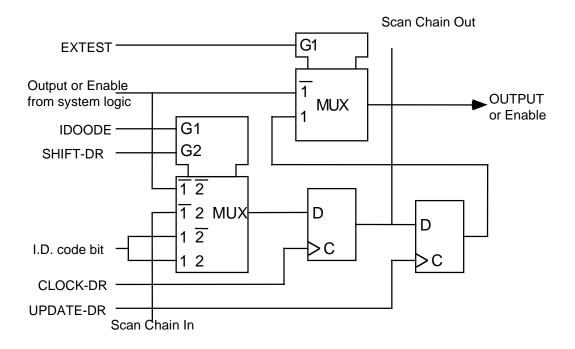

| FIGURE 103 INPUT OBSERVATION CELL (IN_CELL)303                          |

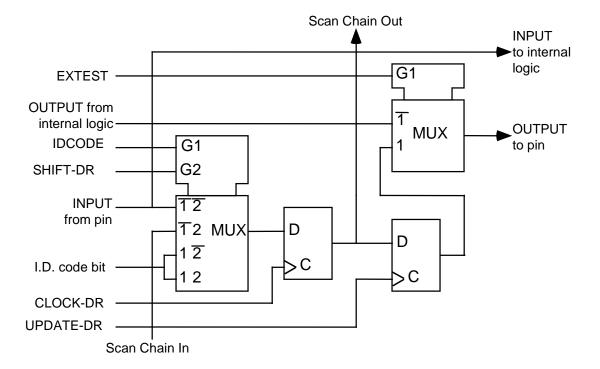

| FIGURE 104 OUTPUT CELL (OUT_CELL)                                       |

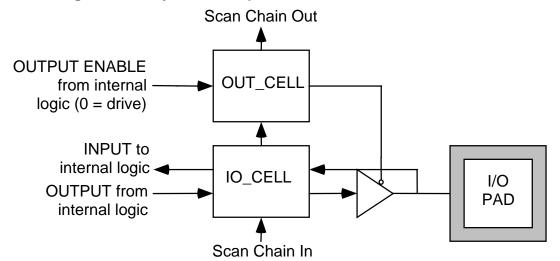

| FIGURE 105 BIDIRECTIONAL CELL (IO_CELL)                                 |

| FIGURE 106 LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS 305          |

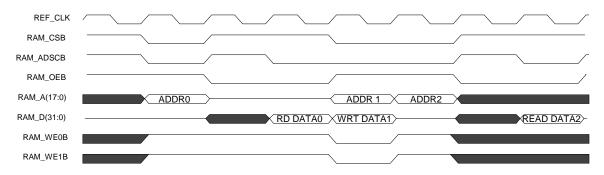

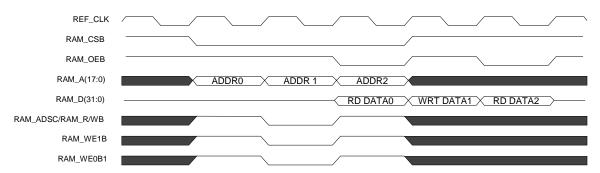

| FIGURE 107 PIPELINED SINGLE-CYCLE DESELECT SSRAM306                     |

| FIGURE 108 PIPELINED ZBT SSRAM                                          |

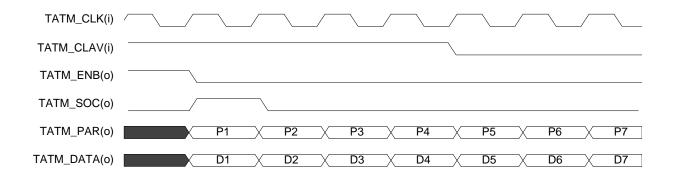

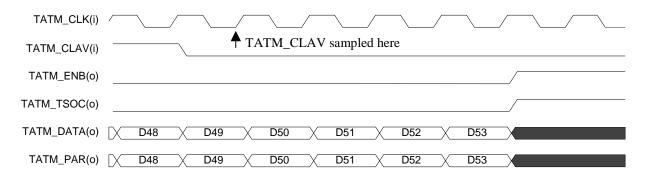

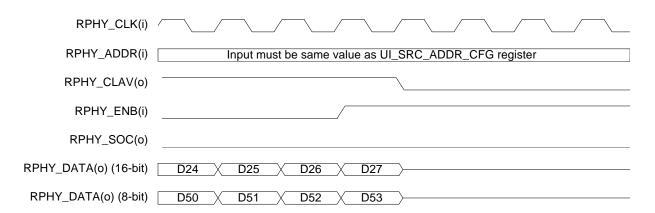

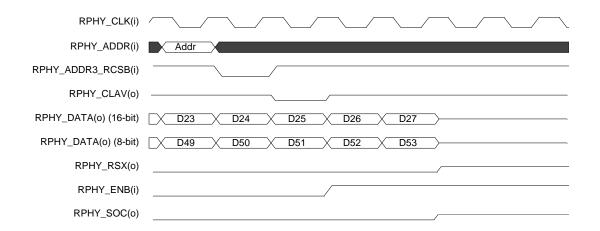

| FIGURE 109 SRC_INTF START OF TRANSFER TIMING (UTOPIA 1 ATM MODE) 307    |

| FIGURE 111 SRC_INTF END-OF-TRANSFER TIMING (UTOPIA 1 ATM MODE)308       |

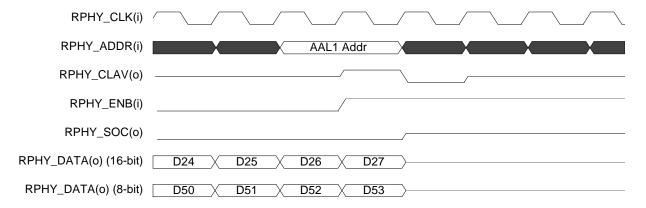

| FIGURE 113 UI_SRC_INTF START-OF-TRANSFER TIMING (UTOPIA 1 PHY MODE) 308 |

ISSUE 2

| FIGURE 114             | UI_SRC_INTF END-OF-TRANSFER (UTOPIA 1 PHY MODE)     | 309 |

|------------------------|-----------------------------------------------------|-----|

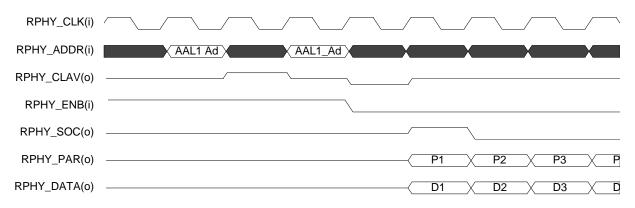

| FIGURE 116<br>MODE) 31 | UI_SRC_INTF START-OF-TRANSFER TIMING (UTOPIA 2 PHIO | łY  |

| FIGURE 118<br>MODE) 31 | UI_SRC_INTF END-OF-TRANSFER TIMING (UTOPIA 2 PHY IO |     |

| FIGURE 120<br>MODE) 31 | UI_SRC_INTF START-OF-TRANSFER TIMING (ANY-PHY PH    | ΙΥ  |

| FIGURE 122<br>MODE) 31 | UI_SRC_INTF END-OF-TRANSFER TIMING (ANY-PHY PHY I1  |     |

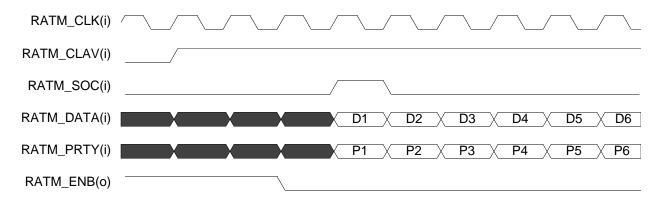

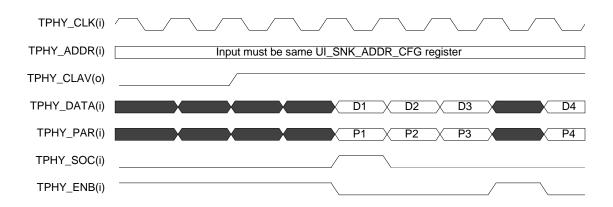

| FIGURE 124<br>MODE) 31 | SNK_INTF START-OF-TRANSFER TIMING (UTOPIA 1 ATM 12  |     |

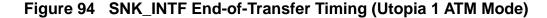

| FIGURE 126<br>MODE) 31 | SNK_INTF END-OF-TRANSFER TIMING (UTOPIA 1 ATM       |     |

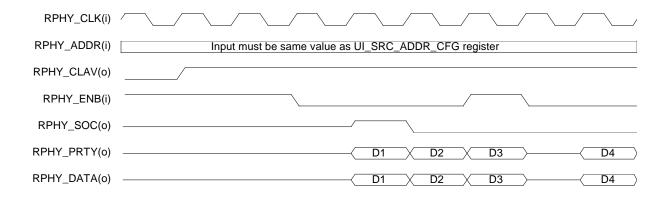

| FIGURE 128<br>MODE) 31 | SNK_INTF START-OF-TRANSFER TIMING (UTOPIA 1 PHY 14  |     |

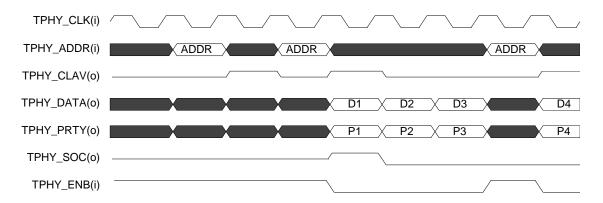

| FIGURE 130             | SNK_INTF START-OF-TRANSFER UTOPIA 2 PHY MODE 3      | 314 |

| FIGURE 132             | SNK_INTF CLAV DISABLE UTOPIA 2 ( PHY MODE)          | 315 |

| FIGURE 134             | SNK_INTF END-OF-TRANSFER UTOPIA 2 ( PHY MODE) 3     | 315 |

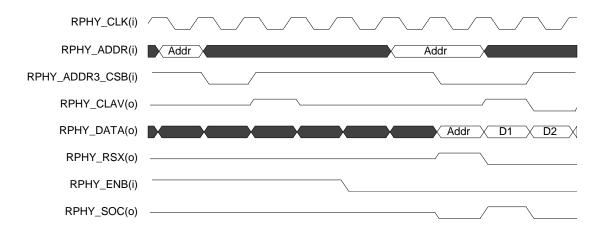

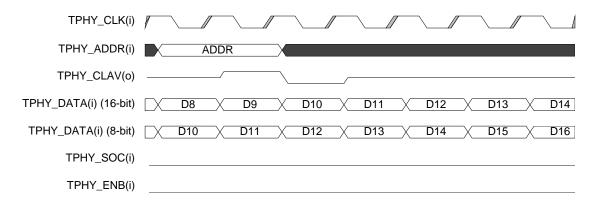

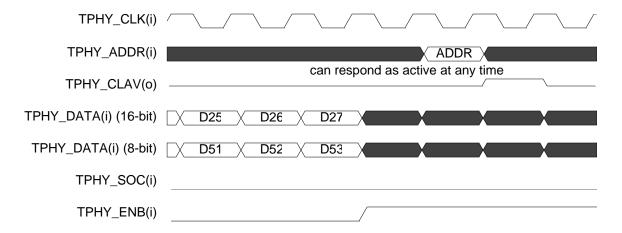

| FIGURE 136             | SNK_INTF START-OF-TRANSFER (ANY-PHY PHY MODE)3      | 316 |

| FIGURE 138             | SNK_INTF END-OF-TRANSFER (ANY-PHY PHY MODE) 3       | 317 |

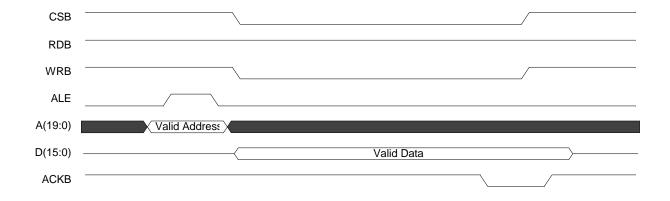

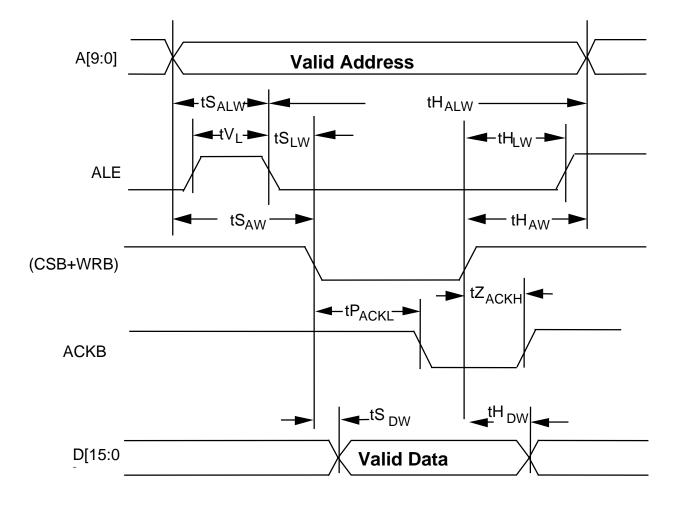

| FIGURE 140             | MICROPROCESSOR WRITE ACCESS                         | 318 |

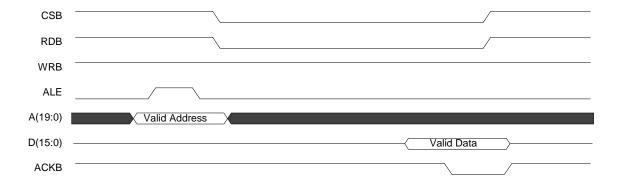

| FIGURE 142             | MICROPROCESSOR READ ACCESS                          | 319 |

| FIGURE 144             | MICROPROCESSOR WRITE ACCESS WITH ALE                | 319 |

| FIGURE 146             | MICROPROCESSOR READ ACCESS WITH ALE                 | 319 |

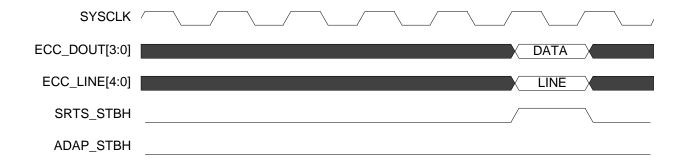

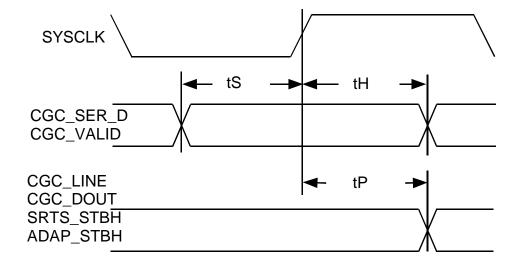

| FIGURE 148             | SRTS DATA                                           | 320 |

| FIGURE 150             | CHANNEL STATUS FUNCTIONAL TIMING                    | 321 |

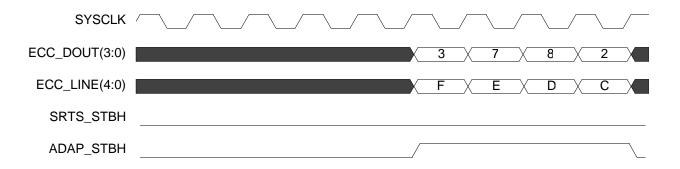

| FIGURE 152             | ADAPTIVE DATA FUNCTIONAL TIMING                     | 323 |

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

| FIGURE 154              | EXT FREQ SELECT FUNCTIONAL TIMING                    |

|-------------------------|------------------------------------------------------|

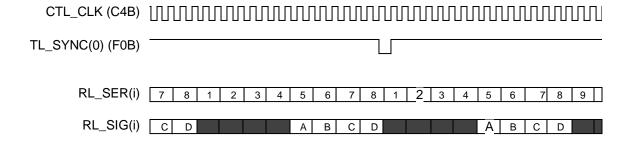

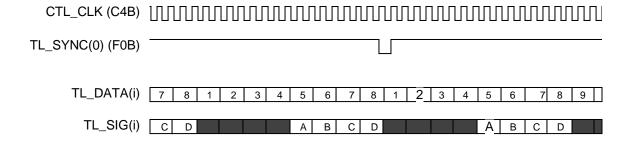

| FIGURE 156              | RECEIVE LINE SIDE T1 TIMING(RL_CLK = 1.544 MHZ) 324  |

| FIGURE 158              | RECEIVE LINE SIDE E1 TIMING(RL_CLK = 2.048 MHZ) 325  |

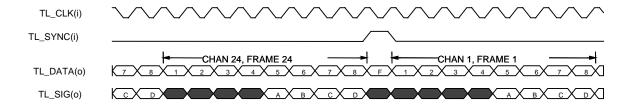

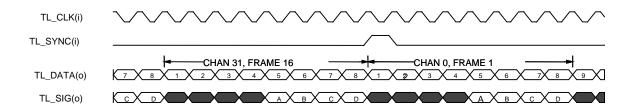

| FIGURE 160              | MVIP-90 RECEIVE FUNCTIONAL TIMING                    |

| FIGURE 161              | TRANSMIT LINE SIDE T1 TIMING(TL_CLK = 1.544 MHZ) 326 |

| FIGURE 163              | TRANSMIT LINE SIDE E1 TIMING(TL_CLK = 2.048 MHZ) 326 |

| FIGURE 165              | MVIP-90 TRANSMIT FUNCTIONAL TIMING                   |

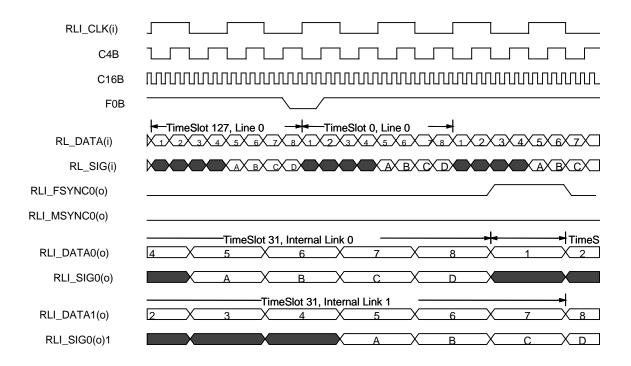

| FIGURE 166              | RECEIVE H-MVIP TIMING, CLOSE-UP VIEW                 |

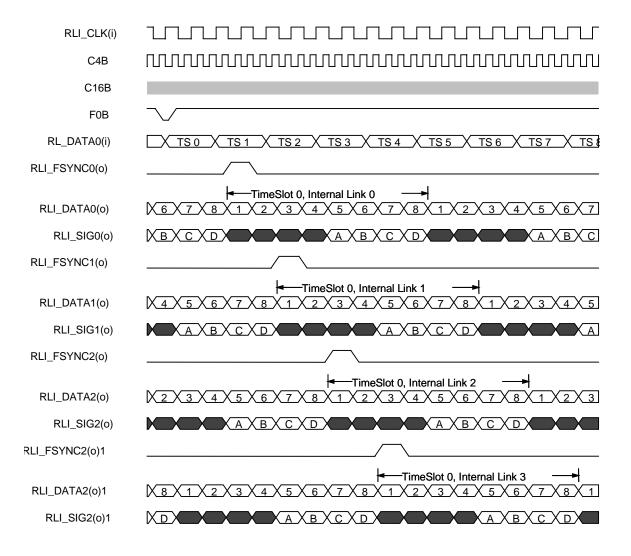

| FIGURE 168              | RECEIVE H-MVIP TIMING, EXPANDED VIEW                 |

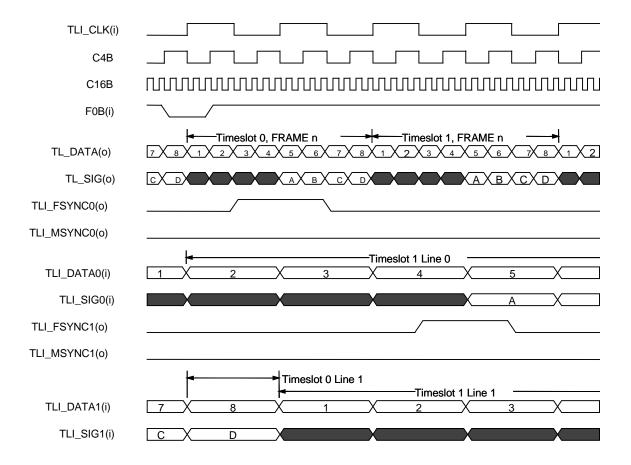

| FIGURE 169              | TRANSMIT H-MVIP TIMING, CLOSE-UP VIEW                |

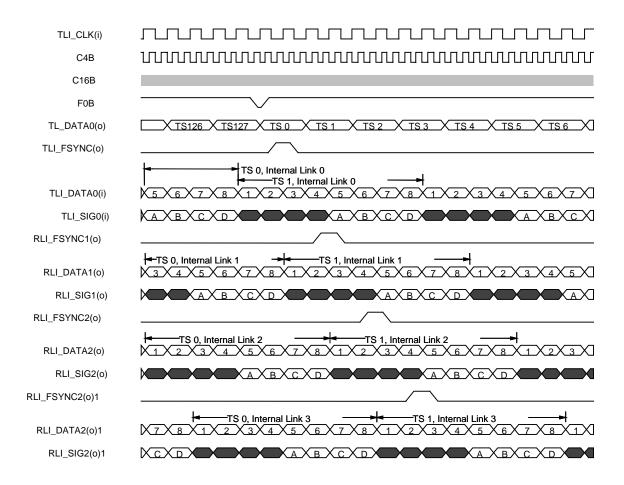

| FIGURE 171              | TRANSMIT H-MVIP TIMING, EXPANDED VIEW                |

| FIGURE 172              | RECEIVE HIGH-SPEED FUNCTIONAL TIMING 331             |

| FIGURE 174              | TRANSMIT HIGH-SPEED FUNCTIONAL TIMING                |

| FIGURE 176              | RSTB TIMING                                          |

| FIGURE 177              | SYS_CLK TIMING338                                    |

| FIGURE 178              | NCLK TIMING                                          |

| FIGURE 179              | MICROPROCESSOR INTERFACE READ TIMING 340             |

| FIGURE 180              | MICROPROCESSOR INTERFACE WRITE TIMING 342            |

| FIGURE 181<br>TIMING 34 | EXTERNAL CLOCK GENERATION CONTROL INTERFACE          |

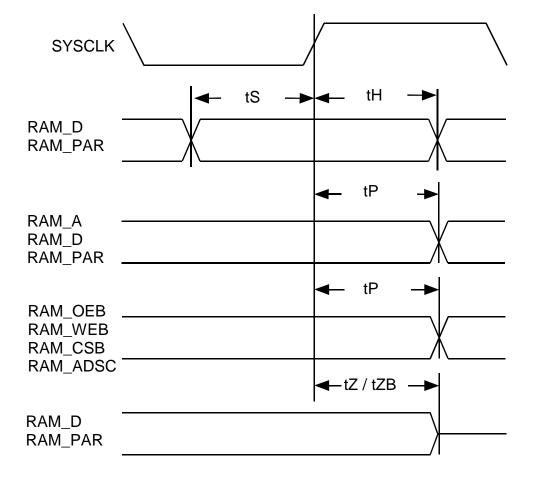

| FIGURE 182              | RAM INTERFACE TIMING                                 |

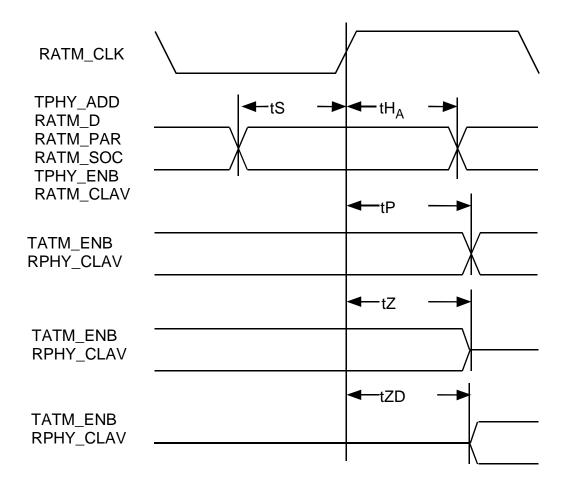

| FIGURE 183              | SINK UTOPIA INTERFACE TIMING                         |

| FIGURE 184              | SOURCE UTOPIA INTERFACE TIMING                       |

| FIGURE 185              | TRANSMIT LOW SPEED INTERFACE TIMING                  |

ISSUE 2

| FIGURE 186 | RECEIVE LOW SPEED INTERFACE TIMING    | 349   |

|------------|---------------------------------------|-------|

| FIGURE 187 | H-MVIP SINK DATA & FRAME PULSE TIMING | . 351 |

| FIGURE 188 | H-MVIP INGRESS DATA TIMING            | . 351 |

| FIGURE 189 | TRANSMIT HIGH SPEED TIMING            | . 352 |

| FIGURE 190 | RECEIVE HIGH SPEED INTERFACE TIMING   | 353   |

| FIGURE 191 | JTAG PORT INTERFACE TIMING            | 355   |

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

## **LIST OF TABLES**

| TABLE 1   | - LINE INTERFACE SIGNAL TABLE SELECTION                       | 50 |

|-----------|---------------------------------------------------------------|----|

| TABLE 3   | - LINE INTERFACE SUMMARY                                      | 56 |

| TABLE 5   | CFG_ADDR AND PHY_ADDR BIT USAGE IN SRC DIRECTION 6            | 39 |

| TABLE 7   | CFG_ADDR AND PHY_ADDR BIT USAGE IN SNK DIRECTION7             | 72 |

|           | MINIMUM PARTIAL CELL SIZE PERMITTED IF ALL CONNECTION<br>/E10 |    |

| TABLE 10  | CHANNEL STATUS                                                | 12 |

| TABLE 12  | BUFFER DEPTH14                                                | 13 |

| TABLE 14  | FREQUENCY SELECT – T1 MODE14                                  | 19 |

| TABLE 16  | FREQUENCY SELECT – E1 MODE                                    | 51 |

| TABLE 18  | LINE_MODE ENCODING16                                          | 33 |

| TABLE 19  | AAL1GATOR-8 MEMORY MAP17                                      | 72 |

| TABLE 20  | A1SP AND LINE CONFIGURATION STRUCTURES SUMMARY 17             | 73 |

| TABLE 21  | TRANSMIT STRUCTURES SUMMARY                                   | 79 |

| TABLE 22  | R_CRC_SYNDROME MASK BIT TABLE                                 | )7 |

| TABLE 23F | R_QUEUE_TBL FORMAT21                                          | 17 |

| TABLE 24  | REGISTER MEMORY MAP23                                         | 38 |

| TABLE 25  | COMMAND REGISTER MEMORY MAP23                                 | 38 |

| TABLE 26  | RAM INTERFACE REGISTERS MEMORY MAP24                          | 14 |

| TABLE 27  | UTOPIA INTERFACE REGISTERS MEMORY MAP24                       | 16 |

| TABLE 20  | CFG_ADDR AND PHY_ADDR BIT USAGE IN SRC DIRECTION2             | 53 |

| TABLE 29  | CFG_ADDR AND PHY_ADDR BIT USAGE IN SNK DIRECTION25            | 54 |

| TABLE 22  | LINE INTERFACE REGISTER MEMORY MAP SUMMARY 25                 | 55 |

ISSUE 2

| TABLE 23 | DIRECT LOW SPEED MODE REGISTER MEMORY MAP       | 255 |

|----------|-------------------------------------------------|-----|

| TABLE 24 | INTERRUPT AND STATUS REGISTERS MEMORY MAP       | 258 |

|          | IDLE CHANNEL DETECTION CONFIGURATION AND STATUS |     |

| TABLE 26 | DLL CONTROL AND STATUS REGISTERS MEMORY MAP     | 288 |

| TABLE 27 | CHANNEL STATUS                                  | 321 |

| TABLE 29 | FRAME DIFFERENCE                                | 322 |

| TABLE 31 | ABSOLUTE MAXIMUM RATINGS                        | 333 |

| TABLE 32 | AAL1GATOR-8 D.C. CHARACTERISTICS                | 334 |

| TABLE 33 | RTSB TIMING                                     | 336 |

| TABLE 34 | SYS_CLK TIMING                                  | 337 |

| TABLE 35 | NCLK TIMING                                     | 338 |

| TABLE 36 | MICROPROCESSOR INTERFACE READ ACCESS            | 339 |

| TABLE 37 | MICROPROCESSOR INTERFACE WRITE ACCESS           | 341 |

| TABLE 38 | EXTERNAL CLOCK GENERATION CONTROL INTERFACE     | 343 |

| TABLE 39 | RAM INTERFACE                                   | 344 |

| TABLE 40 | UTOPIA SOURCE AND SINK INTERFACE                | 345 |

| TABLE 41 | TRANSMIT LOW SPEED INTERFACE TIMING             | 348 |

| TABLE 42 | RECEIVE LOW SPEED INTERFACE TIMING              | 349 |

| TABLE 43 | H-MVIP SINK TIMING                              | 350 |

| TABLE 44 | H-MVIP SOURCE TIMING                            | 351 |

| TABLE 45 | TRANSMIT HIGH SPEED INTERFACE TIMING            | 352 |

| TABLE 46 | RECEIVE HIGH SPEED INTERFACE TIMING             | 353 |

| TABLE 47 | JTAG PORT INTERFACE                             | 354 |

ISSUE 2

PM73123 AAL1GATOR-8

| PMC-2000097 | ISSUE 2             | 8 LINK CES/DBCES AAL1 S       | AR |

|-------------|---------------------|-------------------------------|----|

| TABLE 48    | - AAL1GATOR-8 (PM73 | 123) ORDERING INFORMATION 356 |    |

ISSUE 2

8 LINK CES/DBCES AAL1 SAR

#### 1 FEATURES

The AAL1gator-8 AAL1 Segmentation And Reassembly (SAR) Processor is a monolithic single chip device that provides DS1, E1, E3, or DS3 line interface access to an ATM Adaptation Layer One (AAL1) Constant Bit Rate (CBR) ATM network. It arbitrates access to an external SRAM for storage of the configuration, the user data, and the statistics. The device provides a microprocessor interface for configuration, management, and statistics gathering. PMC-Sierra also provides a software device driver for the AAL1gator-8 device.

- Compliant with the ATM Forum's Circuit Emulation Services (CES) specification (AF-VTOA-0078), and the ITU-T I.363.1

- Supports Dynamic Bandwidth Circuit Emulation Services (DBCES). Compliant with the ATM Forum's DBCES specification (AF-VTOA-0085). Supports idle channel detection via processor intervention, CAS signaling, or data pattern detection. Provides idle channel indication on a per channel basis.

- Supports non-DBCES idle channel detection by activating a queue when any of its constituent time slots are active, and deactivating a queue when all of its constituent time slots are inactive.

- Provides AAL1 segmentation and reassembly of 8 individual E1 or T1 lines, 2 H-MVIP lines at 8 MHz, or 1 E3 or DS3 or STS-1 unstructured line.

•

- Provides a standard UTOPIA level 2 Interface which optionally supports parity and runs up to 52 MHz. Only Cell Level Handshaking is supported. The following modes are supported:

- 8/16-bit Level 2, Multi-Phy Mode (MPHY)

- 8/16-bit Level 1, SPHY

- 8-bit Level 1, ATM Master

- Provides an optional 8/16-bit Any-PHY slave interface.

- Supports up to 256 Virtual Channels (VC).

8 LINK CES/DBCES AAL1 SAR

- Supports n x 64 (consecutive channels) and m x 64 (non-consecutive channels) structured data format.

- Provides transparent transmission of Common Channel Signaling (CCS) and Channel Associated Signaling (CAS). Provides for termination of CAS signaling.

**ISSUE 2**

- Allows the CAS nibble to be coincident with either the first or second nibble of the data.

- Provides per-VC data and signaling conditioning in the transmit cell direction and per DS0 data and signaling conditioning in the transmit line direction. Data and signaling conditioning can be individually enabled. Includes DS3 AIS conditioning support in both directions. Transmit line conditioning options include programmable byte pattern, pseudo-random pattern or old data. Conditioning automatically occurs on underruns.

- In Cell Transmit direction, provides per-VC configuration of time slots allocated, CAS signaling support, partial cell size, data and signaling conditioning, ATM Cell header definition. Generates AAL1 sequence numbers, pointers and SRTS values in accordance with ITU-T I.363.1. Multicast connections are supported.

- In Cell Transmit direction provides counters for:

- Conditioned cells transmitted for each queue

- Cells which were suppressed for each gueue

- Total number of cells transmitted for each queue

- In Cell Receive direction, provides per-VC configuration of time slots allocated, CAS signaling support, partial cell size, sequence number processing options, cell delay variation tolerance buffer depth, maximum buffer depth. Processes AAL1 headers in accordance with ITU-T I.363.1.

- In Cell Receive direction, supports the Fast Sequence Number processing algorithm on all types of connections and Robust Sequence Number processing on Unstructured Data Format (UDF) connections. Cells are inserted/dropped to maintain bit integrity on lost or misinserted cells. Bit integrity is maintained through any single errored cell or up to six lost cells. Bit integrity can also optionally be maintained even if an underrun occurs. Pointer bytes, signaling bytes,

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

and bitmask bytes are taken into account. Cell insertion options include a programmable single byte pattern, pseudo-random data, or old data.

- In Cell Receive direction provides counters for the following events which include all counters required by the ATM Forum's CES-IS 2.0 MIB:

- Incorrect sequence numbers per queue

- Incorrect sequence number protection fields per queue

- Total number of received cells per queue

- Total number of dropped cells per queue

- Total number of underruns per queue

- Total number of lost cells per queue

- Total number of overruns per queue

- Total number of reframes per queue

- Total number of pointer parity errors per queue

- Total number of misinserted cells per queue

- Total number of OAM or non-data cells received

- Total number of OAM or non-data cells dropped.

- For each receive queue the following sticky bits are maintained:

- Cell received

- Structured pointer rule error detected

- DBCES bitmask parity error

- Cell dropped due to blank allocation table

- Cells dropped due to pointer search

- Cell dropped due to forced underrun

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

- Cell dropped due to sequence number processing algorithm

- Valid pointer was received

- Pointer parity error detected

- SRTS resume from an underrun condition

- SRTS underrun occurred

- Resume occurred from an underrun condition

- Pointer reframe occurred

- Overrun condition detected

- Cell received while in an underrun

- Supports AAL0 mode, selectable on a per VC basis.

- Provides system side loopback support. When enabled and the

incoming VCI matches the programmable loopback VCI, the cell

received on the Receive UTOPIA interface is looped back to the

Transmit UTOPIA interface. Alternatively the UTOPIA interface can be

put into remote loopback mode where all incoming cells are looped

back out. Provides line side loopback, enabled on a per queue basis,

which can loop a single channel or any group of channels which can

be mapped to a single queue.

- Provides a patented frame based calendar queue service algorithm with anti-clumping add-queue mechanism that produces minimal Cell Delay Variation (CDV). In UDF mode uses non-frame based scheduling to optimize CDV.

- Queues are added by making entries into an add-queue FIFO to minimize queue activation overhead. An offset can be configured when queue is added to distribute cell build times to minimize CDV due to clumping.

- Provides single maskable, open-collector interrupt with master interrupt register to facilitate interrupt processing. The master interrupt register indicates the following conditions each of which can be masked:

- Error/status condition with the AAL1 block

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

- Ram parity error

- UTOPIA parity error

- Transmit UTOPIA FIFO is full

- Transmit UTOPIA transfer error

- UTOPIA loopback FIFO is full

- UTOPIA runt cell is detected.

- For the AAL1 block the following conditions can cause an interrupt, each of which can be masked. A 64 entry FIFO is used to track receive and transmit status.

- A receive queue sticky bit was just set (individual mask per sticky bit)

- Receive queue entered underrun state

- Receive queue exited underrun state

- DBCES bitmask changed

- Receive Status FIFO overflow

- Transmit Frame Advance FIFO full

- Reception of OAM cells

- Change in idle state of a channel enabled for idle channel detection

- Transmit Channel Idle State change FIFO overflow

- Line frame resync event

- Transmit ATM Layer Processor (TALP) FIFO full

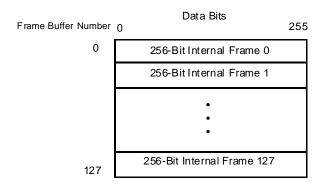

- Provides a 16-bit microprocessor interface to internal registers, and one external 128K x 16(18) (10 ns) Pipelined Single-Cycle Deselect Synchronous SRAMs, or Synchronous ZBT SRAMs.

PMC-2000097

ISSUE 2

- Provides a transmit buffer which can be used for Operations, Administration and Maintenance (OAM) cells as well as any other user-generated cells such as AAL5 cells for ATM signaling. A corresponding receive buffer exists for the reception of OAM cells or non-AAL1 data cells.

- Includes an internal E1/T1 clock synthesizer for each line which can generate a nominal E1/T1 clock or be controlled via Synchronous Residual Time Stamp (SRTS) clock recovery method in Unstructured Data Format (UDF) mode or a programmable weighted moving average adaptive clocking algorithm. DS3 and E3 SRTS or adaptive clocking is supported using an external clock synthesizer and the clock control port.

- The clock synthesizers can also be controlled externally to provide customization of SRTS or adaptive algorithms. SRTS can also be disabled via a hardware input. Adaptive and SRTS information is output to a port for external processing for both low speed and high speed mode, if needed. Buffer depth is provided in units of bytes. The synthesizer can be set to 256 discrete frequencies between either +/-100 ppm for E1 or +/-200 ppm for T1.

- Low-power 2.5 Volt CMOS technology with 3.3 Volt, 5 Volt tolerant I/O.

- 324-pin fine pitch plastic ball grid array (PBGA) package.

ISSUE 2 8 LINK CES/DBCES AAL1 SAR

## 2 **APPLICATIONS**

- Multi-service ATM Switch

- ATM Access Concentrator

- Digital Cross Connect

- Computer Telephony Chassis with ATM infrastructure

- Wireless Local Loop Back Haul

- ATM Passive Optical Network Equipment

8 LINK CES/DBCES AAL1 SAR

#### 3 REFERENCES

Applicable Recommendations and Standards.

ISSUE 2

- ANSI T1 Recommendation T1.403, Network-to-Customer Installation DS1 Metallic Interface, NY, NY, 1995.

- ANSI T1 Recommendation T1.630, Broadband ISDN-ATM Adaptation Layer for Constant Bit Rate Services, Functionality and Specification, NY, NY, 1993.

- 3. ATM Forum, ATM User Network Interface (UNI) Specification, V 3.1, Foster City, CA USA, September 1994.

- 4. ATM Forum, Circuit Emulation Service Interoperability Specification (CES-IS), V. 2.0, Foster City, CA USA, August 1996.

- 5. ATM Forum, Specifications of (DBCES) Dynamic Bandwidth Utilization in 64Kbps Time Slot Trunking Over ATM Using CES, Foster City, CA USA, (AF-VTOA-0085) July 1997.

- 6. ATM Forum, UTOPIA, an ATM-PHY Layer Specification, Level 1, V. 2.01, Foster City, CA USA, March 1994.

- 7. ATM Forum, UTOPIA, an ATM-PHY Layer Specification, Level 2, V. 1.0, Foster City, CA USA, June 1995.

- 8. ITU-T Recommendation G.703, Physical/Electrical Characteristics of Hierarchical Digital Interfaces, April 1991.

- 9. ITU-T Recommendation I.363.1, B-ISDN ATM Adaptation Layer (AAL) Specification, July 1995.

- 10.ITU-T Recommendation G.823, The Control of Jitter and Wander within Digital Networks Which Are Based on the 2048 kbit/s Hierarchy, March 1993.

- 11.ITU-T Recommendation G.824 The Control of Jitter and Wander within Digital Networks Which Are Based on the 1544 kbit/s Hierarchy, March 1993.

- 12. PMC-971268, "High density T1/E1 framer with integrated VT/TU mapper AND M13 multiplexer" (TEMUX), 2000, Issue 5.

- 13. GO-MVIP, "MVIP-90 Standard" Release 1.1, October 1994.

PMC-2000097

8 LINK CES/DBCES AAL1 SAR

14. GO-MVIP, "H-MVIP Standard" Release 1.1a, January 1997.

ISSUE 2

8 LINK CES/DBCES AAL1 SAR

#### 4 APPLICATION EXAMPLES

ISSUE 2

An essential function for ATM networks is to emulate existing Time Division Multiplexing (TDM) circuits. Since most voice and data services are currently provided by TDM circuits, seamless interworking between TDM and ATM has become a system requirement. The ATM Forum has standardized an internetworking function that satisfies this requirement in the Circuit Emulation Service (CES) Specification. The AAL1gator-8 is a direct implementation of that service specification in silicon, including the Nx64 channelized service and support of CAS.

#### 4.1 Integrated Access Device

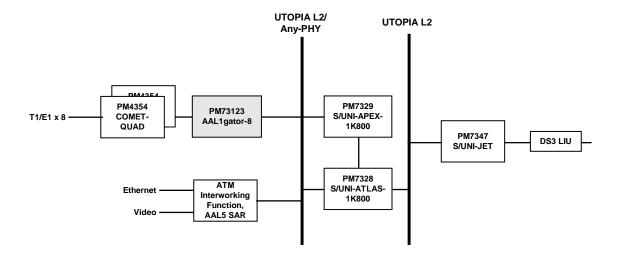

An Integrated Access Device (IAD) consolidates voice, data, Internet, and video wide-area network services using ATM over shared T1/E1 lines. IADs can also unify the functions of many different types of equipment including CSUs, DSUs and multiplexers. Figure 1 shows the AAL1gator-8 connected to PM4354 COMET-QUADs, a PM7329 S/UNI-APEX-1K800 Traffic Manager, a PM7328 S/UNI-ATLAS-1K800 ATM Layer device and the PM7347 S/UNI-JET.

Figure 1. AAL1gator-8 in an Integrated Access Device (IAD) Application.

8 LINK CES/DBCES AAL1 SAR

#### 4.2 ATM Passive Optical Networks (APON)

**ISSUE 2**

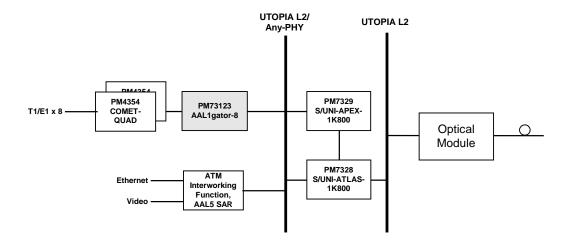

The general architecture of a Passive Optical Network (PON) access network consists of two key elements: the Optical Line Termination (OLT) and the Optical Network Unit (ONU). The OLT is connected to the ONU through a point-to-multipoint Passive Optical Network that consists of fiber, splitters and other passive components. Typically, up to 32 ONUs are connected to a single OLT, depending on the splitting factor. OLTs are typically located in local exchanges and ONUs on street locations, in buildings or even in homes. Figure 2 shows the use of the AAL1gator-8 in an ONU application supporting CES functions.

Figure 2. AAL1gator-8 in an APON ONU Application.

#### 5 **BLOCK DIAGRAM**

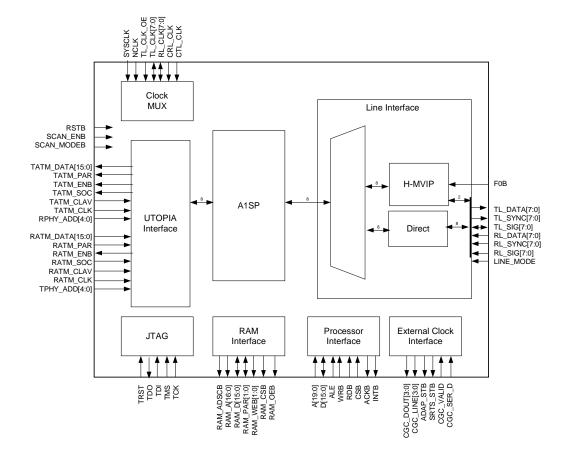

The AAL1gator-8 contains an AAL1 SAR Processor (A1SP) which performs the segmentation and re-assembly of the AAL1 cells. The A1SP block interfaces to a common UTOPIA interface on one side and a line Interface block on the other side, which can be configured to support several different line protocols. The A1SP block connects to the RAM interface. The processor interface block, which also contains the external clock control interface, is shared by all blocks. The AAL1gator-8 supports 8 serial lines.

Figure 3 - AAL1gator-8 Internal Block Diagram

ISSUE 2

8 LINK CES/DBCES AAL1 SAR

#### 6 **DESCRIPTION**

The AAL1gator-8 AAL1 Segmentation And Reassembly (SAR) Processor is a monolithic single chip device that provides DS1, E1, E3, or DS3 line interface access to an ATM Adaptation Layer One (AAL1) Constant Bit Rate (CBR) ATM network. It arbitrates access to an external SRAM for storage of the configuration, the user data, and the statistics. The device provides a microprocessor interface for configuration, management, and statistics gathering. PMC-Sierra also provides a software device driver for the AAL1gator-8 device.

8 LINK CES/DBCES AAL1 SAR

#### 7 PIN DIAGRAM

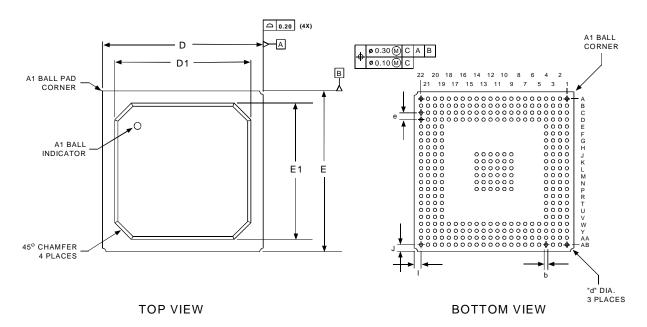

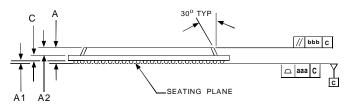

The AAL1gator-8 is manufactured in a 324 pin, fine pitch, plastic ball grid array (PBGA) package. (23mm x 23 mm)

ISSUE 2

Bottom View of AAL1gator-8

|    | 22             | 21              | 20               | 19               | 18               | 17            | 16               | 15               | 14               | 13           | 12           | 11               | 10                | 9                 | 8                 | 7                 | 6                | 5                | 4                  | 3                  | 2                  | 1                  |     |

|----|----------------|-----------------|------------------|------------------|------------------|---------------|------------------|------------------|------------------|--------------|--------------|------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|-----|

| Α  | PQH            | RL_CLK<br>[7]   | TL_CLK<br>[7]    | TL_SYNC<br>[7]   | PPH              | RAM_D<br>[15] | RAM_OE<br>B      | RAM_D<br>[10]    | SCAN_E<br>NB     | RAM_D<br>[4] | PPL          | RAM_WE<br>B [1]  | RAM_PA<br>R [0]   | RAM_AD<br>DR [14] | RAM_AD<br>DR [10] | PCH               | RAM_AD<br>DR [6] | RAM_AD<br>DR [3] | RAM_AD<br>DR [1]   | TMS                | SYSCLK             |                    | Α   |

| В  | TL_SYNC<br>[6] | RL_SYN<br>C [7] | RL_SIG<br>[7]    | TL_DATA<br>[7]   | LINE_MO<br>DE    | RAM_D<br>[9]  | RAM_D<br>[14]    | RAM_D<br>[11]    | RAM_D<br>[8]     | RAM_D<br>[5] | RAM_D<br>[1] | RAM_AD<br>DR [8] | RAM_WE<br>B [0]   | RAM_AD<br>DR [13] | RAM_CS<br>B       | RAM_AD<br>DR [7]  | RAM_AD<br>DR [4] | TDO              | PPL                | TCLK               |                    | TATM_D<br>ATA [14] | В   |

| С  | RL_SIG<br>[6]  | TL_CLK<br>[6]   | RL_SYN<br>C [6]  | PPL              | TL_SIG<br>[7]    | PPL           | CTL_CLK          | RAM_D<br>[13]    | PCH              | RAM_D<br>[6] | RAM_D        | PCL              | RAM_AD<br>DR [16] | RAM_AD<br>DR [12] | RAM_AD<br>DR [9]  | RAM_AD<br>DR [5]  | RAM_AD<br>DR [2] | RAM_AD<br>DR [0] | TDI                | PPL                | TATM_D<br>ATA [15] | RPHY_A<br>DD_RSX   | С   |

| D  | PQL            | TL_SIG<br>[6]   | RL_DATA<br>[7]   | PCL              | CRL_CLK          | RAM_D<br>[12] | PQH              | PPL              | RAM_D<br>[7]     | RAM_D<br>[3] | RAM_D<br>[0] | PPH              | RAM_PA<br>R [1]   | RAM_AD<br>DR [15] | PPL               | RAM_AD<br>DR [11] | RAM_AD<br>SCB    | PQL              | PPH                | TATM_P<br>AR       | TATM_D<br>ATA [13] | TATM_D<br>ATA [11] | D   |

| E  | RL_DATA<br>[6] |                 | _                | TL_CLK<br>[5]    |                  | ,             |                  |                  | 1.7              | [4]          | [4]          |                  |                   | ()                |                   | ()                |                  |                  | PCH                | TATM_D<br>ATA [12] | TATM_D<br>ATA [10] | PPH                | E   |

| F  | -              | TL_SYNC<br>[5]  | _                | RL_SYN<br>C [5]  |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | TATM_CL<br>K       | TATM_D<br>ATA [9]  | TATM_D<br>ATA [8]  | PCL                | F   |

| G  | RL_CLK<br>[5]  | RL_SIG          |                  | PPL              |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | PPL                | RPHY_A<br>DD [2]   | RPHY_A<br>DD [3]   | RPHY_A<br>DD [1]   | G   |

| н  | TL_CLK         |                 | [5]<br>RL_DATA   | TL_SIG           |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | TATM_D             | TATM_E<br>NB       | TATM_S<br>OC       | RPHY_A<br>DD [0]   | н   |

| J  | [4]<br>RL_CLK  | [4]<br>RL_SIG   |                  | [4]<br>RL_SYN    |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | ATA [7] TATM_CL AV | TATM_D             | TATM_D             | TATM_D             | J   |

| ĸ  | [4]<br>TL_CLK  |                 | [4]<br>RL_DATA   | C [4]            |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | TATM_D             | ATA [6]            | ATA [5]            | TATM_D             | ĸ   |

| L  | [3]<br>RL_CLK  | [3]<br>PCL      | [4]<br>TL_DATA   | [3]<br>PPH       |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | ATA [0]            | TATM_D             | ATA [2]<br>RATM_D  | ATA [1]            | L   |

| м  | [3]<br>RL_SIG  | PCH             | [3]<br>RL_SYN    | PPL              |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | PPL                | ATA [3]<br>RATM_D  | ATA [0]<br>RATM_E  | RATM_D             | - м |

| N  | [3]<br>TL_SYNC |                 | C [3]<br>TL_SIG  | RL_DATA          |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | RATM_D             | ATA [2]<br>RATM_D  | NB<br>RATM_D       | ATA [1]<br>RATM_D  | N.  |

| P  | [2]<br>RL_SIG  | [2]<br>RL_CLK   | [2]<br>RL_SYN    | [3]<br>TL_DATA   |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | ATA [3]<br>RATM_D  | ATA [6]            | ATA [5]            | ATA [4]            | P   |

| •  | [2]<br>TL_CLK  | [2]<br>PPH      | C [2]            | [2]<br>RL_DATA   |                  |               |                  |                  | GND              | GND          | GND          | GND              | GND               | GND               |                   |                   |                  |                  | ATA [7]            | DD [0]             | LAV<br>TPHY_A      | OC_<br>RATM_C      | -   |

| R  | [1]<br>RL_SIG  | RL CLK          | [1]<br>RL_DATA   | [2]              |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | TPHY_A             | AR<br>RATM_D       | DD [2]             | LK TPHY_A          | R   |

| т  | [1]<br>RL_SYN  | [1]<br>TL_CLK   | [1]              | [1]<br>TL_DATA   |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | DD [1]             | ATA [9]            | PCL<br>RATM_D      | DD [3]             | т   |

| U  | C[1]           | [0]             | PCH<br>TI DATA   | [1]              |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | PCH<br>RATM_D      | ATA [12]           | ATA [11]           | ATA [8]            | U   |

| V  | PCL<br>RESERV  | PPL             | [0]<br>RL_SYN    | [0]<br>CGC_LIN   |                  |               |                  |                  |                  |              |              |                  |                   |                   |                   |                   |                  |                  | ATA [10]           | ATA [15]<br>SCAN_M | PPH                | DD [4]             | V   |

| W  | ED_IN TL_SIG   | PPL<br>RL_SIG   | C [0]            | E [1]            | LID              | PCH           | PPH<br>TL_CLK_   | INTB<br>CGC_DO   | CSB              | A [0]        | A [3]        | D [0]            | D [3]             | A [7]             | PPH               | D [7]             | A [10]           | D [9]            | PQH                | ODEB               | A [19]             | ATA [13]           | W   |

| Y  | [0]            | [0]             | PPH              | TRSTB            | PQH              | PPL           | OE               | UT [1]           | PCL              | RDB          | A [1]        | PPL              | A [6]             | D [6]             | A [9]             | D [8]             | A [13]           | PPH              | D [15]             | A [12]             | A [18]             | ATA [14]           | Y   |

| AA | RL_CLK<br>[0]  | RSTB            | SRTS_ST<br>BH    | ADAP_ST<br>BH    | CGC_LIN<br>E [2] | CGC_SE<br>R_D | NCLK             | CGC_DO<br>UT [0] | ACKB             | WRB          | A [2]        | PCH              | A [5]             | D [5]             | A [8]             | PCL               | D [10]           | A [14]           | D [13]             | PPL                | PPL                | A [17]             | AA  |

| AB | RL_DATA<br>[0] | PQL             | RESERV<br>ED_OUT | CGC_LIN<br>E [3] | CGC_LIN<br>E [0] | PPH           | CGC_DO<br>UT [3] | PPL              | CGC_DO<br>UT [2] | ALE          | PPL          | D [1]            | A [4]             | D [4]             | PPL               | D [2]             | A [11]           | D [11]           | A [15]             | D [12]             | D [14]             | A [16]             | AB  |

|    | 22             | 21              | 20               | 19               | 18               | 17            | 16               | 15               | 14               | 13           | 12           | 11               | 10                | 9                 | 8                 | 7                 | 6                | 5                | 4                  | 3                  | 2                  | 1                  |     |

RELEASED DATASHEET

PMC-2000097

PMC-Sierra

PM73123 AAL1GATOR-8

ISSUE 2 8 LINK CES/DBCES AAL1 SAR ISSUE 2

8 LINK CES/DBCES AAL1 SAR

## 8 PIN DESCRIPTION

UTOPIA Interface Signals (52)

| Pin Name Type Pin No. Function                                                                                                                                                                                                             |           |              |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                                                                                            | 71.       |              |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| <b>Note</b> signals have different meanings depending on whether the UTOPIA bus is in ATM master mode, PHY mode or Any-PHY mode. The mode is controlled by the UTOP_MODE and ANY-PHY_EN fields in the UI_SRC_CFG and UI_SNK_CFG registers. |           |              |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| All outputs are tri-state when the chip is in reset or when UI_EN is disabled in the UI_COMN_CFG register.                                                                                                                                 |           |              |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| All outputs have a maximum                                                                                                                                                                                                                 | output cu | rrent (IMAX) | = 8  mA.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| TATM_CLK/RPHY_CLK                                                                                                                                                                                                                          | Input     | F4           | <b>ATM</b> : Transmit UTOPIA ATM Layer Clock is the synchronization clock input for the TATM interface.                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                            |           |              | PHY: Receive UTOPIA/Any-PHY PHY Layer Clock is the synchronization clock input for the RPHY interface                                                                                                                                                             |  |  |  |  |  |  |

|                                                                                                                                                                                                                                            |           |              | Maximum frequency is 52 MHz.                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| TATM_SOC/RPHY_SOC<br>/RSOP                                                                                                                                                                                                                 | Output    | H2           | ATM: Transmit UTOPIA ATM Layer Start-Of-Cell is an active high signal asserted by the AAL1gator-8 when TATM_D contains the first valid byte of the cell.                                                                                                          |  |  |  |  |  |  |

|                                                                                                                                                                                                                                            |           |              | PHY: Receive Any-PHY/UTOPIA PHY Layer Start-Of-Cell is an active high signal asserted by the AAL1gator-8 when RPHY_D[15:0] contains the first valid word of the cell. AAL1gator-8 drives this signal only when the ATM layer has selected it for a cell transfer. |  |  |  |  |  |  |

|                                                                                                                                                                                                                                            |           |              | Any-PHY: This pin is the Receive Start of Packet (RSOP) signal which functions just like RPHY_SOC.                                                                                                                                                                |  |  |  |  |  |  |

ISSUE 2

| Pin Name                                                                                                                                                                                                                                                                                                                                    | Туре   | Pin No.                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TATM_D[15]/RPHY_D[15] TATM_D[14]/RPHY_D[14] TATM_D[13]/RPHY_D[13] TATM_D[12]/RPHY_D[12] TATM_D[11]/RPHY_D[11] TATM_D[10]/RPHY_D[10] TATM_D[9]/RPHY_D[9] TATM_D[8]/RPHY_D[8] TATM_D[8]/RPHY_D[6] TATM_D[6]/RPHY_D[6] TATM_D[5]/RPHY_D[5] TATM_D[5]/RPHY_D[4] TATM_D[3]/RPHY_D[3] TATM_D[2]/RPHY_D[2] TATM_D[1]/RPHY_D[1] TATM_D[0]/RPHY_D[0] | Output | C2<br>B1<br>D2<br>E3<br>D1<br>E2<br>F3<br>F2<br>H4<br>J3<br>J2<br>J1<br>L3<br>K2<br>K1<br>K4 | ATM: Transmit UTOPIA ATM Layer Data Bits 7 to 0 form the byte-wide data driven to the PHY layer. Bit 0 is the Least Significant Bit (LSB). Bit 7 is the Most Significant Bit (MSB) and is the first bit received for the cell from the serial line.  Note that only the lower 8 bit of the bus are used in ATM master mode.  PHY: Receive UTOPIA/Any-PHY PHY Layer Data Bits 15 to 0 form the word-wide data driven to the ATM layer. This bus is only driven when the ATM layer has selected the UI_SRC_INTF for a cell transfer. The upper byte is only used if 16_BIT_MODE is set in the UI_SRC_CFG register. Otherwise the upper byte is driven to 0's. Bit 0 is the LSB. Bit 7 is the MSB of the first byte and is the first bit received for the cell from the serial line. |

| TATM_PAR/ RPHY_PAR                                                                                                                                                                                                                                                                                                                          | Output | D3                                                                                           | <b>ATM</b> : Transmit UTOPIA ATM Layer Parity is a byte parity bit covering TATM_D(7:0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                             |        |                                                                                              | PHY: Receive UTOPIA/Any-PHY PHY Layer Parity is either a byte parity covering RPHY_D(7:0) or word parity covering RPHY_D(15:0) depending on the value of 16_BIT_MODE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Name                   | Туре | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TATM_ENB/RPHY_ENB<br>/RENB | Bidi | H3      | ATM: Transmit UTOPIA ATM Layer Enable is an active low signal asserted by the AAL1gator-8 during cycles when TATM_D contains valid data. It is not asserted until the AAL1gator-8 is ready to send a full cell.                                                                                                                                                                 |

|                            |      |         | PHY: Receive UTOPIA/Any-PHY PHY Layer Enable is an active low signal asserted by the ATM layer to indicate RPHY_D and RPHY_SOC will be sampled at the end of the next cycle. If UTOP_MODE in UI_SRC_CFG is set to UTOPIA Level 2 Mode then the AAL1gator-8 will drive data only if RPHY_ADD matches CFG_ADDR in the UI_SRC_ADD_CFG register the cycle before RPHY_ENB goes low. |

|                            |      |         | Any-PHY: This pin is the RENB input signal, which functions the same as RPHY_ENB. The only difference is that data is driven two cycles after selection instead of just one cycle.                                                                                                                                                                                              |

| Pin Name                    | Туре | Pin No. | Function                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TATM_CLAV/RPHY_CLAV<br>/RPA | Bidi | J4      | ATM: Transmit UTOPIA ATM Layer<br>Cell Available is an active high<br>signal from the PHY layer device to<br>indicate that there is sufficient room<br>to accept a cell.                                                                                                                                                                  |

|                             |      |         | PHY: Receive UTOPIA/Any-PHY PHY Layer Cell Available is an active high signal asserted by the AAL1gator-8 to indicate it is ready to deliver a complete cell. In Utopia Level 2 mode, this signal is driven only when MPHY_ADD matches CFG_ADDR in the UI_SRC_ADD_CFG register in the previous cycle. A pulldown resistor is recommended. |

|                             |      |         | Any-PHY: This pin is the Receive Packet Available (RPA) signal which functions the same as RPHY_CLAV except for it is activated two cycles after a matching address instead of one.                                                                                                                                                       |

| Pin Name                                  | Туре                                    | Pin No.  | Function                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPHY_ADD[4]/RSX<br>RPHY_ADD[3]/RCSB       | I/O<br>Input<br>Input<br>Input<br>Input | C1<br>G2 | ATM: These signals are not used in ATM mode.                                                                                                                                                                                                                                                                 |

| RPHY_ADD[2]<br>RPHY_ADD[1]<br>RPHY_ADD[0] |                                         | nput G1  | PHY: Receive UTOPIA PHY Layer Address (Bits 4 to 0) which selects the UTOPIA receiver. These inputs are used as an output enable for RPHY_CLAV and to validate the activation of RPHY_ENB. There are internal pull-up resistors. These pins are compared with CFG_ADDR[5:0] in the UI_SRC_CFG_ADDR register. |

|                                           |                                         |          | ANY-PHY: Receive Start Transfer(RSX) is an active high output which indicates the start of an Any-PHY packet which identifies the location of the prepended address. ANY-PHY_EN in UI_SRC_CFG register needs to be set for this function.                                                                    |

|                                           |                                         |          | Receive Chip Select Bar (RCSB) is an active low input which is used to select the AAL1gator-8 when polling in Any-PHY mode. This input is used to decode any Any-PHY address bits greater than RPHY_ADD[2]. This input goes low one cycle after Any-PHY address is valid.                                    |

|                                           |                                         |          | ANY-PHY_EN and CS_MODE_EN in UI_SRC_CFG register needs to be set for this function. Otherwise this bit functions as RPHY_ADD[3].                                                                                                                                                                             |

|                                           |                                         |          | RPHY_ADD[2:0] is the bottom three bits of the Any-PHY address and is used to select the device when polling. These pins are compared with CFG_ADDR[2:0] in the UI_SRC_CFG_ADDR register.                                                                                                                     |

|                                           |                                         |          | Note these pins must be tied to ground when not used.                                                                                                                                                                                                                                                        |

| Pin Name                   | Туре  | Pin No. | Function                                                                                                                                                        |

|----------------------------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RATM_CLK/ TPHY_CLK         | Input | R1      | <b>ATM</b> : Receive UTOPIA ATM Layer Clock is the synchronization clock input for synchronizing the RATM interface.                                            |

|                            |       |         | PHY: Transmit UTOPIA/Any-PHY PHY Layer Clock is the synchronization clock input for synchronizing the TPHY interface.                                           |

|                            |       |         | Maximum frequency is 52 MHz.                                                                                                                                    |

| RATM_SOC/TPHY_SOC<br>/TSOP | Input | P1      | This signal has two definitions depending on whether the UTOPIA is in ATM mode or PHY mode.                                                                     |

|                            |       |         | ATM: Receive UTOPIA ATM Layer<br>Start-Of-Cell is an active high signal<br>asserted by the PHY layer when<br>RATM_D contains the first valid byte<br>of a cell. |

|                            |       |         | PHY: Transmit UTOPIA/Any-PHY PHY Layer Start-Of-Cell is an active high signal asserted by the ATM layer when TPHY_D contains the first valid byte of a cell.    |

|                            |       |         | Any-PHY: This pin is the Transmit Start of Packet (TSOP) signal which functions just like TPHY_SOC This signal is optional in this mode. If unused, tie low.    |

| Pin Name                                                                                                                                                                                                                                                                                                                                                        | Туре  | Pin No.                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|