ALTIVECPEM/D 2/2002 Rev. 2.0

# AltiVec<sup>™</sup> Technology Programming Environments Manual

For More Information On This Product, Go to: www.freescale.com

AltiVec is a trademark of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc.

The PowerPC name and the PowerPC logotype are trademarks of International Business Machines Corporation used by Motorola under license from International Business Machines Corporation.

This document contains information on a new product under development. Motorola reserves the right to change or discontinue this product without notice. Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and *(K)* are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Motorola Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or 1-303-675-2140/ JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi-Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488 ASIA/PACIFC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong; Tel.: 852-26629298

World Wide Web Address: http://sps.motorola.com/mfax INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center 1-800-521-6274; electronic mail address: crc@wmkmail.sps.mot.com. Document Comments: FAX (512) 933-2625, Attn: RISC Applications Engineering. World Wide Web Addresses: http://www.mot.com/PowerPC http://www.mot.com/netcomm

© Motorola Inc. 2001. All rights reserved.

| Overview                                                          | 1   |

|-------------------------------------------------------------------|-----|

| AltiVec Register Set                                              | 2   |

| Operand Conventions                                               | 3   |

| Addressing Modes and Instruction Set Summary                      | 4   |

| Cache, Exceptions, and Memory Management                          | 5   |

| AltiVec Instructions                                              | 6   |

| Appendix A: Instruction Set Mnemonics - Decimal                   | A   |

| Appendix B: Instruction Set Mnemonics - Binary                    | В   |

| Appendix C: Opcodes - Decimal                                     | С   |

| Appendix D: Opcodes - Binary                                      | D   |

| Appendix E: Forms                                                 | Е   |

| Appendix F: Legends                                               | F   |

| Appendix G: Revision History                                      | G   |

| Glossary of Terms and Abbreviations                               | GLO |

| Index                                                             | IND |

| For More Information On This Product,<br>Go to: www.freescale.com |     |

| 1   | Overview                                        |

|-----|-------------------------------------------------|

| 2   | AltiVec Register Set                            |

| 3   | Operand Conventions                             |

| 4   | Addressing Modes and Instruction Set Summary    |

| 5   | Cache, Exceptions, and Memory Management        |

| 6   | AltiVec Instructions                            |

| A   | Appendix A: Instruction Set Mnemonics - Decimal |

| В   | Appendix B: Instruction Set Mnemonics - Binary  |

| C C | Appendix C: Opcodes - Decimal                   |

| D   | Appendix D: Opcodes - Binary                    |

| E   | Appendix E: Forms                               |

| F   | Appendix F: Legends                             |

| G   | Appendix G: Revision History                    |

| GLO | Glossary of Terms and Abbreviations             |

| IND | Index                                           |

|     | For More Information On This Product,           |

re Information On This Product, Go to: www.freescale.com

## Contents

Title

#### Page Number

| Audience                   | xx    |

|----------------------------|-------|

| Organization               |       |

| Suggested Reading          |       |

| General Information        |       |

| Related Documentation      | xxii  |

| Conventions                | xxiii |

| Acronyms and Abbreviations | xxiv  |

| Terminology Conventions    | xxvii |

#### Chapter 1 Overview

| 1.2AltiVec Technology Overview1.2.1Levels of AltiVec ISA1.2.2Features Not Defined by AltiVec ISA1.3AltiVec Architectural Model1.3.1AltiVec Registers and Programming Model1.3.2Operand Conventions1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions | 1-5<br>1-6<br>1-6 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.2.2Features Not Defined by AltiVec ISA1.3AltiVec Architectural Model1.3.1AltiVec Registers and Programming Model1.3.2Operand Conventions1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions                                                         | 1-6<br>1-6        |

| 1.3AltiVec Architectural Model1.3.1AltiVec Registers and Programming Model1.3.2Operand Conventions1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions                                                                                                 | . 1-6             |

| 1.3.1AltiVec Registers and Programming Model1.3.2Operand Conventions1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions                                                                                                                               |                   |

| 1.3.2Operand Conventions.1.3.2.1Byte Ordering .1.3.2.2Floating-Point Conventions .                                                                                                                                                                      | 16                |

| 1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions                                                                                                                                                                                                   | . 1-0             |

| 1.3.2.1Byte Ordering1.3.2.2Floating-Point Conventions                                                                                                                                                                                                   | . 1-7             |

|                                                                                                                                                                                                                                                         | . 1-7             |

|                                                                                                                                                                                                                                                         | . 1-8             |

| 1.3.3     AltiVec Addressing Modes                                                                                                                                                                                                                      |                   |

| 1.3.4 AltiVec Instruction Set                                                                                                                                                                                                                           | 1-11              |

| 1.3.5     AltiVec Cache Model                                                                                                                                                                                                                           | 1-12              |

| 1.3.6     AltiVec Exception Model                                                                                                                                                                                                                       | 1-12              |

| 1.3.7 Memory Management Model                                                                                                                                                                                                                           | 1-12              |

#### Chapter 2 AltiVec Register Set

| 2.1   | Overview on the AltiVec and PowerPC Registers |  |

|-------|-----------------------------------------------|--|

| 2.2   | AltiVec Register Set Overview                 |  |

| 2.3   | Registers defined by AltiVec ISA              |  |

| 2.3.1 | AltiVec Vector Register File (VRF)            |  |

| 2.3.2 | Vector Status and Control Register (VSCR)     |  |

| 2.3.3 | Vector Save/Restore Register (VRSAVE)         |  |

|       | - · · · · ·                                   |  |

Paragraph

Number

#### For More Information On This Product, Go to: www.freescale.com

## Contents

| Paragraph<br>Number | Title                                                           | Page<br>Number |

|---------------------|-----------------------------------------------------------------|----------------|

| 2.4                 | Additions to PowerPC UISA Registers                             |                |

| 2.4.1               | PowerPC Condition Register                                      |                |

| 2.5                 | Additions to PowerPC OEA Registers                              |                |

| 2.5.1               | AltiVec Field added in the PowerPC Machine State Register (MSR) |                |

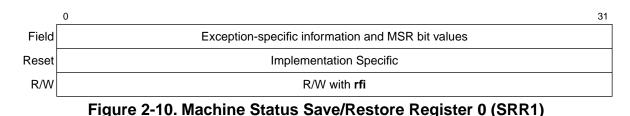

| 2.5.2               | Machine Status Save/Restore Registers (SRRs)                    |                |

| 2.5.2.1             | Machine Status Save/Restore Register 0 (SRR0)                   |                |

| 2.5.2.2             | Machine Status Save/Restore Register 1 (SRR1)                   |                |

#### Chapter 3 Operand Conventions

| 3.1     | Data Organization in Memory                            |  |

|---------|--------------------------------------------------------|--|

| 3.1.1   | Aligned and Misaligned Accesses                        |  |

| 3.1.2   | AltiVec Byte Ordering                                  |  |

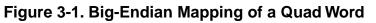

| 3.1.2.1 | Big-Endian Byte Ordering                               |  |

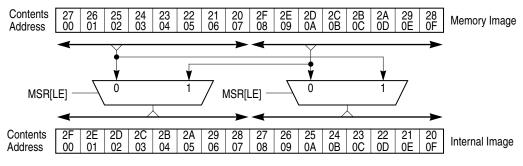

| 3.1.2.2 | Little-Endian Byte Ordering                            |  |

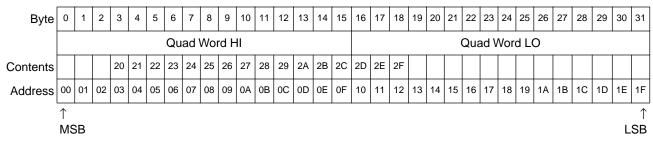

| 3.1.3   | Quad Word Byte Ordering Example                        |  |

| 3.1.4   | Aligned Scalars in Little-Endian Mode                  |  |

| 3.1.5   | Vector Register and Memory Access Alignment            |  |

| 3.1.6   | Quad-Word Data Alignment                               |  |

| 3.1.6.1 | Accessing a Misaligned Quad Word in Big-Endian Mode    |  |

| 3.1.6.2 | Accessing a Misaligned Quad Word in Little-Endian Mode |  |

| 3.1.6.3 | Scalar Loads and Stores                                |  |

| 3.1.6.4 | Misaligned Scalar Loads and Stores                     |  |

| 3.1.7   | Mixed-Endian Systems                                   |  |

| 3.2     | AltiVec Floating-Point Instructions—UISA               |  |

| 3.2.1   | Floating-Point Modes                                   |  |

| 3.2.1.1 | Java Mode                                              |  |

| 3.2.1.2 | Non-Java Mode                                          |  |

| 3.2.2   | Floating-Point Infinities                              |  |

| 3.2.3   | Floating-Point Rounding                                |  |

| 3.2.4   | Floating-Point Exceptions                              |  |

| 3.2.4.1 | NaN Operand Exception                                  |  |

| 3.2.4.2 | Invalid Operation Exception                            |  |

| 3.2.4.3 | Zero Divide Exception                                  |  |

| 3.2.4.4 | Log of Zero Exception                                  |  |

| 3.2.4.5 | Overflow Exception                                     |  |

| 3.2.4.6 | Underflow Exception                                    |  |

| 3.2.5   | Floating-Point NaNs                                    |  |

| 3.2.5.1 | NaN Precedence                                         |  |

| 3.2.5.2 | SNaN Arithmetic                                        |  |

| 3.2.5.3 | QNaN Arithmetic                                        |  |

MOTOROLA

## Contents

# Paragraph<br/>NumberPage<br/>Number3.2.5.4NaN Conversion to Integer

| 3.2.5.4 | NaN Conversion to Integer | 8 |

|---------|---------------------------|---|

| 3.2.5.5 | NaN Production            | 8 |

#### Chapter 4 Addressing Modes and Instruction Set Summary

| 4.1       | Conventions                                         |

|-----------|-----------------------------------------------------|

| 4.1.1     | Execution Model                                     |

| 4.1.2     | Computation Modes                                   |

| 4.1.3     | Classes of Instructions                             |

| 4.1.4     | Memory Addressing                                   |

| 4.1.4.1   | Memory Operands                                     |

| 4.1.4.2   | Effective Address Calculation                       |

| 4.2       | AltiVec UISA Instructions                           |

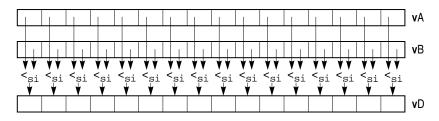

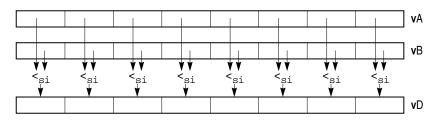

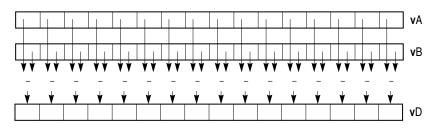

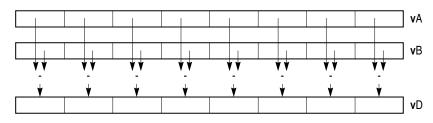

| 4.2.1     | Vector Integer Instructions                         |

| 4.2.1.1   | Saturation Detection                                |

| 4.2.1.2   | Vector Integer Arithmetic Instructions              |

| 4.2.1.3   | Vector Integer Compare Instructions                 |

| 4.2.1.4   | Vector Integer Logical Instructions                 |

| 4.2.1.5   | Vector Integer Rotate and Shift Instructions        |

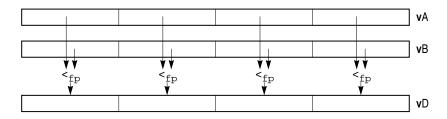

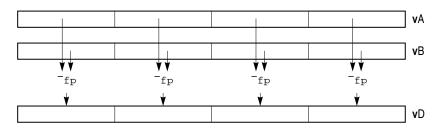

| 4.2.2     | Vector Floating-Point Instructions                  |

| 4.2.2.1   | Floating-Point Division and Square-Root             |

| 4.2.2.1.1 | Floating-Point Division                             |

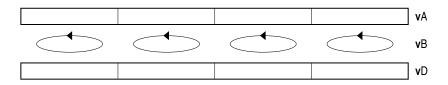

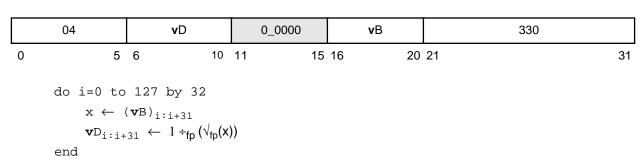

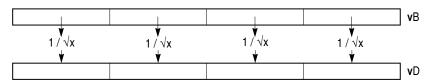

| 4.2.2.1.2 | Floating-Point Square-Root                          |

| 4.2.2.2   | Floating-Point Arithmetic Instructions              |

| 4.2.2.3   | Floating-Point Multiply-Add Instructions            |

| 4.2.2.4   | Floating-Point Rounding and Conversion Instructions |

| 4.2.2.5   | Floating-Point Compare Instructions                 |

| 4.2.2.6   | Floating-Point Estimate Instructions                |

| 4.2.3     | Load and Store Instructions                         |

| 4.2.3.1   | Alignment                                           |

| 4.2.3.2   | Load and Store Address Generation                   |

| 4.2.3.3   | Vector Load Instructions                            |

| 4.2.3.4   | Vector Store Instructions                           |

| 4.2.4     | Control Flow                                        |

| 4.2.5     | Vector Permutation and Formatting Instructions      |

| 4.2.5.1   | Vector Pack Instructions                            |

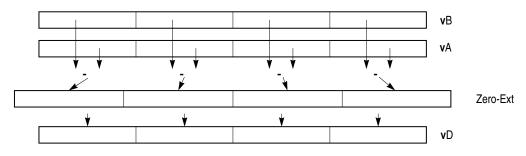

| 4.2.5.2   | Vector Unpack Instructions                          |

| 4.2.5.3   | Vector Merge Instructions                           |

| 4.2.5.4   | Vector Splat Instructions                           |

| 4.2.5.5   | Vector Permute Instruction                          |

| 4.2.5.6   | Vector Select Instruction                           |

#### Contents

| 4.2.5.7   | Vector Shift Instructions                        |  |

|-----------|--------------------------------------------------|--|

| 4.2.5.7.1 | Immediate Interelement Shifts/Rotates            |  |

| 4.2.5.7.2 | Computed Interelement Shifts/Rotates             |  |

| 4.2.5.7.3 | Variable Interelement Shifts                     |  |

| 4.2.6     | Processor Control Instructions—UISA              |  |

| 4.2.6.1   | AltiVec Status and Control Register Instructions |  |

| 4.2.7     | Recommended Simplified Mnemonics                 |  |

| 4.3       | AltiVec VEA Instructions                         |  |

| 4.3.1     | Memory Control Instructions—VEA                  |  |

| 4.3.2     | User-Level Cache Instructions—VEA                |  |

|           |                                                  |  |

#### Chapter 5 Cache, Exceptions, and Memory Management

| 5.1     | PowerPC Shared Memory                   |  |

|---------|-----------------------------------------|--|

| 5.2     | AltiVec Memory Bandwidth Management     |  |

| 5.2.1   | Software-Directed Prefetch              |  |

| 5.2.1.1 | Data Stream Touch (dst)                 |  |

| 5.2.1.2 | Transient Streams                       |  |

| 5.2.1.3 | Storing to Streams (dstst)              |  |

| 5.2.1.4 | Stopping Streams                        |  |

| 5.2.1.5 | Exception Behavior of Prefetch Streams  |  |

| 5.2.1.6 | Synchronization Behavior of Streams     |  |

| 5.2.1.7 | Address Translation for Streams         |  |

| 5.2.1.8 | Stream Usage Notes                      |  |

| 5.2.1.9 | Stream Implementation Assumptions       |  |

| 5.2.2   | Prioritizing Cache Block Replacement    |  |

| 5.2.3   | Partially Executed AltiVec Instructions |  |

| 5.3     | DSI Exception—Data Address Breakpoint   |  |

| 5.4     | AltiVec Unavailable Exception (0x00F20) |  |

|         |                                         |  |

#### Chapter 6 AltiVec Instructions

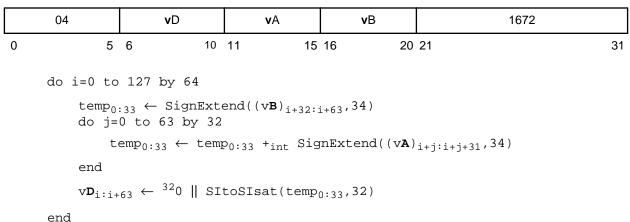

| 6.1   | Instruction Formats      | 6-1 |

|-------|--------------------------|-----|

| 6.1.1 | Instruction Fields       | 6-1 |

| 6.1.2 | Notation and Conventions |     |

| 6.2   | AltiVec Instruction Set  |     |

|       |                          |     |

**AltiVec Programming Environments Manual**

#### Contents

| Paragraph<br>Number | Title                                                          | Page<br>Number |

|---------------------|----------------------------------------------------------------|----------------|

|                     | Appendix A<br>AltiVec Instruction Set Listings                 |                |

| A.1                 | Instructions Sorted by Mnemonic in Decimal Format              | A-1            |

|                     | Appendix B<br>Instructions Sorted by Mnemonic in Binary Format |                |

| B.1                 | Instructions Sorted by Mnemonic in Binary Format               | B-1            |

|                     | Appendix C<br>Instructions Sorted by Opcode                    |                |

| C.1                 | Instructions Sorted by Opcode in Decimal Format                | C-1            |

|                     | Appendix D<br>Instructions Sorted by Opcode                    |                |

| D.1                 | Instructions Sorted by Opcode in Binary Format                 | D-1            |

|                     | Appendix E<br>Instructions Sorted by Form                      |                |

| E.1                 | Instructions Sorted by Form                                    | E-1            |

|                     | Appendix F<br>Instruction Set Legend                           |                |

| F.1                 | Instruction Set Legend                                         | F-1            |

|                     | Appendix G<br>User's Manual Revision History                   |                |

| G.1                 | Revision History                                               | G-1            |

|                     | Glossary                                                       |                |

|                     | Index                                                          |                |

## Contents

Paragraph Number

Title

Page Number

MOTOROLA

AltiVec Programming Environments Manual

## **Figures**

#### Page Number

| Number | Title                                                            | Number |

|--------|------------------------------------------------------------------|--------|

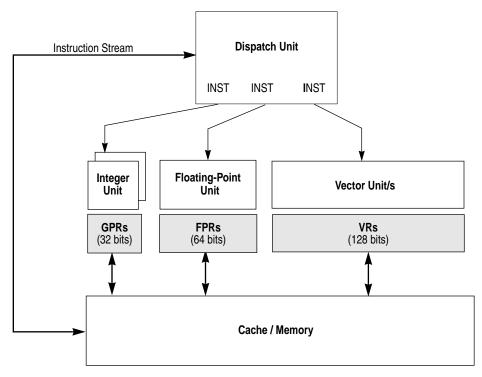

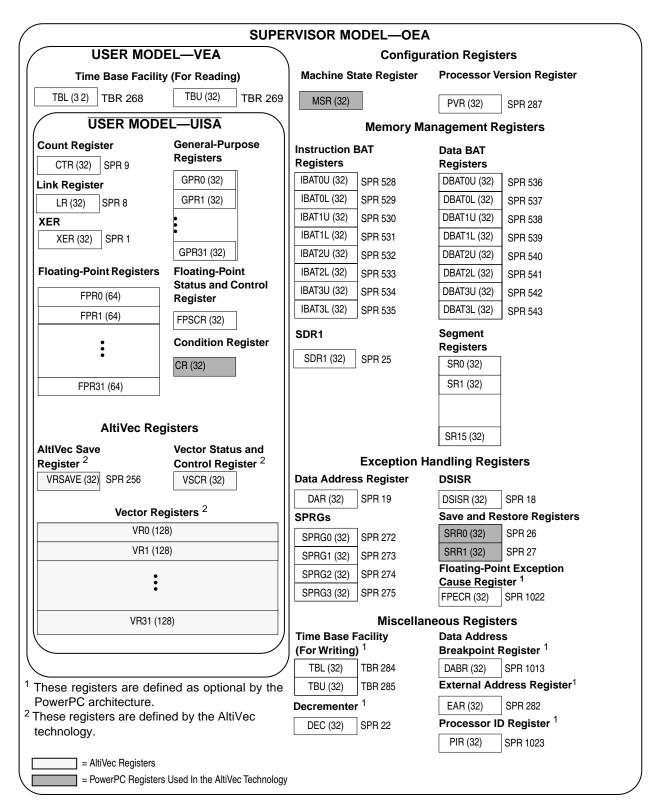

| 1-1    | Overview of PowerPC architecture with AltiVec Technology         |        |

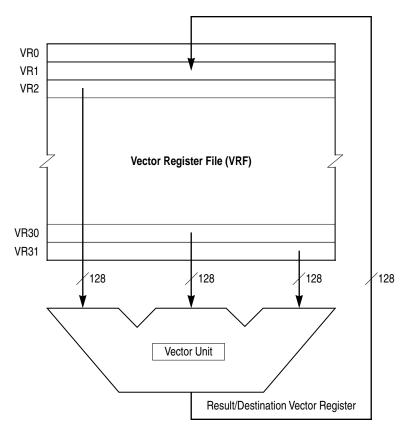

| 1-2    | AltiVec Top-Level Diagram                                        |        |

| 1-3    | Big-Endian Byte Ordering for a Vector Register                   |        |

| 1-4    | Bit Ordering                                                     |        |

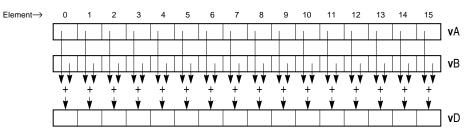

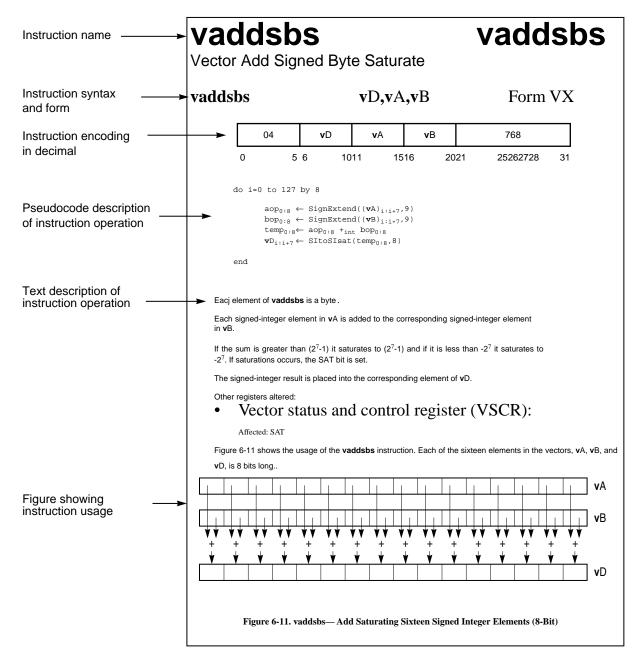

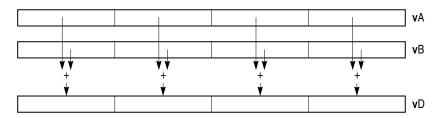

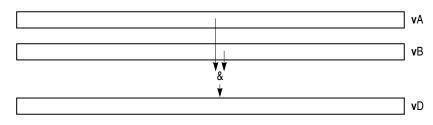

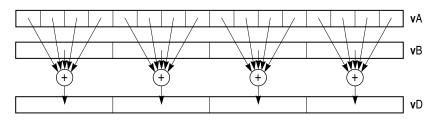

| 1-5    | Intraelement Example, vaddsbs                                    |        |

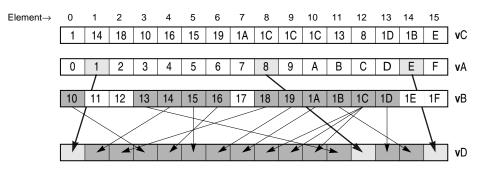

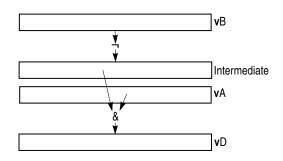

| 1-6    | Interelement Example, vperm                                      |        |

| 2-1    | Programming Model—All Registers                                  |        |

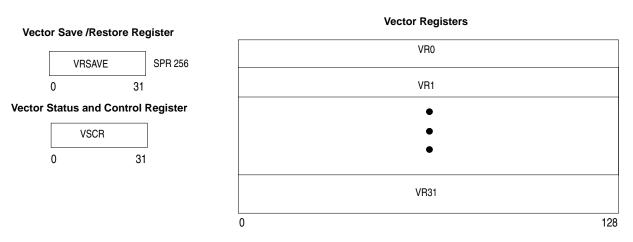

| 2-2    | AltiVec Register Set                                             |        |

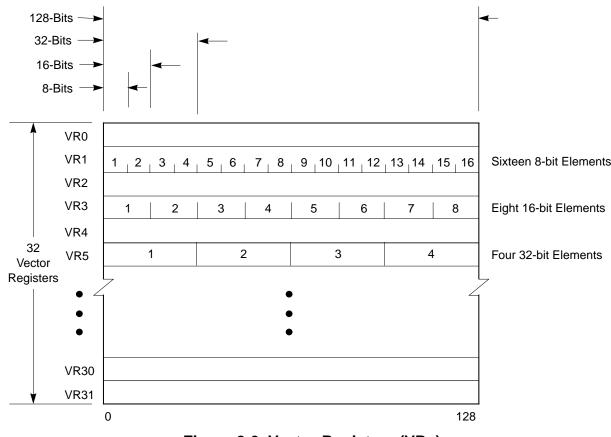

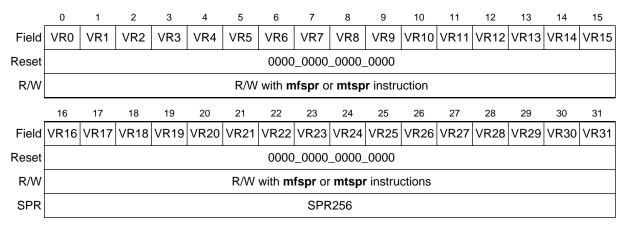

| 2-3    | Vector Registers (VRs)                                           |        |

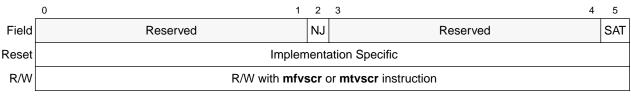

| 2-4    | Vector Status and Control Register (VSCR)                        |        |

| 2-5    | 32-bit VSCR Moved to a 128-bit Vector Register                   |        |

| 2-6    | Vector Save/Restore Register (VRSAVE)                            |        |

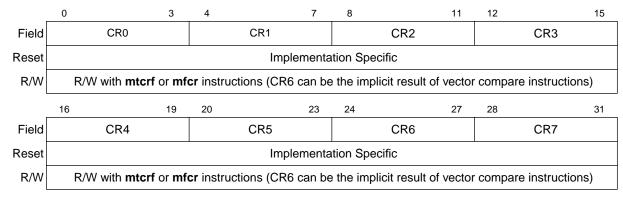

| 2-7    | Condition Register (CR)                                          |        |

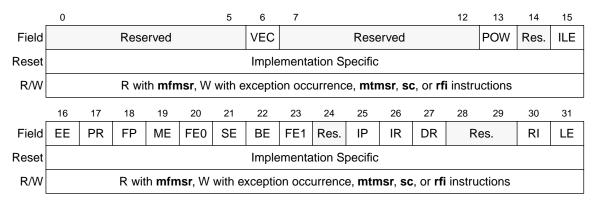

| 2-8    | Machine State Register (MSR)                                     |        |

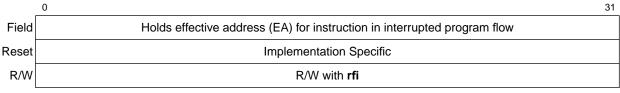

| 2-9    | Machine Status Save/Restore Register 0 (SRR0)                    |        |

| 2-10   | Machine Status Save/Restore Register 0 (SRR1)                    |        |

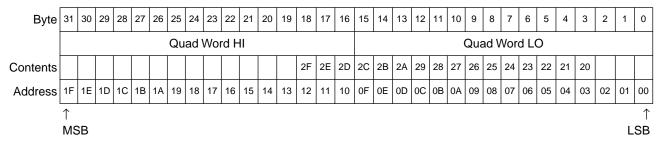

| 3-1    | Big-Endian Mapping of a Quad Word                                |        |

| 3-2    | Little-Endian Mapping of a Quad Word                             |        |

| 3-3    | Little-Endian Mapping of Quad Word—Alternate View                |        |

| 3-4    | Quad Word Load with PowerPC Munged Little-Endian Applied         |        |

| 3-5    | AltiVec Little Endian Double-Word Swap                           |        |

| 3-6    | Misaligned Vector in Big-Endian Mode                             |        |

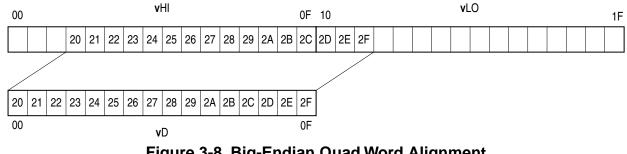

| 3-8    | Big-Endian Quad Word Alignment                                   |        |

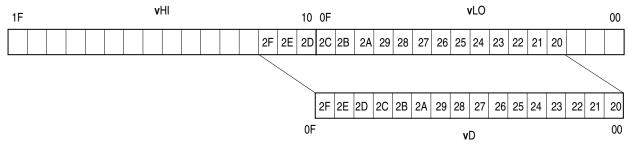

| 3-7    | Misaligned Vector in Little-Endian Addressing Mode               |        |

| 3-9    | Little-Endian Alignment                                          |        |

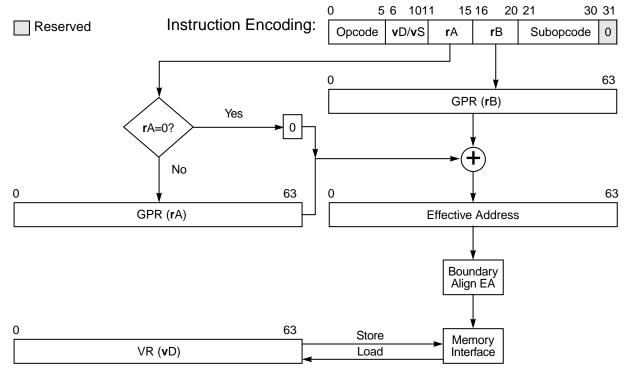

| 4-1    | Register Indirect with Index Addressing for Loads/Stores         |        |

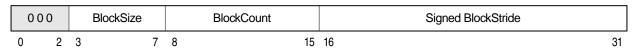

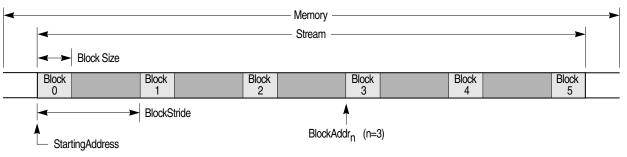

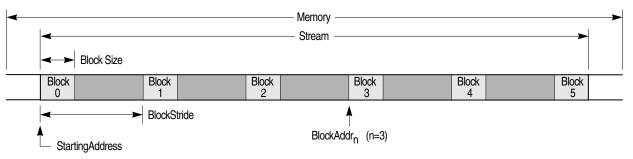

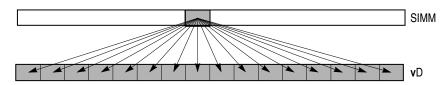

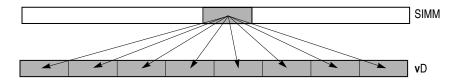

| 5-1    | Format of rB in dst Instruction                                  |        |

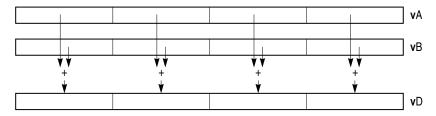

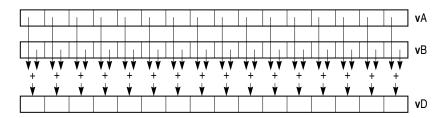

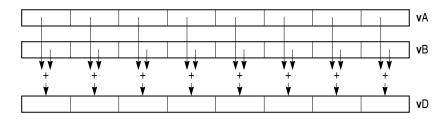

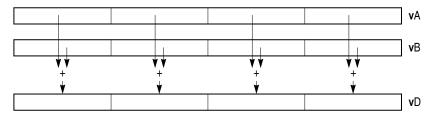

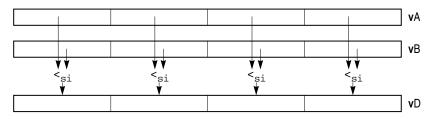

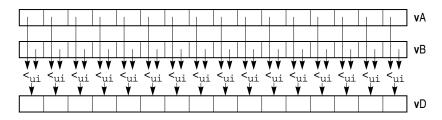

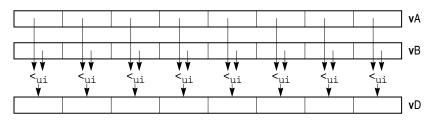

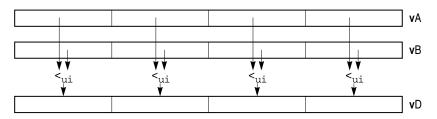

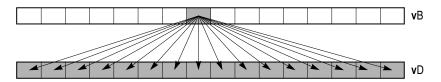

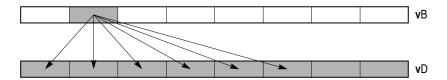

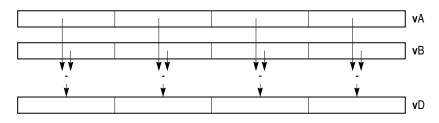

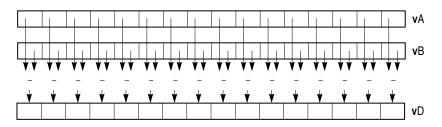

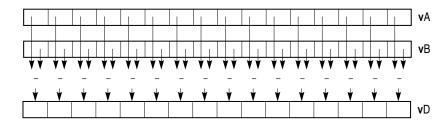

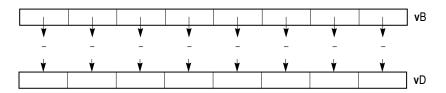

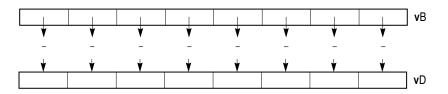

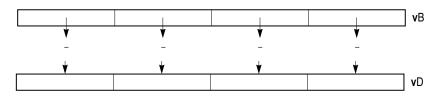

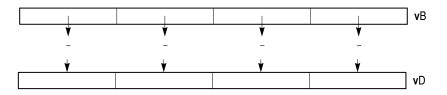

| 5-2    | Data Stream Touch                                                |        |

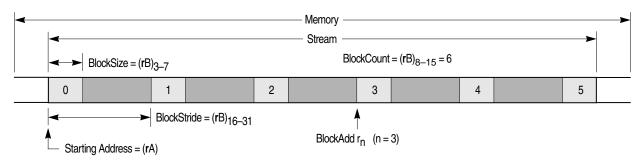

| 5-3    | SRR1 Bit Settings after an AltiVec Unavailable Exception         |        |

| 6-1    | Format of rB in dst instruction (32-bit)                         |        |

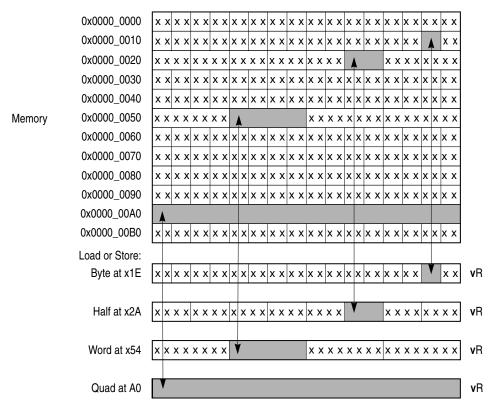

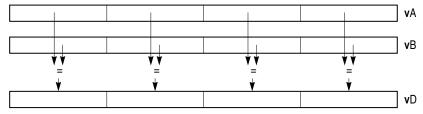

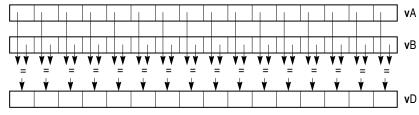

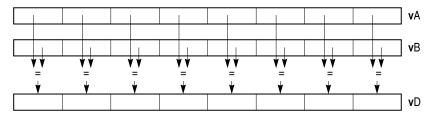

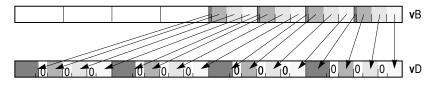

| 6-2    | Effects of Example Load/Store Instructions                       |        |

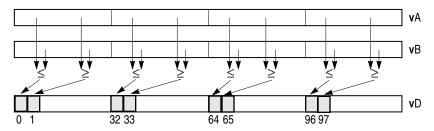

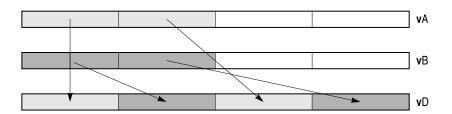

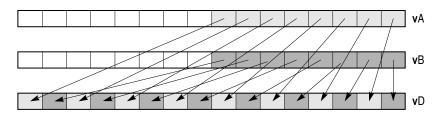

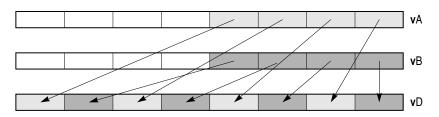

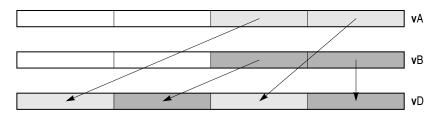

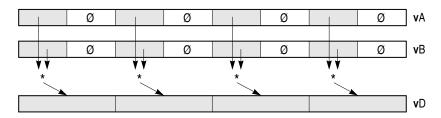

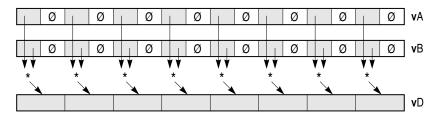

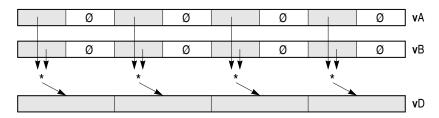

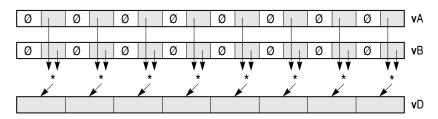

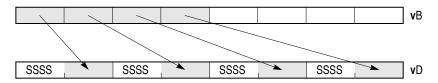

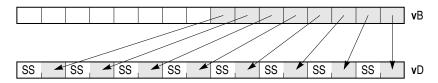

| 6-3    | Load Vector for Shift Left                                       |        |

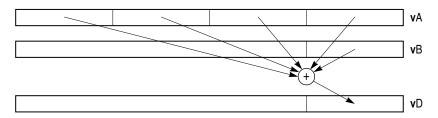

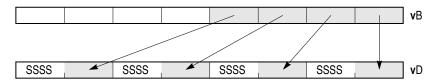

| 6-4    | Instruction vperm Used in Aligning Data                          |        |

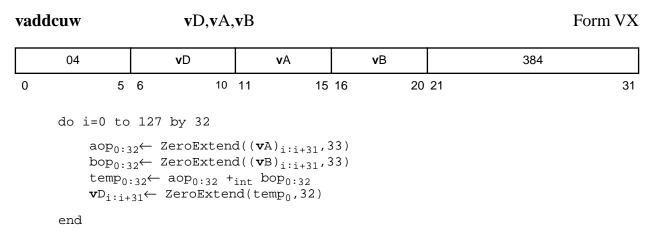

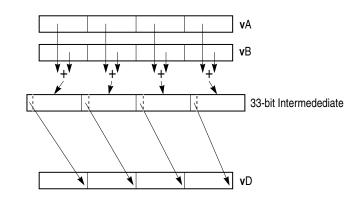

| 6-5    | vaddcuw—Determine Carries of Four Unsigned Integer Adds (32-Bit) |        |

| 6-6    | vaddfp—Add Four Floating-Point Elements (32-Bit)                 | 6-31   |

Figure

## **Figures**

| Figure<br>Number | Title                                                                                                       | Page<br>Number |

|------------------|-------------------------------------------------------------------------------------------------------------|----------------|

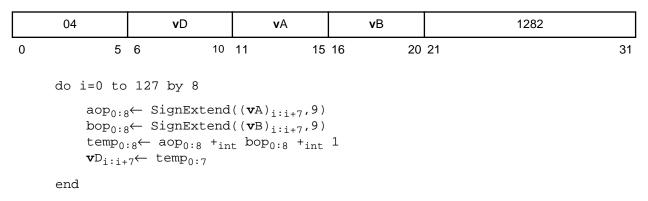

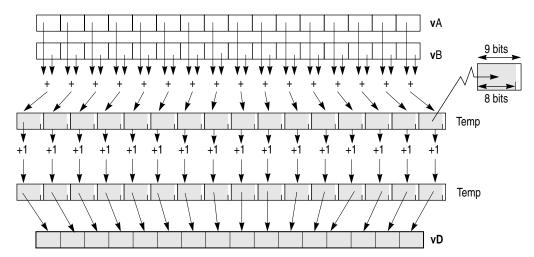

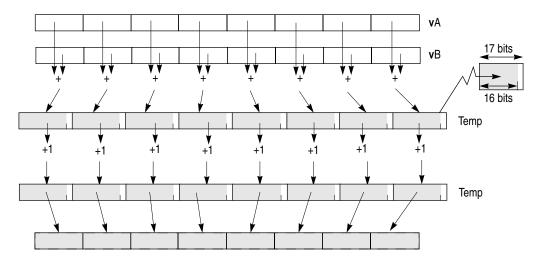

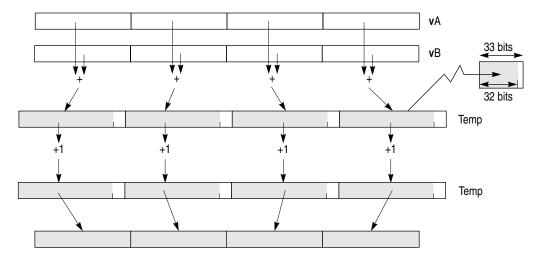

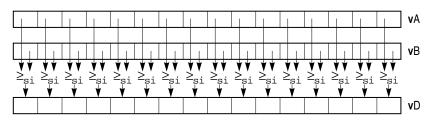

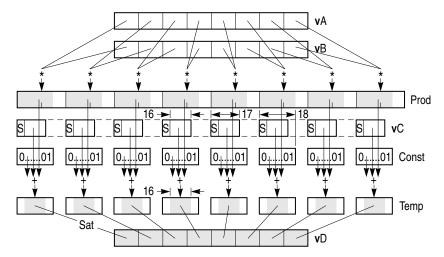

| 6-7              | vaddsbs—Add Saturating Sixteen Signed Integer Elements (8-Bit)                                              | 6-32           |

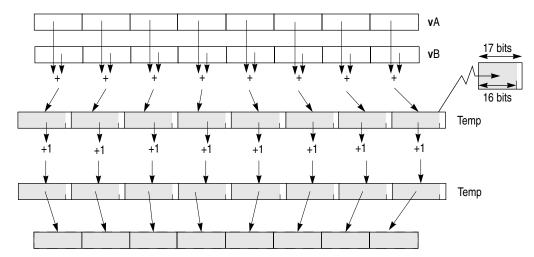

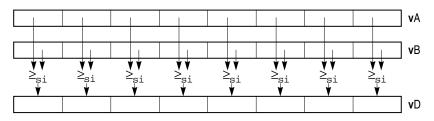

| 6-8              | vaddshs—Add Saturating Eight Signed Integer Elements (16-Bit)                                               | 6-33           |

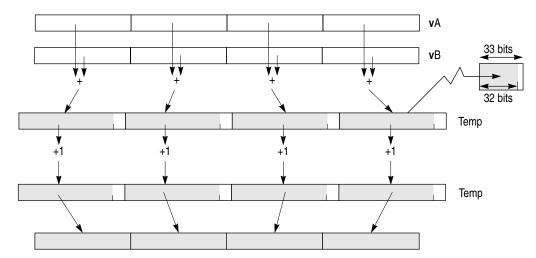

| 6-9              | vaddsws—Add Saturating Four Signed Integer Elements (32-Bit)                                                | 6-34           |

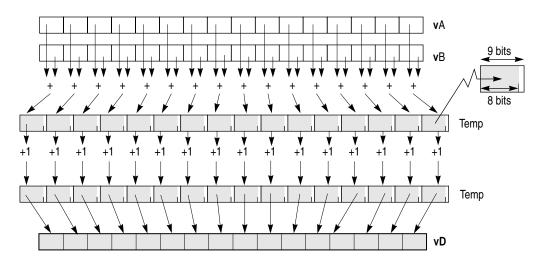

| 6-10             | vaddubm—Add Sixteen Integer Elements (8-Bit)                                                                | 6-35           |

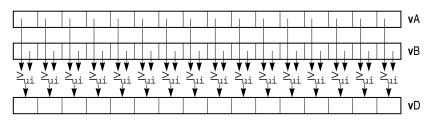

| 6-11             | vaddubs—Add Saturating Sixteen Unsigned Integer Elements (8-Bit)                                            | 6-36           |

| 6-12             | vadduhm—Add Eight Integer Elements (16-Bit)                                                                 | 6-37           |

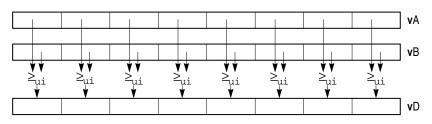

| 6-13             | vadduhs—Add Saturating Eight Unsigned Integer Elements (16-Bit)                                             | 6-38           |

| 6-14             | vadduwm—Add Four Integer Elements (32-Bit)                                                                  | 6-39           |

| 6-15             | vadduws-Add Saturating Four Unsigned Integer Elements (32-Bit)                                              | 6-40           |

| 6-16             | vand—Logical Bitwise AND                                                                                    | 6-41           |

| 6-17             | vand—Logical Bitwise AND with Complement                                                                    | 6-42           |

| 6-18             | vavgsb— Average Sixteen Signed Integer Elements (8-Bit)                                                     | 6-43           |

| 6-19             | vavgsh—Average Eight Signed Integer Elements (16-bits)                                                      | 6-44           |

| 6-20             | vavgsw— Average Four Signed Integer Elements (32-Bit)                                                       | 6-45           |

| 6-21             | vavgub—Average Sixteen Unsigned Integer Elements (8-bits)                                                   | 6-46           |

| 6-22             | vavgsh—Average Eight Signed Integer Elements (16-Bit)                                                       | 6-47           |

| 6-23             | vavguw—Average Four Unsigned Integer Elements (32-Bit)                                                      | 6-48           |

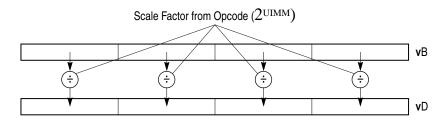

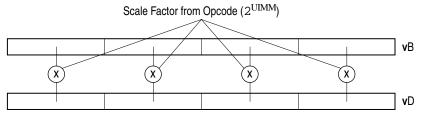

| 6-24             | vcfsx-Convert Four Signed Integer Elements to Four Floating-Point Element                                   | nts            |

|                  | (32-Bit)                                                                                                    | 6-49           |

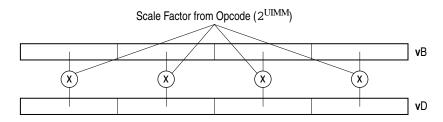

| 6-25             | vcfux-Convert Four Unsigned Integer Elements to Four Floating-Point Elements                                | nents          |

|                  | (32-Bit)                                                                                                    | 6-50           |

| 6-26             | vcmpbfp—Compare Bounds of Four Floating-Point Elements (32-Bit)                                             | 6-52           |

| 6-27             | vcmpeqfp—Compare Equal of Four Floating-Point Elements (32-Bit)                                             | 6-53           |

| 6-28             | vcmpequb—Compare Equal of Sixteen Integer Elements (8-bits)                                                 | 6-54           |

| 6-29             | vcmpequh—Compare Equal of Eight Integer Elements (16-Bit)                                                   | 6-55           |

| 6-30             | vcmpequw—Compare Equal of Four Integer Elements (32-Bit)                                                    | 6-56           |

| 6-31             | vcmpgefp—Compare Greater-Than-or-Equal of Four Floating-Point Elemen<br>(32-Bit)                            |                |

| 6-32             | vcmpgtfp—Compare Greater-Than of Four Floating-Point Elements (32-Bit)                                      |                |

| 6-33             | vcmpgtsb—Compare Greater-Than of Sixteen Signed Integer Elements (8-B                                       |                |

| 6-34             | vcmpgtsb—Compare Greater-Than of Eight Signed Integer Elements (16-Bi                                       | ,              |

| 6-35             | vcmpgtsw—Compare Greater-Than of Four Signed Integer Elements (32-Bit                                       |                |

| 6-36             | vcmpgtub—Compare Greater-Than of Sixteen Unsigned Integer Elements (82 Bill                                 |                |

| 6-37             | vcmpgtub—Compare Greater-Than of Eight Unsigned Integer Elements (16-                                       | ,              |

| 6-38             | vcmpgtuw—Compare Greater-Than of Four Unsigned Integer Elements (32-                                        |                |

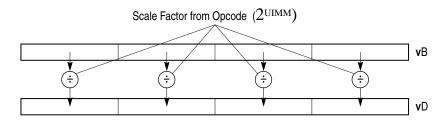

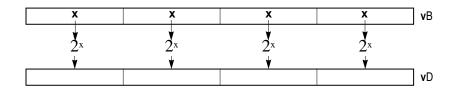

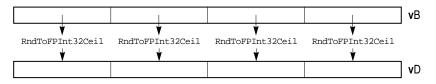

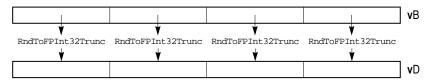

| 6-39             | vctsxs-Convert Four Floating-Point Elements to Four Signed Integer Eleme                                    | ents           |

| 6-40             | (32-Bit)                                                                                                    | ements         |

| 6-41             | (32-Bit)<br>vexptefp—2 Raised to the Exponent Estimate Floating-Point for Four Floatin<br>Elements (32-Bit) | ng-Point       |

|                  |                                                                                                             |                |

MOTOROLA

## **Figures**

| Figure<br>Number | Title                                                                            | Page<br>Number |

|------------------|----------------------------------------------------------------------------------|----------------|

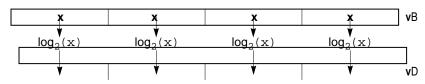

| 6-42             | vexptefp—Log2 Estimate Floating-Point for Four Floating-Point Elements           |                |

|                  | (32-Bit)                                                                         |                |

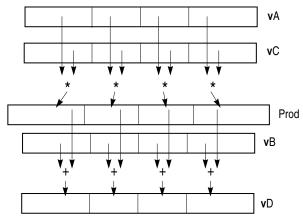

| 6-43             | vmaddfp—Multiply-Add Four Floating-Point Elements (32-Bit)                       |                |

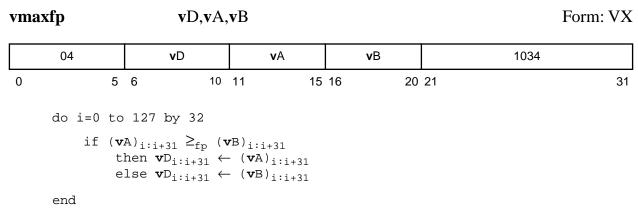

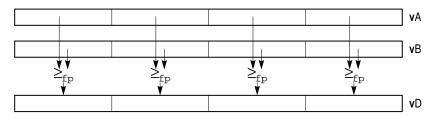

| 6-44             | vmaxfp—Maximum of Four Floating-Point Elements (32-Bit)                          |                |

| 6-45             | vmaxsb—Maximum of Sixteen Signed Integer Elements (8-Bit)                        |                |

| 6-46             | vmaxsh—Maximum of Eight Signed Integer Elements (16-Bit)                         |                |

| 6-47             | vmaxsw—Maximum of Four Signed Integer Elements (32-Bit)                          |                |

| 6-48             | vmaxub—Maximum of Sixteen Unsigned Integer Elements (8-Bit)                      |                |

| 6-49             | vmaxuh—Maximum of Eight Unsigned Integer Elements (16-Bit)                       |                |

| 6-50             | vmaxuw—Maximum of Four Unsigned Integer Elements (32-Bit)                        |                |

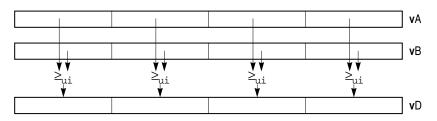

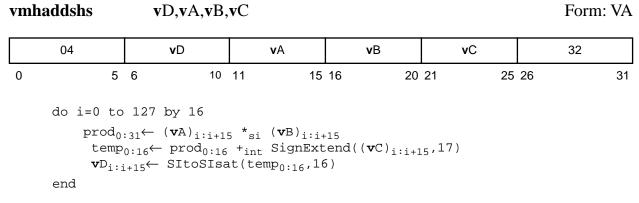

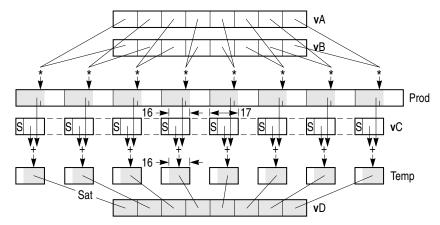

| 6-51             | vmhaddshs—Multiply-High and Add Eight Signed Integer Elements (16-Bit            | ·              |

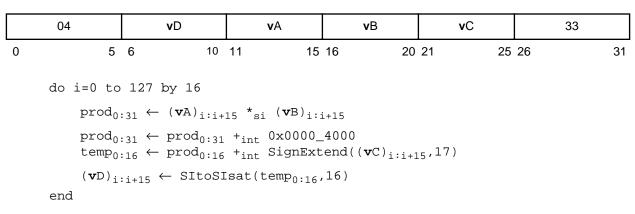

| 6-52             | vmhraddshs—Multiply-High Round and Add Eight Signed Integer Elements<br>(16-Bit) |                |

| 6-53             | vminfp—Minimum of Four Floating-Point Elements (32-Bit)                          |                |

| 6-54             | vminsb—Minimum of Sixteen Signed Integer Elements (8-Bit)                        |                |

| 6-55             | vminsb—Minimum of Eight Signed Integer Elements (16-Bit)                         |                |

| 6-56             | vminsm—Winimum of Eight Signed Integer Elements (10-Bit)                         |                |

| 6-57             | vminus—Minimum of Sixteen Unsigned Integer Elements (82-Bit)                     |                |

| 6-58             | vminub—Minimum of Eight Unsigned Integer Elements (0 Bit)                        |                |

| 6-59             | vminum—Minimum of Four Unsigned Integer Elements (32-Bit)                        |                |

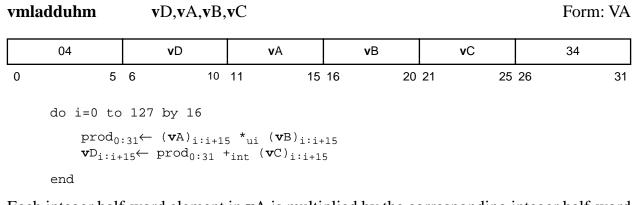

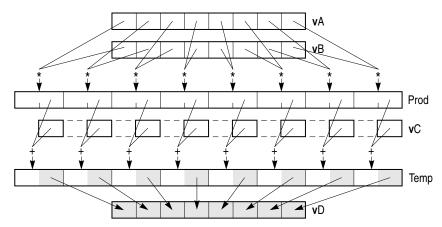

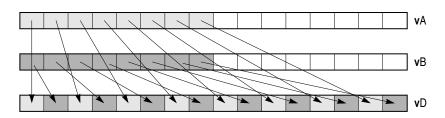

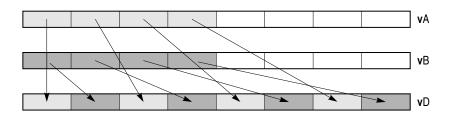

| 6-60             | vmladduhm—Multiply-Add of Eight Integer Elements (16-Bit)                        |                |

| 6-61             | vmrghb—Merge Eight High-Order Elements (8-Bit)                                   |                |

| 6-62             | vmrghh—Merge Four High-Order Elements (0 Bit)                                    |                |

| 6-63             | vmrghw—Merge Four High-Order Elements (32-Bit)                                   |                |

| 6-64             | vmrglb—Merge Eight Low-Order Elements (8-Bit)                                    |                |

| 6-65             | vmrglh—Merge Four Low-Order Elements (16-Bit)                                    |                |

| 6-66             | vmrglw—Merge Four Low-Order Elements (32-Bit)                                    |                |

| 6-67             | vmsummbm—Multiply-Sum of Integer Elements (8-Bit to 32-Bit)                      |                |

| 6-68             | vmsumshm—Multiply-Sum of Signed Integer Elements                                 |                |

|                  | (16-Bit to 32-Bit)                                                               | 6-96           |

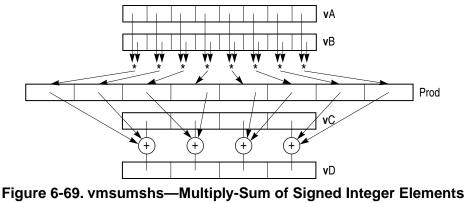

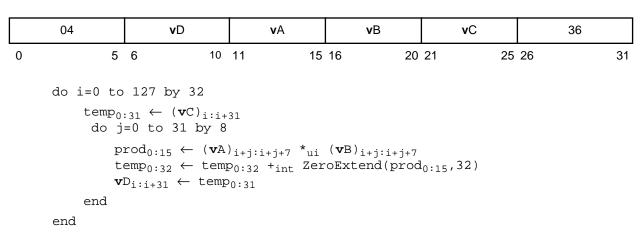

| 6-69             | vmsumshs—Multiply-Sum of Signed Integer Elements                                 |                |

|                  | (16-Bit to 32-Bit)                                                               | 6-97           |

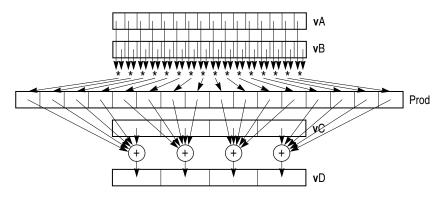

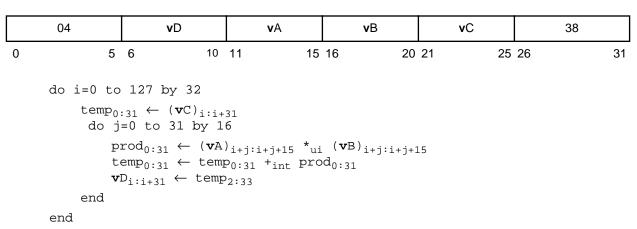

| 6-70             | vmsumubm—Multiply-Sum of Unsigned Integer Elements                               |                |

|                  | (8-Bit to 32-Bit)                                                                | 6-98           |

| 6-71             | vmsumuhm—Multiply-Sum of Unsigned Integer Elements                               |                |

|                  | (16-Bit to 32-Bit)                                                               | 6-99           |

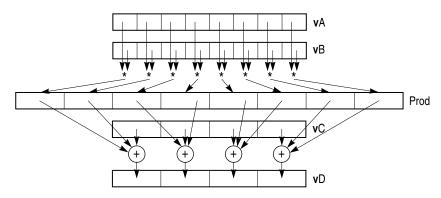

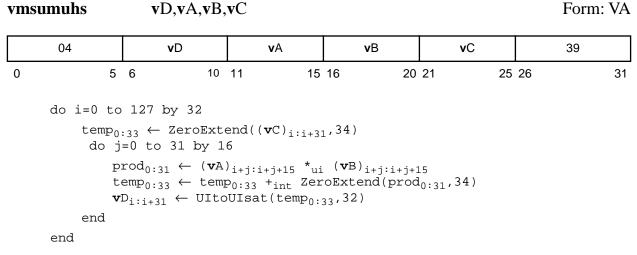

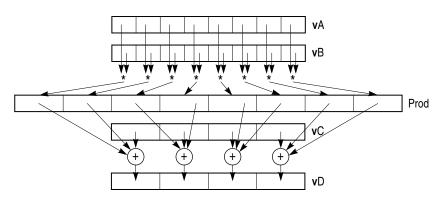

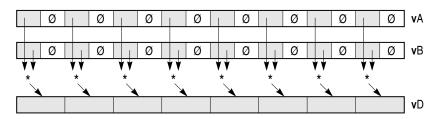

| 6-72             | vmsumuhs—Multiply-Sum of Unsigned Integer Elements                               |                |

|                  | (16-Bit to 32-Bit)                                                               | 6-100          |

| 6-73             | vmulesb—Even Multiply of Eight Signed Integer Elements (8-Bit)                   |                |

| 6-74             | vmulesb—Even Multiply of Four Signed Integer Elements (16-Bit)                   |                |

| 6-75             | vmuleub—Even Multiply of Eight Unsigned Integer Elements (8-Bit)                 |                |

|                  |                                                                                  |                |

## **Figures**

| Figure<br>Number | Page<br>Title Numbe                                                                |   |

|------------------|------------------------------------------------------------------------------------|---|

| 6-76             | vmuleuh—Even Multiply of Four Unsigned Integer Elements (16-Bit) 6-104             | 4 |

| 6-77             | vmulosb—Odd Multiply of Eight Signed Integer Elements (8-Bit)                      | 5 |

| 6-78             | vmuleuh—Odd Multiply of Four Unsigned Integer Elements (16-Bit) 6-100              | б |

| 6-79             | vmuloub—Odd Multiply of Eight Unsigned Integer Elements (8-Bit) 6-10               | 7 |

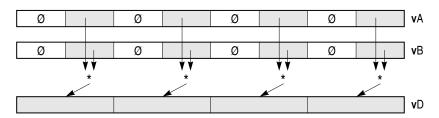

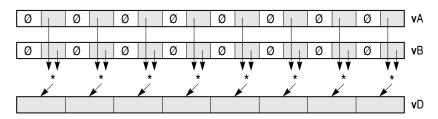

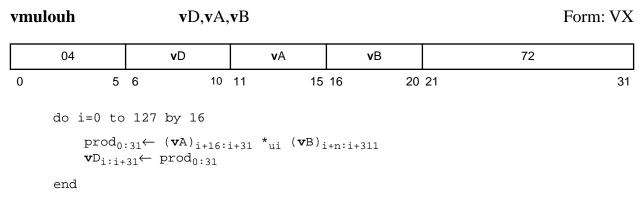

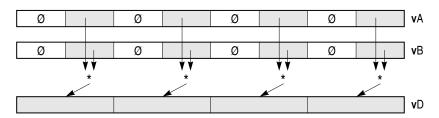

| 6-80             | vmulouh—Odd Multiply of Four Unsigned Integer Elements (16-Bit) 6-108              | 8 |

| 6-81             | vnmsubfp—Negative Multiply-Subtract of                                             |   |

|                  | Four Floating-Point Elements (32-Bit)                                              | 9 |

| 6-82             | vnor—Bitwise NOR of 128-bit Vector                                                 | 0 |

| 6-83             | vor—Bitwise OR of 128-bit Vector                                                   | 1 |

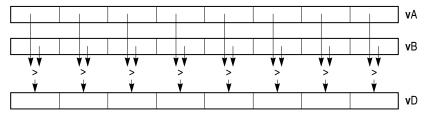

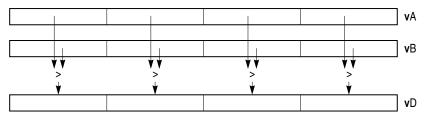

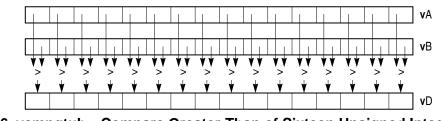

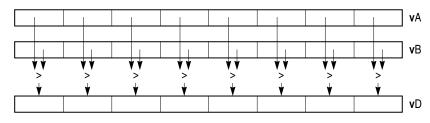

| 6-84             | vperm—Concatenate Sixteen Integer Elements (8-Bit)                                 | 2 |

| 6-85             | How a Word is Packed to a Half Word                                                | 3 |

| 6-86             | vpkpx—Pack Eight Elements (32-Bit) to Eight Elements (16-Bit)                      | 4 |

| 6-87             | vpkshss—Pack Sixteen Signed Integer Elements (16-Bit) to Sixteen Signed Integer    |   |

| 6-88             | Elements (8-Bit)                                                                   |   |

| 6-89             | Elements (8-Bit)                                                                   |   |

| 6-90             | Elements (16-Bit)                                                                  |   |

| 6-91             | vpkuhum—Pack Sixteen Unsigned Integer Elements (16-Bit)                            |   |

| 6-92             | to Sixteen Unsigned Integer Elements (8-Bit)                                       |   |

|                  | to Sixteen Unsigned Integer Elements (8-Bit)                                       | 0 |

| 6-93             | vpkuwum—Pack Eight Unsigned Integer Elements (32-Bit)                              |   |

|                  | to Eight Unsigned Integer Elements (16-Bit)                                        | 1 |

| 6-94             | vpkuwum—Pack Eight Unsigned Integer Elements (32-Bit)                              |   |

|                  | to Eight Unsigned Integer Elements (16-Bit)                                        |   |

| 6-95             | vrefp—Reciprocal Estimate of Four Floating-Point Elements (32-Bit) 6-124           | 4 |

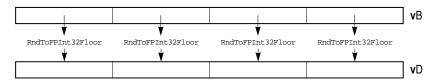

| 6-96             | vrfim— Round to Minus Infinity of Four Floating-Point<br>Integer Elements (32-Bit) | 5 |

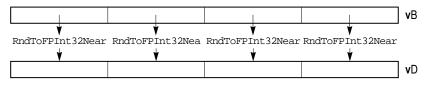

| 6-97             | vrfin—Nearest Round to Nearest of Four                                             |   |

| C 00             | Floating-Point Integer Elements (32-Bit)                                           | 5 |

| 6-98             | vrfip—Round to Plus Infinity of Four Floating-Point                                | - |

| <                | Integer Elements (32-Bit)                                                          |   |

| 6-99             | vrfiz—Round-to-Zero of Four Floating-Point Integer Elements (32-Bit)               |   |

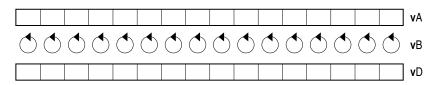

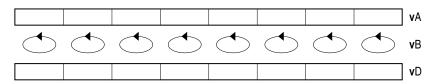

| 6-100            | vrlb—Left Rotate of Sixteen Integer Elements (8-Bit)                               |   |

| 6-101            | vrlh—Left Rotate of Eight Integer Elements (16-Bit)                                |   |

| 6-102            | vrlw—Left Rotate of Four Integer Elements (32-Bit)                                 | I |

| 6-103            | vrsqrtefp—Reciprocal Square Root Estimate of Four Floating-Point Elements          | า |

|                  | (32-Bit)                                                                           | 2 |

MOTOROLA

## **Figures**

| Figure<br>Number | Title                                                                 | Page<br>Number |

|------------------|-----------------------------------------------------------------------|----------------|

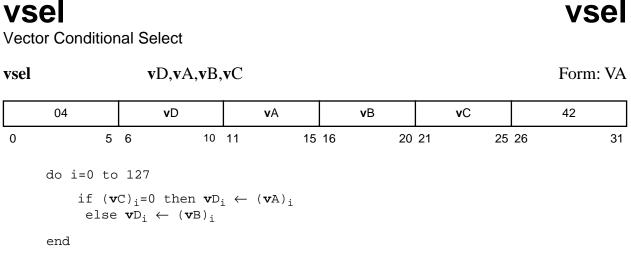

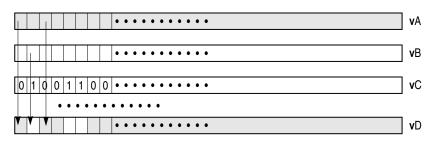

| 6-104            | vsel—Bitwise Conditional Select of Vector Contents(128-bit)           | 6-133          |

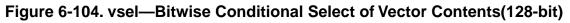

| 6-105            | vsl—Shift Bits Left in Vector (128-Bit)                               | 6-134          |

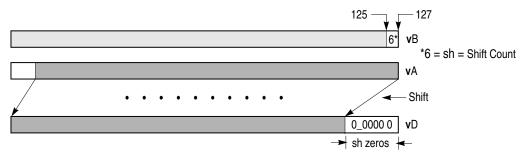

| 6-106            | vslb—Shift Bits Left in Sixteen Integer Elements (8-Bit)              | 6-135          |

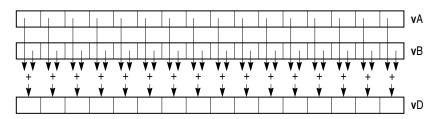

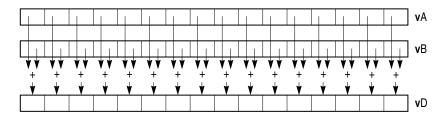

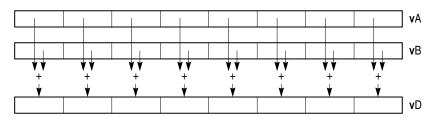

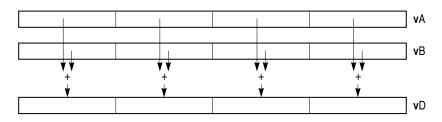

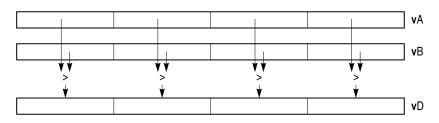

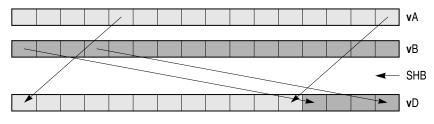

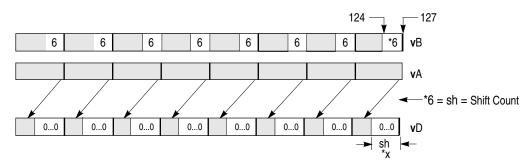

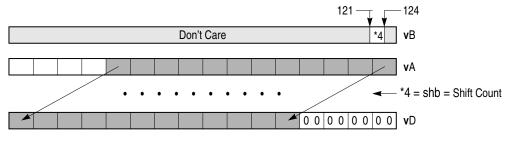

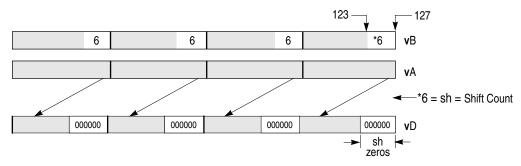

| 6-107            | vsldoi—Shift Left by Bytes Specified                                  |                |

| 6-108            | vslh—Shift Bits Left in Eight Integer Elements (16-Bit)               | 6-137          |

| 6-109            | vslo—Left Byte Shift of Vector (128-Bit)                              | 6-138          |

| 6-110            | vslw—Shift Bits Left in Four Integer Elements (32-Bit)                | 6-139          |

| 6-111            | vspltb—Copy Contents to Sixteen Elements (8-Bit)                      |                |

| 6-112            | vsplth—Copy Contents to Eight Elements (16-Bit)                       | 6-141          |

| 6-113            | vspltisb-Copy Value into Sixteen Signed Integer Elements (8-Bit)      | 6-142          |

| 6-114            | vspltish—Copy Value to Eight Signed Integer Elements (16-Bit)         |                |

| 6-115            | vspltisw—Copy Value to Four Signed Elements (32-Bit)                  | 6-144          |

| 6-116            | vspltw—Copy contents to Four Elements (32-Bit)                        | 6-145          |

| 6-117            | vsr—Shift Bits Right for Vectors (128-Bit)                            | 6-147          |

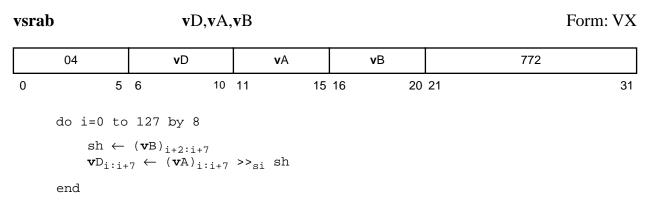

| 6-118            | vsrab—Shift Bits Right in Sixteen Integer Elements (8-Bit)            | 6-148          |

| 6-119            | vsrah—Shift Bits Right for Eight Integer Elements (16-Bit)            | 6-149          |

| 6-120            | vsraw—Shift Bits Right in Four Integer Elements (32-Bit)              |                |

| 6-121            | vsrb—Shift Bits Right in Sixteen Integer Elements (8-Bit)             | 6-151          |

| 6-122            | vsrh—Shift Bits Right for Eight Integer Elements (16-Bit)             | 6-152          |

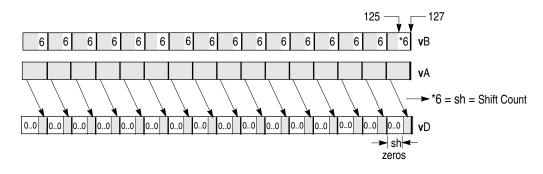

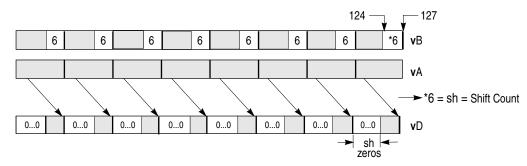

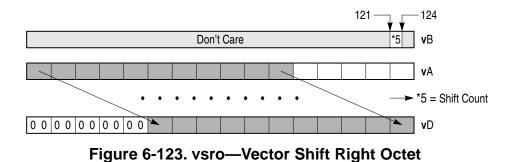

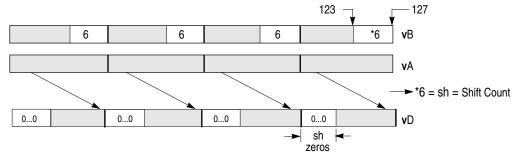

| 6-123            | vsro—Vector Shift Right Octet                                         |                |

| 6-124            | vsrw—Shift Bits Right in Four Integer Elements (32-Bit)               |                |

| 6-125            | vsubcuw—Subtract Carryout of Four Unsigned Integer Elements (32-Bit). |                |

| 6-126            | vsubfp—Subtract Four Floating Point Elements (32-Bit)                 |                |

| 6-127            | vsubsbs—Subtract Sixteen Signed Integer Elements (8-Bit)              |                |

| 6-128            | vsubshs—Subtract Eight Signed Integer Elements (16-Bit)               |                |

| 6-129            | vsubsws—Subtract Four Signed Integer Elements (32-Bit)                |                |

| 6-130            | vsububm—Subtract Sixteen Integer Elements (8-Bit)                     |                |

| 6-131            | vsububs—Subtract Sixteen Unsigned Integer Elements (8-Bit)            |                |

| 6-132            | vsubuhm—Subtract Eight Integer Elements (16-Bit)                      |                |

| 6-133            | vsubuhs—Subtract Eight Signed Integer Elements (16-Bit)               |                |

| 6-134            | vsubuwm—Subtract Four Integer Elements (32-Bit)                       |                |

| 6-135            | vsubuws—Subtract Four Signed Integer Elements (32-Bit)                |                |

| 6-136            | vsumsws—Sum Four Signed Integer Elements (32-Bit)                     |                |

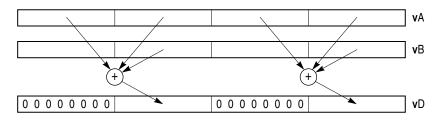

| 6-137            | vsum2sws—Two Sums in the Four Signed Integer Elements (32-Bit)        |                |

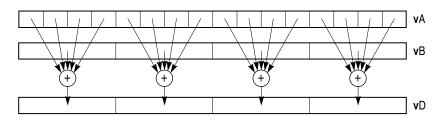

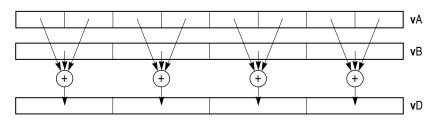

| 6-138            | vsum4sbs—Four Sums in the Integer Elements (32-Bit)                   |                |

| 6-139            | vsum4shs—Four Sums in the Integer Elements (32-Bit)                   |                |

| 6-140            | vsum4ubs—Four Sums in the Integer Elements (32-Bit)                   |                |

| 6-141            | vupkhpx—Unpack High-Order Elements (16 bit) to Elements (32-Bit)      |                |

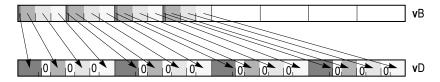

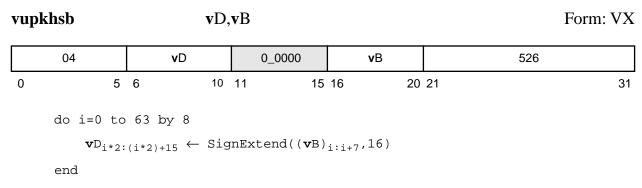

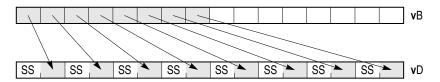

| 6-142            | vupkhsb—Unpack HIgh-Order Signed Integer Elements (8-Bit) to Signed   |                |

|                  | Elements (16-Bit)                                                     |                |

**Figures**

#### Figure Page Number Title Number 6-143 vupkhsh—Unpack Signed Integer Elements (16-Bit) to Signed Integer Elements 6-144 vupklsb—Unpack Low-Order Elements (8-Bit) to Elements (16-Bit) ...... 6-175 6-145 6-146 vupklsh—Unpack Low-Order Signed Integer Elements (16-Bit) to Signed Integer 6-147

MOTOROLA

**AltiVec Programming Environments Manual**

## **Tables**

#### Page ...

| Table<br>Number | Title                                                          | Page<br>Number |

|-----------------|----------------------------------------------------------------|----------------|

| i               | Acronyms and Abbreviated Terms                                 | xxiv           |

| ii              | Terminology Conventions                                        | xxvii          |

| iii             | Instruction Field Conventions                                  | xxvii          |

| 2-1             | VSCR Field Descriptions                                        |                |

| 2-2             | VRSAVE Bit Settings                                            |                |

| 2-3             | CR6 Field's Bit Settings for Vector Compare Instructions       |                |

| 2-4             | MSR Bit Settings                                               |                |

| 3-1             | Memory Operand Alignment                                       |                |

| 3-2             | Effective Address Modifications                                |                |

| 4-1             | Vector Integer Arithmetic Instructions                         |                |

| 4-2             | CR6 Field Bit Settings for Vector Integer Compare Instructions |                |

| 4-3             | Vector Integer Compare Instructions                            |                |

| 4-4             | Vector Integer Logical Instructions                            |                |

| 4-5             | Vector Integer Rotate Instructions                             |                |

| 4-6             | Vector Integer Shift Instructions                              |                |

| 4-7             | Floating-Point Arithmetic Instructions                         |                |

| 4-8             | Floating-Point Multiply-Add Instructions                       |                |

| 4-9             | Floating-Point Rounding and Conversion Instructions            |                |

| 4-10            | Common Mathematical Predicates                                 |                |

| 4-11            | Other Useful Predicates                                        |                |

| 4-12            | Floating-Point Compare Instructions                            |                |

| 4-13            | Floating-Point Estimate Instructions                           |                |

| 4-14            | Effective Address Alignment                                    |                |

| 4-15            | Integer Load Instructions                                      |                |

| 4-16            | Vector Load Instructions Supporting Alignment                  |                |

| 4-17            | Shift Values for lvsl Instruction                              |                |

| 4-18            | Shift Values for lvsr Instruction                              |                |

| 4-19            | Integer Store Instructions                                     |                |

| 4-20            | Vector Pack Instructions                                       |                |

| 4-21            | Vector Unpack Instructions                                     |                |

| 4-22            | Vector Merge Instructions                                      |                |

| 4-23            | Vector Splat Instructions                                      |                |

| 4-24            | Vector Permute Instruction                                     |                |

| 4-25            | Vector Select Instruction                                      |                |

| 4-26            | Vector Shift Instructions                                      |                |

## **Tables**

| Table<br>Number | Title                                                         | Page<br>Number |

|-----------------|---------------------------------------------------------------|----------------|

| 4-27            | Coding Various Shifts and Rotates with the vsidoi Instruction |                |

| 4-28            | Move to/from Condition Register Instructions                  |                |

| 4-29            | Simplified Mnemonics for Data Stream Touch (dst)              |                |

| 4-30            | User-Level Cache Instructions                                 |                |

| 5-1             | AltiVec Unavailable Exception—Register Settings               |                |

| 5-2             | Exception Priorities (Synchronous/Precise Exceptions)         |                |

| 6-1             | Instruction Syntax Conventions                                |                |

| 6-2             | Notation and Conventions                                      |                |

| 6-3             | Instruction Field Conventions                                 | 6-7            |

| 6-4             | Precedence Rules                                              | 6-7            |

| 6-5             | Special Values of the Element in vB                           | 6-67           |

| 6-6             | Special Values of the Element in vB                           | 6-69           |

| 6-7             | Special Values of the Element in vB                           |                |

| 6-8             | Special Values of the Element in vB                           |                |

| A-1             | Instruction Sorted by Mnemonic in Decimal Format              | A-1            |

| B-1             | Instructions Sorted by Mnemonic in Binary Format              | B-1            |

| C-1             | Instructions Sorted by Opcode in Decimal Format               | C-1            |

| D-1             | Instructions Sorted by Opcode in Binary Format                | D-1            |

| E-1             | VA-Form                                                       | E-1            |

| E-2             | VX-Form                                                       | E-2            |

| E-3             | X-Form                                                        | E-5            |

| E-4             | VXR-Form                                                      | E-6            |

| F-1             | AltiVec Instruction Set Legend                                | F-1            |

AltiVec Technology Programming Environments Manual

# **About This Book**

The primary objective of this manual is to help programmers provide software that is compatible with processors that implement the PowerPC architecture and the AltiVec<sup>TM</sup> technology. This book describes how the AltiVec technology relates to the 32-bit portions of the PowerPC architecture.

To locate any published errata or updates for this document, refer to the web at http://www.motorola.com/semiconductors.

This book is one of two that discuss the AltiVec technology. The two books are as follows.

- *AltiVec Technology Programming Interface Manual (AltiVec PIM)* is a reference guide for high-level programmers. The AltiVec PIM describes how programmers can access AltiVec functionality from programming languages such as C and C++. The AltiVec PIM defines a programming model for use with the AltiVec instruction set. Processor that implement the PowerPC architecture use the AltiVec instruction set as an extension of the PowerPC instruction set.

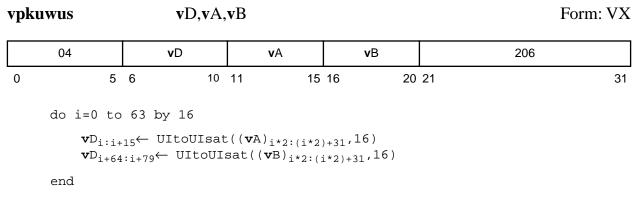

- AltiVec Technology Programming Environments Manual (AltiVec PEM) is used as a reference guide for assembler programmers. The AltiVec PEM uses a standardized format instruction to describe each instruction, showing syntax, instruction format, register translation language (RTL) code that describes how the instruction works, and a listing of which, if any, registers are affected. At the bottom of each instruction entry is a figure that shows the operations on elements within source operands and where the results of those operations are placed in the destination operand.

Because it is important to distinguish between the levels of the PowerPC architecture to ensure compatibility across multiple platforms, those distinctions are shown clearly throughout this book. This document stays consistent with the PowerPC architecture in referring to three levels, or programming environments, which are as follows:

- PowerPC user instruction set architecture (UISA)—The UISA defines the level of the architecture to which user-level software should conform. he UISA defines the base user-level instruction set, user-level registers, data types, memory conventions, and the memory and programming models seen by application programmers.

- PowerPC virtual environment architecture (VEA)—The VEA, which is the smallest component of the PowerPC architecture, defines additional user-level functionality that falls outside typical user-level software requirements. The VEA describes the memory model for an environment in which multiple processors or other devices can

Semiconductor, Inc

reescale

U

access external memory and defines aspects of the cache model and cache control instructions from a user-level perspective. VEA resources are particularly useful for optimizing memory accesses and for managing resources in an environment in which other processors and other devices can access external memory.

Implementations that conform to the VEA also conform to the UISA but may not necessarily adhere to the OEA.

• PowerPC operating environment architecture (OEA)—The OEA defines supervisor-level resources typically required by an operating system. It defines the memory management model, supervisor-level registers, and the exception model. Implementations that conform to the OEA also conform to the UISA and VEA.

Most of the discussions on the AltiVec technology are at the UISA level. The level of the architecture to which text refers is indicated in the outer margin, using the conventions shown in Section , "Conventions," on page -xxiii.

For ease in reference, this book and the processor user's manuals have arranged the architecture information into topics that build upon one another, beginning with a description and complete summary of registers and instructions (for all three environments) and progressing to more specialized topics such as the cache, exception, and memory management models. As such, chapters may include information from multiple levels of the architecture, but when discussing OEA and VEA, the level is noted in the text.

It is beyond the scope of this manual to describe individual AltiVec technology implementations on processors that implement the PowerPC architecture. It must be kept in mind that each processor that implements the PowerPC architecture and AltiVec technology is unique in its implementation.

The information in this book is subject to change without notice, as described in the disclaimers on the title page of this book. As with any technical documentation, it is the readers' responsibility to be sure they are using the most recent version of the documentation. For more information, contact your sales representative or visit our web site at http://www.mot.com/semiconductors.

## Audience

This manual is intended for system software and hardware developers and application programmers who want to develop products using the AltiVec technology extension to the PowerPC architecture. It is assumed that the reader understands operating systems, microprocessor system design, and the basic principles of RISC processing and details of the PowerPC architecture.

This book describes how the AltiVec technology interacts with the 32-bit portions of the PowerPC architecture

хх

0

## Organization

Following is a summary and a brief description of the major sections of this manual:

- Chapter 1, "Overview," is useful for those who want a general understanding of the features and functions of the AltiVec technology. This chapter provides an overview of how the AltiVec technology defines the register set, operand conventions, addressing modes, instruction set, cache model, and exception model.

- Chapter 2, "AltiVec Register Set," is useful for software engineers who need to understand the PowerPC programming model for the three programming environments. The chapter also discusses the functionality of the AltiVec technology registers and how they interact with the other PowerPC registers.

- Chapter 3, "Operand Conventions," describes how the AltiVec technology interacts with the PowerPC conventions for storing data in memory, including information regarding alignment, single-precision floating-point conventions, and big- and little-endian byte ordering.

- Chapter 4, "Addressing Modes and Instruction Set Summary," provides an overview of the AltiVec technology addressing modes and a brief description of the AltiVec technology instructions organized by function.

- Chapter 5, "Cache, Exceptions, and Memory Management," provides a discussion of the cache and memory model defined by the VEA and aspects of the cache model that are defined by the OEA. It also describes the exception model defined in the UISA.

- Chapter 6, "AltiVec Instructions," functions as a handbook for the AltiVec instruction set. Instructions are sorted by mnemonic. Each instruction description includes the instruction formats and figures where it helps in understanding what the instruction does.

- Appendices A, B, C, D, E, F, and G list all of the AltiVec instructions, grouped according to mnemonic, opcode, and form, in both decimal and binary order.

- Appendix G, "User's Manual Revision History," describes changes since the previous revision of this document.

- This manual also includes a glossary and an index.

## **Suggested Reading**

This section lists additional reading that provides background for the information in this manual as well as general information about the AltiVec technology and PowerPC architecture.

#### **General Information**

The following documentation, available through Morgan-Kaufmann Publishers, 340 Pine Street, Sixth Floor, San Francisco, CA, provides useful information about the PowerPC architecture and computer architecture in general:

• *The PowerPC Architecture: A Specification for a New Family of RISC Processors*, Second Edition, by International Business Machines, Inc.

For updates to the specification, see http://www.austin.ibm.com/tech/ppc-chg.html.

- *PowerPC Microprocessor Common Hardware Reference Platform: A System Architecture*, by Apple Computer, Inc., International Business Machines, Inc., and Motorola, Inc.

- *Computer Architecture: A Quantitative Approach*, Second Edition, by John L. Hennessy and David A. Patterson

- *Computer Organization and Design: The Hardware/Software Interface*, Second Edition, David A. Patterson and John L. Hennessy

#### **Related Documentation**

Motorola documentation is available from the sources listed on the back cover of this manual; the document order numbers are included in parentheses for ease in ordering:

- Programming Environments Manual for 32-Bit Implementations of the PowerPC Architecture (Programming Environments Manual)—Describes resources defined by the PowerPC architecture (documentation order number: MPCFP32B/AD).

- User's manuals—These books provide details about individual implementations and are intended for use with the *Programming Environments Manual*.

- Addenda/errata to user's manuals—Because some processors have follow-on parts an addendum is provided that describes the additional features and functionality changes. These addenda are intended for use with the corresponding user's manuals.

- Hardware specifications—Hardware specifications provide specific data regarding bus timing, signal behavior, and AC, DC, and thermal characteristics, as well as other design considerations.

- Technical summaries—Each device has a technical summary that provides an overview of its features. This document is roughly the equivalent to the overview (Chapter 1) of an implementation's user's manual.

- Application notes—These short documents address specific design issues useful to programmers and engineers working with Motorola processors.

Additional literature is published as new processors become available. For a current list of documentation, refer to http://www.motorola.com/semiconductors.

## Conventions

This document uses the following notational conventions:

| This document uses | ne ronoving notational conventions.                                                                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cleared/set        | When a bit takes the value zero, it is said to be cleared; when it takes a value of one, it is said to be set.                                                                                                                                                                                      |

| mnemonics          | Instruction mnemonics are shown in lowercase bold.                                                                                                                                                                                                                                                  |

| italics            | Italics indicate variable command parameters, for example, bcctrx.                                                                                                                                                                                                                                  |

|                    | Book titles in text are set in italics                                                                                                                                                                                                                                                              |

| 0x0                | Prefix to denote hexadecimal number                                                                                                                                                                                                                                                                 |

| 0b0                | Prefix to denote binary number                                                                                                                                                                                                                                                                      |

| rA, rB             | Instruction syntax used to identify a source general-purpose register (GPR)                                                                                                                                                                                                                         |

| rD                 | Instruction syntax used to identify a destination GPR                                                                                                                                                                                                                                               |

| frA, frB, frC      | Instruction syntax used to identify a source floating-point register (FPR)                                                                                                                                                                                                                          |

| frD                | Instruction syntax used to identify a destination FPR                                                                                                                                                                                                                                               |

| REG[FIELD]         | Abbreviations for registers are shown in uppercase text. Specific bits, fields, or ranges appear in brackets. For example, MSR[LE] refers to the little-endian mode enable bit in the machine state register.                                                                                       |

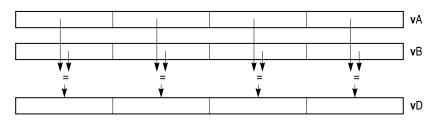

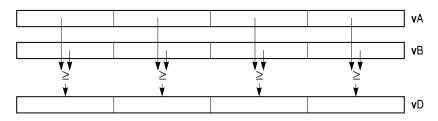

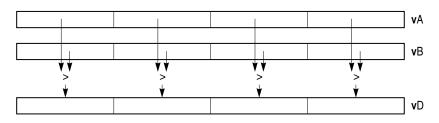

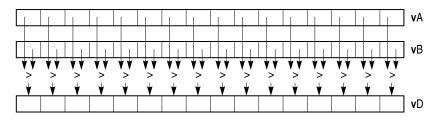

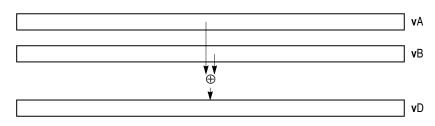

| vA, vB, vC         | Instruction syntax used to identify a source vector register (VR)                                                                                                                                                                                                                                   |

| vD                 | Instruction syntax used to identify a destination VR                                                                                                                                                                                                                                                |

| X                  | In some contexts, such as signal encodings, an unitalicized x indicates a don't care.                                                                                                                                                                                                               |

| x                  | An italicized x indicates an alphanumeric variable.                                                                                                                                                                                                                                                 |

| n                  | An italicized <i>n</i> indicates an numeric variable.                                                                                                                                                                                                                                               |

| -                  | NOT logical operator                                                                                                                                                                                                                                                                                |

| &                  | AND logical operator                                                                                                                                                                                                                                                                                |

|                    | OR logical operator                                                                                                                                                                                                                                                                                 |

|                    | This symbol identifies text that is relevant with respect to the<br>PowerPC user instruction set architecture (UISA). This symbol is<br>used both for information that can be found in the UISA specification<br>as well as for explanatory information related to that programming<br>environment. |

This symbol identifies text that is relevant with respect to the PowerPC virtual environment architecture (VEA). This symbol is used both for information that can be found in the VEA specification as well as for explanatory information related to that programming environment.

This symbol identifies text that is relevant with respect to the PowerPC operating environment architecture (OEA). This symbol is used both for information that can be found in the OEA specification as well as for explanatory information related to that programming environment.

Indicates functionality defined by the AltiVec technology.

G

V

0

Indicates reserved bits or bit fields in a register. Although these bits may be written to as ones or zeros, they are always read as zeros.

Additional conventions used with instruction encodings are described in Section 6.1, "Instruction Formats."

## **Acronyms and Abbreviations**

Table i contains acronyms and abbreviations that are used in this document. Note that the meanings for some acronyms (such as SDR1 and XER) are historical, and the words for which an acronym stands may not be intuitively obvious.

| Term        | Meaning                                                     |

|-------------|-------------------------------------------------------------|

| AltiVec PEM | AltiVec Technology Programming Environments Manual          |

| AltiVec PIM | AltiVec Technology Programming Interface Manual             |

| ALU         | Arithmetic logic unit                                       |

| BAT         | Block address translation                                   |

| CR          | Condition register                                          |

| CTR         | Count register                                              |

| DABR        | Data address breakpoint register                            |

| DAR         | Data address register                                       |

| DBAT        | Data BAT                                                    |

| DEC         | Decrementer register                                        |

| DSISR       | Register used for determining the source of a DSI exception |

| EA          | Effective address                                           |

| ECC         | Error checking and correction                               |

Table i. Acronyms and Abbreviated Terms

AltiVec Technology Programming Environments Manual

MOTOROLA

| Term          | Meaning                                                                                |

|---------------|----------------------------------------------------------------------------------------|

| FPR           | Floating-point register                                                                |

| FPSCR         | Floating-point status and control register                                             |

| FPU           | Floating-point unit                                                                    |

| GPR           | General-purpose register                                                               |

| IABR          | Instruction address breakpoint register                                                |

| IBAT          | Instruction BAT                                                                        |

| IEEE          | Institute of Electrical and Electronics Engineers                                      |

| ITLB          | Instruction translation lookaside buffer                                               |

| IU            | Integer unit                                                                           |

| L2            | Secondary cache                                                                        |

| L3            | Level 3 cache                                                                          |

| LIFO          | Last-in-first-out                                                                      |

| LR            | Link register                                                                          |

| LRU           | Least recently used                                                                    |

| LSB           | Least-significant byte                                                                 |

| lsb           | Least-significant bit                                                                  |

| LSU           | Load/store unit                                                                        |

| LSQ           | Least-significant quad-word                                                            |

| lsq           | Least-significant quad-word                                                            |

| MESI          | Modified/exclusive/shared/invalid—cache coherency protocol                             |

| MMCR <i>n</i> | Monitor mode control registers                                                         |

| MMU           | Memory management unit                                                                 |

| MSB           | Most-significant byte                                                                  |

| msb           | Most-significant bit                                                                   |

| MSQ           | Most-significant quad-word                                                             |

| msq           | Most-significant quad-word                                                             |

| MSR           | Machine state register                                                                 |

| NaN           | Not a number                                                                           |

| NIA           | Next instruction address                                                               |

| No-op         | No operation                                                                           |

| OEA           | Operating environment architecture                                                     |

| PEM           | Programming Environments Manual For 32-Bit Implementations of the PowerPC Architecture |

| PMC <i>n</i>  | Performance monitor counter registers                                                  |

| PTE           | Page table entry                                                                       |

| Term           | Meaning                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------|

| PTEG           | Page table entry group                                                                          |

| PVR            | Processor version register                                                                      |

| RISC           | Reduced instruction set computing                                                               |

| RTL            | Register transfer language                                                                      |

| RWITM          | Read with intent to modify                                                                      |

| RWNITM         | Read with no intent to modify                                                                   |

| SDA            | Sampled data address register                                                                   |

| SDR1           | Register that specifies the page table base address for virtual-to-physical address translation |

| SIA            | Sampled instruction address register                                                            |

| SIMM           | Signed immediate value                                                                          |

| SPR            | Special-purpose register                                                                        |

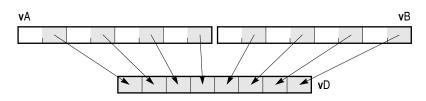

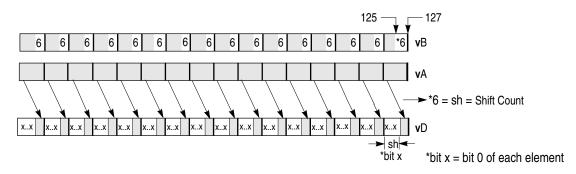

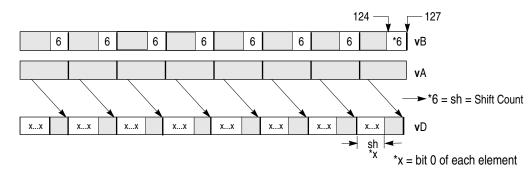

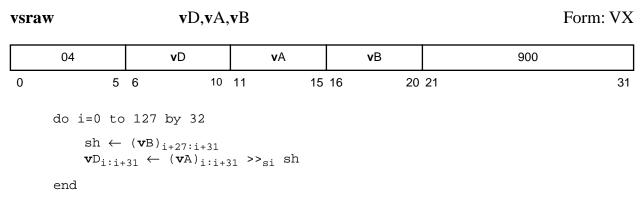

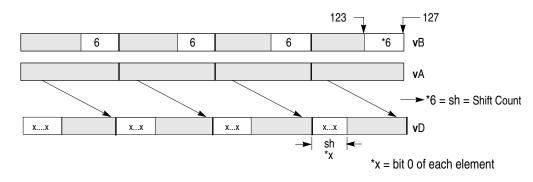

| SR <i>n</i>    | Segment register                                                                                |