# **Signetics**

# SAA5025 Teletext Timing Chain for USA 525-Line System

**Product Specification**

#### **Linear Products**

### DESCRIPTION

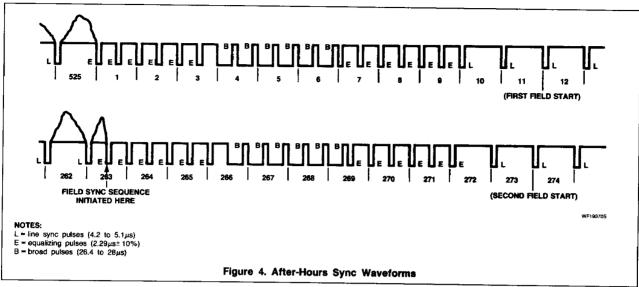

The SAA5025 is a MOS N-channel integrated circuit which performs the timing functions for a Teletext system. It provides the necessary timing signals to extract data from a memory and produce a display according to the USA 525-line television standard (system M).

The SAA5025 may be used in conjunction with the SAA5030 (Teletext video processor; VIP) the SAA5050 (Teletext character generator; TROM), the SAA5040B (Teletext acquisition control; TAC) and the SAA5045 (Gearing and Address Logic Array; GALA).

### **FEATURES**

- Designed to operate with USA 525-line television standard (system M)

- For 24 row (8 TV lines per row) × 40 character display

- Big character select input for double-height characters

- Composite sync signal output for display time-base synchronization

### **APPLICATIONS**

- Teletext

- Telecaptioning

- Videotex

- Phase-locking with Incoming video (when used with SAA5030)

- Composite sync generator

- Low cost display systems (when used with SAA5050 series)

### **ORDERING INFORMATION**

| DESCRIPTION                   | TEMPERATURE RANGE | ORDER CODE |

|-------------------------------|-------------------|------------|

| 28-Pin Plastic DIP (SOT-117D) | -20°C to +70°C    | SAA5025DN  |

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                                                 | RATING        | UNIT |

|------------------|---------------------------------------------------------------------------|---------------|------|

| V <sub>DD</sub>  | Supply voltage range                                                      | -0.3 to +7.5  | ٧    |

| Vi               | Input voltage range <sup>1</sup>                                          | -0.3 to +7.5  | ٧    |

| V <sub>OHZ</sub> | High-impedance state output voltage                                       | -0.3 to +7.5  | ٧    |

| V <sub>ODD</sub> | Open-drain output voltage                                                 | -0.3 to +13.2 | ٧    |

|                  | Electrostatic charge protection on all inputs and outputs <sup>2, 3</sup> | 1000          | ٧    |

| P <sub>TOT</sub> | Total power dissipation per package                                       | 275           | mW   |

| TA               | Operating ambient temperature range                                       | -20 to +70    | °C   |

| T <sub>STG</sub> | Storage temperature range                                                 | -65 to +150   | °C   |

### NOTES:

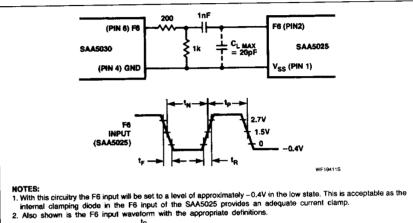

- 1. See also characteristics on F6 input and Figure 8.

- 2. Equivalent to discharging a 250pF capacitor through a  $1k\Omega$  series resistor.

- 3. N.B.: the SAA5025 is not protected against TV tube flash-over.

- 4. All outputs are TTL compatible.

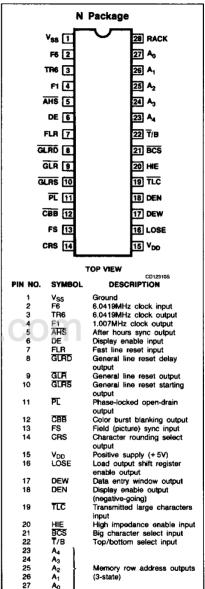

### PIN CONFIGURATION

January 14, 1987 13-14 853-1143 87202

....

Read address clock output

**SAA5025**

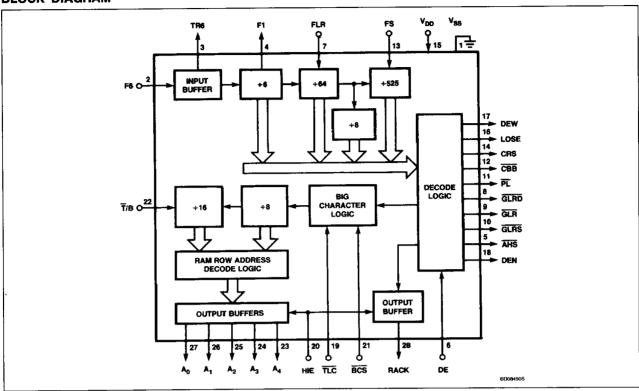

### **BLOCK DIAGRAM**

www.DataSheet4U.com

1 3

www.DataSheet4U.com

SAA5025

# DC AND AC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C; F6 input frequency = 6.041957MHz, unless otherwise specified.

| SYMBOL                              | PARAMETER                                                                                | V <sub>DD</sub> (V) | Limits                  |                                                  |                 |        |

|-------------------------------------|------------------------------------------------------------------------------------------|---------------------|-------------------------|--------------------------------------------------|-----------------|--------|

|                                     |                                                                                          |                     | Min                     | Тур                                              | Max             | UNIT   |

| Supply                              |                                                                                          |                     |                         |                                                  |                 |        |

| V <sub>DD</sub>                     | Supply voltage                                                                           |                     | 4.5                     | 5.0                                              | 5.5             | v      |

| I <sub>DD</sub>                     | Supply current                                                                           | 5                   | 5                       |                                                  | 50              | mA     |

| Inputs                              |                                                                                          |                     |                         |                                                  |                 | •      |

|                                     | Input leakage currents                                                                   |                     |                         |                                                  |                 |        |

| l <sub>1</sub>                      | F6                                                                                       | 5.5                 | 0.2                     |                                                  | 10              | μΑ     |

| –կ<br>±կ                            | FLR, TLC, FS, HIE, BCS, T/B, DE                                                          | 0<br>0 to 5.5       |                         |                                                  | 10              | μA     |

|                                     |                                                                                          |                     |                         |                                                  | 10              | μΑ     |

| Cı                                  | Input capacitance; all inputs                                                            | 5                   | <del></del>             |                                                  | 7               | pF     |

| V                                   | High level input voltages F6 (see Figure 8)                                              | _                   | 0.7                     |                                                  |                 |        |

| V <sub>IH</sub><br>V <sub>IH</sub>  | FLR, TLC, FS, HIE, BCS, T/B, DE                                                          | 5                   | 2.7<br>2.0 <sup>1</sup> |                                                  | 6.5<br>5.5      | V<br>V |

| V <sub>IL</sub>                     | Low level input voltage (all inputs); (see Figure 8)                                     | 5                   | 2.0                     | <del>                                     </del> | 0.81            | v      |

| t <sub>R</sub> , t <sub>F</sub>     | Input rise and fall time F6 (see Figure 4)                                               | 0 and 2.7           | ·                       | -                                                | <del> </del>    |        |

| δ                                   | Input F6 duty factor (see Figure 8)                                                      | 5                   | 40                      | 50                                               | 30              | ns     |

| Outputs                             | input 10 daty lactor (see Figure 6)                                                      | 3                   | 40                      | 50                                               | 56              | %      |

|                                     | Tax                                                                                      | 1                   |                         |                                                  | <del> </del>    | ·      |

| Co                                  | Output node capacitance (all outputs)                                                    | 5                   |                         |                                                  | 7               | pF     |

| ± I <sub>O</sub>                    | Output leakage current high-impedance state; A <sub>0</sub> to A <sub>4</sub> , RACK     | 0 to 5.5            |                         |                                                  | 10              | μΑ     |

| lo                                  | Output leakage current open-drain; PL, CBB                                               | 6                   |                         |                                                  | 10              | μΑ     |

| Output TR6                          | 6.041957MHz clock                                                                        | ot/I                |                         | om                                               | <u> </u>        | ·      |

| VoH                                 | High level output voltage<br>-I <sub>OH</sub> = 100μA                                    | 5                   | 2.75                    | ОП                                               | V <sub>DD</sub> | ٧      |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 100 µA                                        | 5                   | 0                       |                                                  | 0.4             | ٧      |

| CL                                  | Output load capacitance                                                                  | 5                   |                         |                                                  | 15              | pF     |

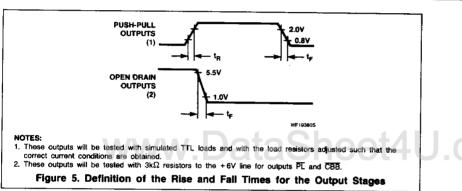

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times (see Figure 5)                                                | 5                   |                         | · · · · · · · · · · · · · · · · · · ·            | 30              | ns     |

| δ                                   | Duty factor at 1.5V level depends on input F6 (see F6 data and Figure 8)                 | 5                   | 40                      |                                                  | 60              | %      |

| Output F1 1.                        | 007MHz clock                                                                             |                     |                         |                                                  |                 |        |

| V <sub>OH</sub>                     | High level output voltage -I <sub>OH</sub> = 100μA                                       | 5                   | 2.75                    |                                                  | V <sub>DD</sub> | ٧      |

| V <sub>OL</sub>                     | Low level output voltage                                                                 | 5                   | 0                       |                                                  | 0.4             | V      |

| CL                                  | Output load capacitance                                                                  | 5                   |                         | -                                                | 40              | pF     |

| t <sub>R</sub> , t <sub>R</sub>     | Output rise and fall times (see Figure 5)                                                | 5                   |                         |                                                  | 50              | ns     |

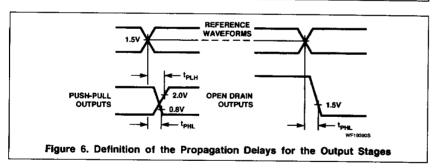

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delays from rising edge of TR6 (see<br>Figure 6) High-to-Low and Low-to-High | 5                   | 7                       |                                                  | 60              | ns     |

| δ                                   | Duty factor at 1.5V level                                                                | 5                   | 45                      | 50                                               | 52              | %      |

----

**SAA5025**

# DC AND AC ELECTRICAL CHARACTERISTICS (Continued) $T_A = 25^{\circ}\text{C}$ ; F6 input frequency = 6.041957MHz, unless otherwise specified.

| SYMBOL PARAMETER                    |                                                                                     | V <sub>DD</sub> | LIMITS |             |                 | UNIT        |

|-------------------------------------|-------------------------------------------------------------------------------------|-----------------|--------|-------------|-----------------|-------------|

|                                     | (V)                                                                                 | Min             | Тур    | Max         | CHI             |             |

| Output AHS                          | (see Figure 6)                                                                      |                 |        | <del></del> |                 |             |

| V <sub>OH</sub>                     | High level output voltage<br>-I <sub>OH</sub> = 200µA                               | 5               | 2.4    |             | V <sub>DD</sub> | ٧           |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 1.6mA                                    | 5               | 0      |             | 0.4             | ٧           |

| <br>C <sub>L</sub>                  | Output load capacitance                                                             | 5               |        |             | 30              | pF          |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times (see Figure 7)                                           | 5               |        |             | 100             | ns          |

| t <sub>PLH</sub>                    | Propagation delay from rising edge of F1 (see Figure 8) Low-to-High                 | 5               | 0      |             | 350             | ns          |

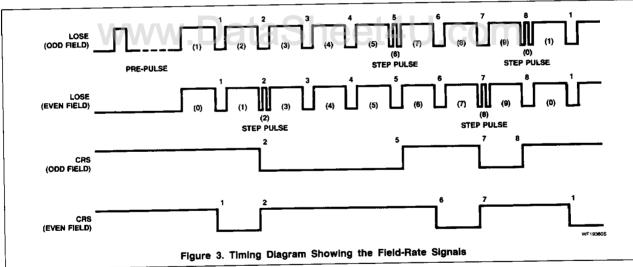

| Outputs GLF                         | R, GLRD, GLRS (see Figure 3)                                                        |                 |        |             |                 |             |

| V <sub>OH</sub>                     | High level output voltage<br>-I <sub>OH</sub> = 100μA                               | 5               | 2.4    |             | V <sub>DD</sub> | V           |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 0.8mA                                    | 5               | 0      |             | 0.4             | V           |

| C <sub>L</sub>                      | Output load capacitance                                                             | 5               |        |             | 40              | pF          |

| t <sub>R</sub>                      | Output rise and fall times (see Figure 7)                                           | 5               |        |             | 70<br>50        | ns<br>ns    |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay from rising edge of F1 (see Figure 8) High-to-Low and Low-to-High | 5               | 0      |             | 300             | ns          |

| Output PL (                         | see Figure 3)                                                                       |                 |        |             | ·               |             |

| V <sub>OL</sub>                     | Low level output voltage                                                            | eet4            | 0      | om          | 1.0             | V           |

| CL                                  | Output load capacitance                                                             | 5               |        |             | 30              | pF          |

| t <sub>F</sub>                      | Output fall time (see Figure 7)                                                     | 5               |        |             | 100             | ns          |

| t <sub>PLH</sub>                    | Propagation delay from rising edge of F1 (see Figure 8) Low-to-High                 | 5               | 0      |             | 250             | ns          |

| Output CBB                          | (see Figure 2)                                                                      |                 |        |             | T               |             |

| VoĽ                                 | Low level output voltage  IoL = 2mA                                                 | 5               | 0      |             | 1.0             | V           |

| CL                                  | Output load capacitance                                                             | 5               |        |             | 30              | pF          |

| t <sub>F</sub>                      | Output fail time (see Figure 5)                                                     | 5               |        |             | 200             | ns          |

| <b>t</b> РLН                        | Propagation delay from rising edge of F1 (see Figure 6) Low-to-High                 | 5               | 0      |             | 250             | ns          |

| Output CRS                          | <b>3</b>                                                                            |                 |        | <del></del> | <del> </del>    | <del></del> |

| V <sub>OH</sub>                     | High level output voltage -I <sub>OH</sub> = 100 μA                                 | 5               | 2.4    |             | V <sub>DD</sub> | V           |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 100 µA                                   | 5               | 0      |             | 0.4             | V           |

| CL                                  | Output load capacitance                                                             | 5               |        |             | 30              | pi          |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times (see Figure 5)                                           | 5               |        |             | 1               | μ           |

www.DataSheet4U.com

# Teletext Timing Chain for USA 525-Line System

**SAA5025**

DC AND AC ELECTRICAL CHARACTERISTICS (Continued) T<sub>A</sub> = 25°C; F6 input frequency = 6.041957MHz, unless otherwise specified.

| SYMBOL                              | DADAMETED                                                                             | V <sub>DD</sub><br>(V) | LIMITS |      |                 |     |

|-------------------------------------|---------------------------------------------------------------------------------------|------------------------|--------|------|-----------------|-----|

|                                     | PARAMETER                                                                             |                        | Min    | Тур  | Max             | UNI |

| Output LOSE                         | (see Figure 1)                                                                        |                        | ·      |      |                 |     |

| V <sub>OH</sub>                     | High level output voltage -I <sub>OH</sub> = 100 <i>µ</i> A                           | 5                      | 2.4    |      | V <sub>DD</sub> | v   |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 100μA                                      | 5                      | 0      |      | 0.4             | ٧   |

| CL                                  | Output load capacitance                                                               | 5                      |        |      | 30              | pF  |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times (see Figure 5)                                             | 5                      |        |      | 50              | ns  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay from rising edge of F1 (see Figure 6) High-to-Low and Low-to-High   | 5                      | 0      |      | 1               | μs  |

| Output DEN                          |                                                                                       |                        | •      |      |                 |     |

| V <sub>OH</sub>                     | High level output voltage<br>-I <sub>OH</sub> = 200µA                                 | 5                      | 2.4    |      |                 | v   |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 100μA                                      | 5                      |        |      | 0.4             | ٧   |

| C <sub>L</sub>                      | Output load capacitance                                                               | 5                      |        |      | 30              | ρF  |

| t <sub>Fi</sub> , t <sub>F</sub>    | Output rise and fall times                                                            | 5                      |        |      | 50              | ns  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay from rising edge of F1;<br>High-to-Low and Low-to-High              | 5                      |        |      | 250             | ns  |

| Output DEW                          | (see Figure 2)                                                                        |                        |        |      |                 |     |

| V <sub>OH</sub>                     | High level output voltage -I <sub>OH</sub> = 200 µA                                   | 5                      | 2.4    | 0100 | V <sub>DD</sub> | v   |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 1.6mA                                      | 5                      | 0,0    | UITI | 0.4             | v   |

| C <sub>L</sub>                      | Output load capacitance                                                               | 5                      |        |      | 50              | pF  |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times                                                            | 5                      |        |      | 200             | ns  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay from rising edge of CBB (see Figure 6) High-to-Low and Low-to-High  | 5                      | 6.5    | 6.96 | 7.5             | μs  |

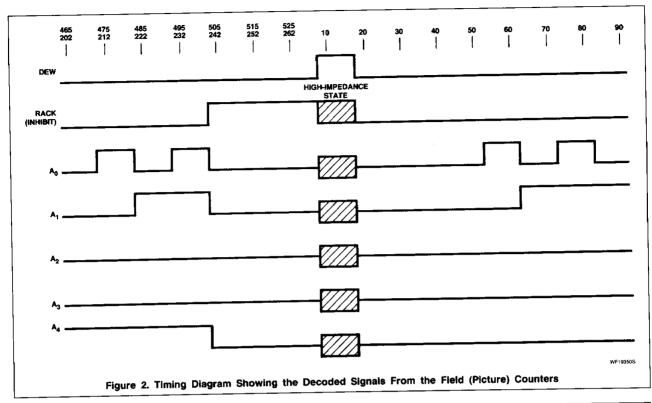

| Outputs A <sub>0</sub> to           | o A <sub>4</sub> (see Figure 2)                                                       |                        |        |      |                 |     |

| V <sub>OH</sub>                     | High level output voltage<br>-I <sub>OH</sub> = 100μA                                 | 5                      | 2.4    |      | V <sub>DD</sub> | V   |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 1.6mA                                      | 5                      | 0      |      | 0.4             | ٧   |

| CL                                  | Output load capacitance                                                               | 5                      |        |      | 85              | pF  |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise and fall times                                                            | 5                      |        |      | 1               | μs  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay from falling edge of CBB (see Figure 6) High-to-Low and Low-to-High | 5                      | 6.5    |      | 9.0             | μs  |

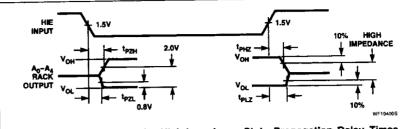

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Propagation delay from rising edge of HIE to high-<br>impedance state (see Figure 7)  | 5                      | 0      |      | 0.9             | μs  |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Propagation delay from falling edge of HIE to normal active state (see Figure 7)      | 5                      | 1      |      | 2.9             | μs  |

**SAA5025**

# DC AND AC ELECTRICAL CHARACTERISTICS (Continued) T<sub>A</sub> = 25°C; F6 input frequency = 6.041957MHz, unless otherwise specified.

| SYMBOL                              | PARAMETER                                                                            | V <sub>DD</sub><br>(V) | LIMITS |     |                 |          |

|-------------------------------------|--------------------------------------------------------------------------------------|------------------------|--------|-----|-----------------|----------|

|                                     |                                                                                      |                        | Min    | Тур | Max             | UNIT     |

| Output RACH                         | ( (see Figures 1 and 2)                                                              |                        |        |     |                 |          |

| V <sub>OH</sub>                     | High level output voltage -I <sub>OH</sub> = 100µA                                   | 5                      | 2.4    |     | V <sub>DD</sub> | ٧        |

| V <sub>OL</sub>                     | Low level output voltage I <sub>OL</sub> = 1.6mA                                     | 5                      | 0      |     | 0.4             | V        |

| CL                                  | Output load capacitance                                                              | 5                      |        |     | 40              | pF       |

| t <sub>R</sub><br>t <sub>F</sub>    | Output rise and fall times (see Figure 5)                                            | 5                      |        |     | 60<br>300       | ns<br>ns |

| t <sub>PHL</sub>                    | Propagation delay from falling edge of F1 (see Figure 6) High-to-Low                 | 5                      | 150    |     | 280             | ns       |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Propagation delay from rising edge of HIE to high-<br>impedance state (see Figure 7) | 5                      | 1      |     | 2.9             | μs       |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Propagation delay from falling edge of HIE to normal active state (see Figure 7)     | 5                      | 0      |     | 0.9             | μs       |

### NOTE:

### **FUNCTIONAL DESCRIPTION**

The basic input to the SAA5025 is a 6.0419 MHz clock signal (e.g., from SAA5030). The clock input (F6) is buffered and also available as an output at TR6 to provide a dot rate clock. The signal at F6 is divided by 6 to produce the 1.007 MHz character rate clock at output F1, which is in turn divided by 64 to produce the line period of  $63.556 \mu s$ . A divide-by-262 or 263 counter,

clocked at line rate, produces a field (picture) period of 16.683ms (average), i.e., 33.366ms for divide-by-525. The display format is 40 characters per row for 24 rows (1 row is 8 TV lines)

A big character select (BSC) input is provided and it enables double-height characters (16 TV lines per row) to be displayed. The top or bottom select (T/B) input must be used in conjunction with BCS to select either the top half or bottom half of the page to be displayed on the television screen.

A composite sync (ĀHS) output is available for synchronizing the display timebase. A high-impedance enable (HIE) input is included to switch the read address clock (RACK) and the memory row address (A<sub>0</sub> to A<sub>4</sub>) outputs into their high-impedance states.

....

<sup>1.</sup> These values give no noise immunity.

### Teletext Timing Chain for USA 525-Line System

SAA5025

January 14, 1987

13-20

SAA5025

January 14, 1987

13-21

.....

**SAA5025**

.....

**SAA5025**

### APPLICATION INFORMATION

The function is described following the corresponding pin number.

### 1 V<sub>SS</sub> -- Ground (0V)

- 2 F6 6.041957MHz Clock Input Obtained from video processor (SAA5030) or other source. The permissible mark/space ratio is in the range from 56:44 to 40:60 (see also Figure 8).

- 3 TR6 6.041957MHz Clock Output Dotrate clock for Teletext character generator SAA5050 series.

- 4 F1 1.007MHz Clock Output Characterrate clock for Teletext character generator SAA5050 series.

- 5 AHS After-Hours Sync Output A composite sync waveform consisting of a successive sequence of line sync pulses (LSP) followed by six equalizing pulses  $(\overline{\mathsf{EP}})$ , six broad pulses (BP), and six equalizing pulses (EP), and is followed by another sequence of LSP. This composite sync waveform occurs at the end and beginning of each field/picture (see also Figure 4).

- 6 DE Display Enable Input A Low level signal from the Teletext acquisition and control circuit (SAA5040 series) to this input switches output DEN to the Low state.

- 7 FLR Fast Line Reset Input This is the input for a positive-going pulse with a duration of 0.5 µs to 63 µs which resets the line rate counter (÷64). After accepting an FLR pulse, further resets are inhibited for one line period of approximately  $63.5 \mu s$ .

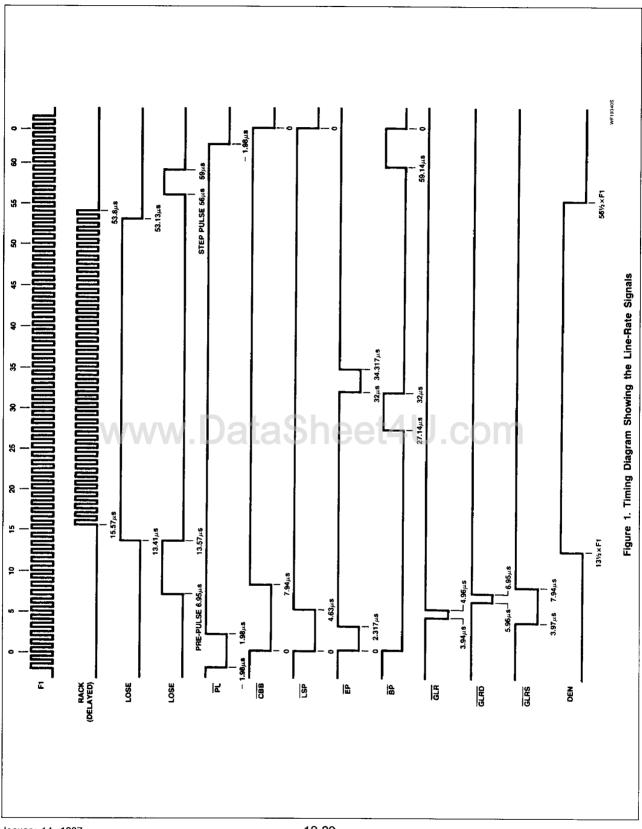

- 8 GLRD General Line Reset Delay Output - A negative-going pulse with a duration of 993ns which commences 5.96 µs from the start of each line (see also Figure 1).

- 9 GLR General Line Reset Output A negative-going pulse with a duration of 993ns which commences 3.97 µs from the start of each line (see also Figure 1).

- 10 GLRS General Line Reset Starting Output - A negative-going pulse with starting  $3.97\mu s$  and ending  $7.94\mu s$  from the start of each line (see also Figure 1).

- 11 PL Phase-Locked Open-Drain Output - This open-drain output is used to lock the oscillator in the SAA5030 to the line rate. It is a negative-going pulse with a duration of 3.96 µs which starts at 61.58 µs on one line and ends at  $1.98\mu s$  after the start of the following line (see also Figure 1).

- 12 CBB Color Burst Blanking Output -This open-drain output blanks the color burst in the SAA5030. It is a 7.94 µs negative-going pulse which starts at the beginning of each line (t = 0; see also Figure 1).

January 14, 1987

Figure 7. Definitions of the High-Impedance State Propagation Delay Times

- 3. The duty factor is defined as:

- Figure 8. Recommended 6MHz interface Circuitry Between the SAA5025 and the SAA5030 (Input F6)

- 13 FS Field (Picture) Sync Input This input accepts a positive-going pulse of approximately 160 µs duration. Its leading edge occurs during the second half of line one on even fields (half picture) and correspondingly in odd fields (other half picture). It is ignored during the odd field.

- 14 CRS Character Rounding Select Output - The output signal starts High during the even field (lines 1 to 263), goes Low after the first LOSE pulse, again High after the second LOSE pulse, then Low after the sixth LOSE pulse, and finally High at the end of the seventh LOSE pulse. This sequence repeats every 8 lines (every row) for the entire display period (see also Figure 3). For the odd field (lines 264 to 525) CRS starts High, goes Low after the second LOSE pulse, again High after the fifth LOSE pulse, then Low after the seventh LOSE pulse and finally High at the end of the eighth LOSE pulse. This sequence repeats every 8 lines (every row) for the entire display period (see also Figure 3).

- 15 V<sub>DD</sub> Positive Supply (+5V)

- 16 LOSE Load Output Shift Register Enable Output - This is a positive-going output pulse of 39.72 µs duration commencing 13.41 us from start of line valid during line 47 to 238 inclusive, for the even field. A step-

pulse starting at the count of 3 character rate clock pulses (F1) after the second and seventh LOSE pulses and at the count of 3 character rate clock pulses repeated every row is included. For the odd field, the LOSE pulse is preceded by a pre-pulse of  $7\mu s$ duration commencing 7.41 µs in line 20, and has a step-pulse after the fifth and eighth pulse, repeated every row (see also Figure 3).

- 17 DEW Data Entry Window Output -This output defines the period during which data may be extracted from the incoming television signal. It is High during lines 7 to 18 inclusive for the even fields and line 270 to 281 inclusive for the odd fields. The positivegoing pulse has a duration of 762.67 µs and commences at 6.95 µs from the start of the line (see also Figure 2).

- 18 DEN Display Enable Output The output pulse is positive-going at 13.5 µs from the start of a line to 56.5 µs and is active during line 47 to 238 inclusive if the DE input is High. If the DE input is Low, the DEN is held in the Low state.

- 19 TLC Transmitted Large Characters Input - When this input is Low, it enables rows of double-height characters to be displayed as required. Large characters descend into the next memory row address location. TLC is

SAA5025

always High (i.e., small) for the first line of a row, even if it contains large characters.

20 HIE High Impedance Enable input — When this input is in the High state, it will force the RACK and memory row address output into the high-impedance state. For normal Teletext operation, this input should be connected to the DEW output (Pin 17).

21 BCS Big Character Select Input — For normal size character display, this input signal must be High while a Low gives double-height characters.

22 T/B Top/Bottom Select Input — When both BCS and T/B are Low, the top half of a page is displayed with double-height characters. If T/B is High and BCS is Low, the

bottom half of the page is also displayed with double-height characters.

23 to 27  $A_0$  to  $A_4$  Memory Row Address Outputs (3-State) — These binary count outputs sequencing from 00000 (count 0) to address 10111 (count 23) for the 40  $\times$  24 format.

The binary count changes every 8 TV lines per row in the display period of line 47 to 238 inclusive for the 24-row display. The count changes between 6.5 µs and 9.0 µs during the line period.

28 RACK Read Address Clock Output — This is the read address clock output to the SAA5045 (GALA) column address counter during the display period. It consists of 39 positive pulses at the 1.007MHz rate starting

at  $13.57\mu s$  from the start of the line period with the last negative edge occurring at  $51.8\mu s$ . This sequence is active on line 45 to 238 inclusive. RACK is delayed by two F1 clock periods for the whole of the field when input DE is Low for the whole of line 39. On lines 19 to 44 inclusive, output RACK is permanently delayed by two F1 clock periods, unaffected by DE.

#### NOTES:

- In the big character top mode the memory row address count is 0 to 11, and in the big character bottom mode the count is 12 to 23. Each big character row is equal to 16 television lines.

- The memory row addresses are held Low for one line period starting 6.5 µs to 9 µs from the beginning of line 36 which is only valid in the big character bottom mode.

www.DataSheet4U.com

January 14, 1987

13-24

-- -