|     | REALGICAG                                                                                                                                                |                 |            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|

| LTR | DESCRIPTION                                                                                                                                              | DATE (YR-MO-DA) | APPROVED   |

| A   | Added case outline letter U to the drawing. Removed ESDS requirements from drawing. Editorial changes throughout.                                        | 90-01-26        | M. A. Frye |

| В   | Removed "Delay to next write" (t <sub>DVWL</sub> , t <sub>DVEL</sub> ) test from table I and figures 5 and 6. Corrected figure 1 dimensions.             | 92-03-04        | M. A. Fry  |

| С   | Redrawn with changes. Add device type 05. Add software data protect. Added ander CAGE 60395 and 61394 as approved sources. Editorial changes throughout. | 92-12-18        | M.A. Frye  |

# THE ORIGINAL FIRST PAGE OF THIS DRAWING HAS BEEN REPLACED.

|                                                                                                |                      |         |    |                  |                  |            |     |    | ,   |                                                                            |     |     |    |      |      |    |    |    |    |    |

|------------------------------------------------------------------------------------------------|----------------------|---------|----|------------------|------------------|------------|-----|----|-----|----------------------------------------------------------------------------|-----|-----|----|------|------|----|----|----|----|----|

| REV                                                                                            |                      |         |    |                  |                  |            |     |    |     |                                                                            |     |     |    |      |      |    |    |    |    |    |

| SHEET                                                                                          |                      |         |    |                  |                  |            |     |    |     |                                                                            |     |     |    |      |      |    |    |    |    |    |

| REV                                                                                            | A                    | Α       | С  | С                | С                | С          | С   | С  | С   |                                                                            |     |     |    |      |      |    |    |    |    |    |

| SHEET                                                                                          | 15                   | 16      | 17 | 18               | 19               | 20         | 21  | 22 | 23  |                                                                            |     |     |    |      |      |    |    |    |    |    |

| REV STAT                                                                                       | JS                   |         |    | RE               | REV C C C        |            |     | С  | U   | С                                                                          | С   | С   | С  | С    | С    | A  | С  | С  |    |    |

| OF SHEETS                                                                                      | 5                    |         |    | SH               | EET              |            | 1   | 2  | 3   | 4                                                                          | 5   | 6   | 7  | 8    | 9    | 10 | 11 | 12 | 13 | 14 |

| PMIC N/A                                                                                       |                      |         |    |                  | ARED E           |            |     |    |     | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                       |     |     |    |      |      |    |    |    |    |    |

|                                                                                                |                      |         | ,  |                  | KED BY<br>Monnir |            |     |    |     |                                                                            |     |     |    |      |      |    |    |    |    |    |

|                                                                                                | ARDI<br>ITAI<br>AWIN | RY      | •  |                  | OVED E           | BY<br>Frye |     |    |     | MICROCIRCUITS, MEMORY, DIGITAL, CMOS<br>32K X 8 EEPROM, MONOLITHIC SILICON |     |     |    |      |      |    |    |    |    |    |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE |                      |         |    |                  |                  |            | SIZ |    | CAG | E CO                                                                       | DE  |     | 59 | 062- | 8863 | 34 |    |    |    |    |

| VERARIMEN                                                                                      | ii or l              | ELEM 21 | •  | REVISION LEVEL C |                  |            |     |    | A   |                                                                            | -   | 726 | 8  |      |      |    |    |    |    |    |

| AM:                                                                                            | SC N/A               |         |    |                  |                  |            |     |    |     | SHI                                                                        | EET |     | 1  |      | OF   |    | 23 |    |    |    |

|                                                                                                |                      |         |    |                  |                  |            |     |    |     |                                                                            |     |     |    |      |      |    |    |    |    |    |

DESC FORM 193

JUL 91

5962-E604-92

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

9004708 0010777 554 📟 ,

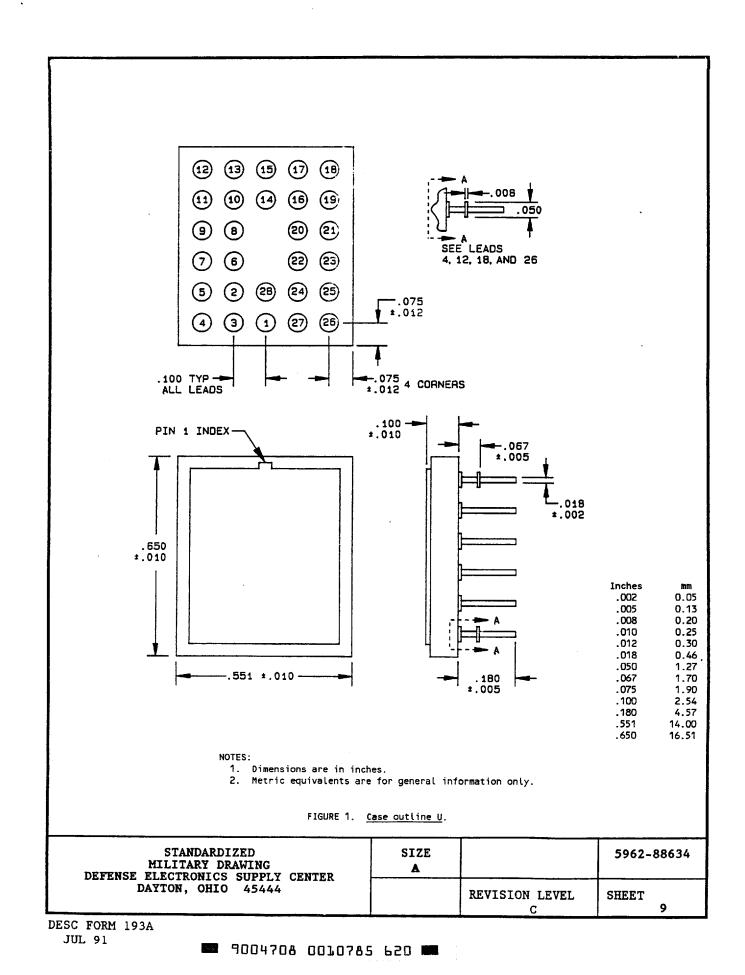

LOPE This drawing describes device requirements for class 3 migrocircuits in accordance with 1.2.1 of Topps. This drawing describes device requirements for class 3 microcircuits in accordance with 31.3.3, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". Fort or Identifying Number (PIN). The complete PIN shall be as shown in the following example: 5962**-88**6**34** Lead finish per Case outline Device type Crawing number MIL-M-38510 (see 1.2.1) (see 1.2.2) 1.2.1 Device type(s). The device type(s) shall identify the circuit function as follows: Write Circuit Access Dovice Coneric speed Write mode End of write indicator Endurance function <u>time</u> tyng number DATA polling/toggle bit 10,000 cycles 32K x 8 EEPROM Sec 6.6 120 ກຣ 10 ms byte/page 01 10,000 cycles DATA polling/toggle bit 120 ns 3 ms byte/page 32K x 8 EEPROM See 6.6 02 10,000 cycles 32K x 8 EEPROM 90 ns 10 ms byte/page DATA polling/toggle bit 03 See 6.6 90 ns 3 ms byte/page DATA polling/toggle bit 10,000 cycles 32K x 8 EEPROM See 6.6 04 10,000 cycles DATA polling/toggle bit 32K x 8 EEPROM 70 ns 10 ms byte/page OS Sec 6.6 1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows: Package style **Terminals** Descriptive designator Outline letter 28 Pin grid array See figure 1 Dual-in-line GDIP1-T28 or CDIP2-T28 28 Х Rectangular leadless chip carrier 32 cqcc1-N32 28 Flat pack CDFP4-F28 1.3 Absolute maximum ratings. 1/ 1.4 Recommended operating conditions. 1/ All voltages are referenced to V<sub>SS</sub> (ground).

Z/ Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions in accordance with method 5004 of MIL-STD-883.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE A |                     | 5962-88634 |

|------------------------------------------------------|--------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |        | REVISION LEVEL<br>C | SHEET 2    |

DESC FORM 193A

JUL 91

**5** 9004708 0010778 490 **5**

2 = LICALLE DOCUMENTS

2.\* Transment specification, standards, and bulletin. Unless otherwise specified, the following specification, standards, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510 - Microcircuits, General Specification for.

STANDARDS

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-1835 - Microcircuit Case Outlines.

BULLETIN

MILITARY

MIL-BUL-103 - List of Standardized Military Drawings (SMD's).

(Copies of the specification, standards, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 2.

- 3.2.2 Truth table(s). The truth table(s) shall be as specified on figure 3.

- 3.2.2.1 <u>Unprogrammed or erased devices</u>. The truth table for unprogrammed devices shall be as specified on figure 3.

- 3.2.2.2 Programmed devices. The requirements for supplying programmed devices are not part of this drawing.

- 3.2.3 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-88634 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET<br>3 |

DESC FORM 193A

JUL 91

9004708 0010779 327

| Test                                         | Symbol                                  | Symbol   Conditions                                                                                                                                                                                            |                       | Device       |                    | <br>  Un                         |    |

|----------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--------------------|----------------------------------|----|

| rest                                         | ayimuOt                                 | Conditions<br>  $-55^{\circ}\text{C} \leq T_{\text{C}} \leq +125^{\circ}\text{C},$<br>  $V_{\text{SS}} = 0 \text{ V}, 4.5 \text{ V} \leq V_{\text{CC}} \leq 5.5 \text{ V},$<br>  unless otherwise specified 1/ | Group A<br> subgroups | types        | Min                | imits<br> <br>  Max              |    |

| Supply current<br>(operating)                | I <sub>CC1</sub>                        | CE = OE = V <sub>II</sub> , WE = V <sub>IH</sub> ,<br>  all I/O's = 0.0 mA,<br>  inputs = V <sub>CC</sub> = 5.5 V,<br>  t <sub>AVAV</sub> = t <sub>AVAV</sub> (min)                                            | 1, 2, 3               | All          |                    | 80                               | mA |

| Supply current (ITL standby)                 | I <sub>CC2</sub>                        |                                                                                                                                                                                                                | 1, 2, 3               | 01,02        |                    | 3                                | mA |

| •                                            |                                         | inputs = V <sub>CC</sub> - 0.3 V,<br> f = 0.0 MHz                                                                                                                                                              |                       | 03,04,<br>05 |                    | 60                               |    |

| Supply current<br>(CMOS standby)             | I <sub>CC</sub> 3                       | <u> </u>                                                                                                                                                                                                       | 1, 2, 3               | 01,02        |                    | 350                              | μΑ |

| inputs = V <sub>IL</sub> or V<br>f = 0.0 MHz | inputs = $V_{T1}$ or $V_{CC} - 0.3 V$ , |                                                                                                                                                                                                                | 03,04,                |              | 60                 | mA                               |    |

| Input leakage (high)                         | IIH                                     | V <sub>IN</sub> = 5.5 V                                                                                                                                                                                        | 1, 2, 3               | ALL          |                    | 10                               | μа |

| Input leakage (low)                          | IIL                                     | V <sub>IN</sub> = 0.1 V                                                                                                                                                                                        | 1, 2, 3               | ALL          | -10                |                                  | μΑ |

| Output leakage (high)                        | IOHZ                                    | V <sub>OUT</sub> = 5.5 V, CE = V <sub>IH</sub> <u>2</u> /                                                                                                                                                      | 1, 2, 3               | ALL          |                    | 10                               | μΑ |

| Output leakage (low)                         | IOLZ                                    | V <sub>OUT</sub> = 0.1 V, CE = V <sub>IH</sub> <u>2</u> /                                                                                                                                                      | 1, 2, 3               | ALL          | -10                |                                  | μА |

| Input voltage low                            | VIL                                     |                                                                                                                                                                                                                | 1, 2, 3               | ALL          | <br>  <b>-</b> 0.1 | 0.8                              | V  |

| Input voltage high                           | V <sub>IH</sub>                         |                                                                                                                                                                                                                | 1, 2, 3               | ALL          | 2.0                | <br> V <sub>6</sub> c<br> +0.3 V | V  |

| Output voltage low                           | v <sub>oL</sub>                         | I <sub>OL</sub> = 6.0 mA, V <sub>IH</sub> = 2.0 V,   V <sub>CC</sub> = 4.5 V, V <sub>IL</sub> = 0.8 V                                                                                                          | 1, 2, 3               | ALL          |                    | 0.45                             | \  |

| Output voltage high                          | v <sub>он</sub>                         | I <sub>OH</sub> = -4.0 mA, V <sub>IH</sub> = 2.0 V,<br>  V <sub>CC</sub> = 4.5 V, V <sub>IL</sub> = 0.8 V                                                                                                      | 1, 2, 3               | ALL          | 2.4                |                                  | V  |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88634 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>4 |

DESC FORM 193A JUL 91

; 🔜 9004708 0010780 049 📟 .

| Test                              | Symbol            | Conditions                                                                                                                       | Group A   | Device       | <u></u> | Unit |    |

|-----------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|---------|------|----|

|                                   |                   | $V_{SS} = 0 \text{ V}$ , $4.5 \text{ V} = V_{CC} \le 5.5 \text{ V}$ , unless otherwise specified 1/                              | subgroups | types        | Min     | Max  |    |

| OE high leakage<br>(chip erase)   | IOE               | V <sub>H</sub> = 13 V                                                                                                            | 1, 2, 3   | A11          | -10     | 100  | μΑ |

| Input capacitance                 | cI                | $V_{T} = 0 \text{ V}, V_{C'} = 1.0 \text{ V},$<br>$T_{A}^{2} = +25^{\circ}\text{C}, f = 1 \text{ MHz},$<br>see 4.3.1c = 3.7  4.7 | 4         | All          |         | 10   | pF |

| Output capacitance                | c <sub>o</sub>    | V <sub>0</sub> = 0 V, V <sub>CC</sub> = 5.6 V,<br>T <sub>A</sub> = 25°C, 1 = 5.6 V,<br>see 4.3.1c 3/4/                           | 4         | All          |         | 10   | pF |

| Read cycle time                   | tavav             |                                                                                                                                  | 9, 10, 11 | 01,02        | 120     |      | ns |

|                                   |                   |                                                                                                                                  |           | 03,04        | 90      |      |    |

|                                   |                   | 1                                                                                                                                |           | 05           | 70      |      |    |

| Address access time               | t <sub>AVQV</sub> |                                                                                                                                  | 9, 10, 11 | 01,02        |         | 120  | ns |

|                                   |                   |                                                                                                                                  |           | 03,04        |         | 90   | _  |

|                                   | <u> </u>          | <u> </u>                                                                                                                         | +         | 05           | ļ       | 70   |    |

| Chip enable access time           | tELQV             |                                                                                                                                  | 9, 10, 11 | 01,02        |         | 120  | ns |

|                                   |                   |                                                                                                                                  |           | 03,04        |         | 90   |    |

|                                   |                   | 1                                                                                                                                | -         | 05           |         | 70   |    |

| Output enable access t            | t <sub>OLQV</sub> |                                                                                                                                  | 9, 10, 11 | 01,02        |         | 50   | ns |

|                                   |                   | <u> </u>                                                                                                                         |           | 03,04,<br>05 |         | 40   |    |

| Chip enable to output in low Z 4/ | t <sub>ELQX</sub> |                                                                                                                                  | 9, 10, 11 | All          | 10      |      | ns |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-88634 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 5    |

DESC FORM 193A JUL 91

📰 9004708 0010781 T85 📟

| Test                                  | Symbo1            | Conditions                                                                                                                                                                                                                                                       | Group A   | Device<br>types | Limits |     | Unit |

|---------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|--------|-----|------|

| 1001                                  |                   | $\begin{array}{c} -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}, \\ \text{V}_{\text{SS}} = 0 \text{ V}, \ 4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}, \\ \text{unless otherwise specified } \underline{1}/ \end{array}$ | subgroups |                 | Min    | Max |      |

| Chip disable to output in high Z 4/   | t <sub>EHQZ</sub> | See figure 4 <u>5</u> /                                                                                                                                                                                                                                          | 9, 10, 11 | 01,02           |        | 50  | ns   |

|                                       |                   |                                                                                                                                                                                                                                                                  |           | 03,04,<br>05    |        | 40  |      |

| Output enable to output in low Z 4/   | <sup>t</sup> oLQX | 1.                                                                                                                                                                                                                                                               | 9, 10, 11 | All             | 10     |     | ns   |

| Output disable to output in high Z 4/ | <sup>t</sup> onqz |                                                                                                                                                                                                                                                                  | 9, 10, 11 | 01,02           |        | 50  | ns   |

| ·                                     |                   | <u> </u>                                                                                                                                                                                                                                                         |           | 03,04,<br>05    |        | 40  |      |

| Output hold from address change       | <sup>t</sup> AXQX |                                                                                                                                                                                                                                                                  | 9, 10, 11 | All             | 0      |     | ns   |

| Write cycle time                      | twHWL1<br>teHEL1  | See figures 5, 6, and 7 (as applicable to <u>5</u> /)                                                                                                                                                                                                            | 9, 10, 11 | 01,03,<br>05    |        | 10  | ms   |

|                                       |                   |                                                                                                                                                                                                                                                                  |           | 02,04           |        | 3   |      |

| Address setup time                    | tavel<br>tavwl    |                                                                                                                                                                                                                                                                  | 9, 10, 11 | All             | 20     |     | ns   |

| Address hold time                     | t <sub>ELAX</sub> |                                                                                                                                                                                                                                                                  | 9, 10, 11 | All             | 50     |     | ns   |

| Write setup time                      | t <sub>WLEL</sub> |                                                                                                                                                                                                                                                                  | 9, 10, 11 | All             | 0      |     | ns   |

| Write hold time                       | t <sub>EHWH</sub> |                                                                                                                                                                                                                                                                  | 9, 10, 11 | All             | 0      |     | ns   |

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 5962-88634 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET 6    |

DESC FORM 193A JUL 91

**==** 9004708 0010782 911 **==**

| Test                                | Symbol                                 | Conditions                                                                                                                              | Group A            | Device | <u> </u>    | Unit           |            |

|-------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-------------|----------------|------------|

|                                     |                                        | -55°C ≤ T <sub>C</sub> ≤ ÷125°C,<br> V <sub>SS</sub> = 0 V, 4.5°V ≤ V <sub>CC</sub> ≤ 5.5 V,<br>  unless otherwish specified <u>1</u> / | subgroups          | types  | Min         | Max            | }<br> <br> |

| OF setur time                       | <sup>t</sup> OHEL<br><sup>t</sup> OHWL | <br> See figures 5, 6, and 7 (as<br>  applicable to <u>2</u> 2)                                                                         | 9, 10, 11          | ALL    | 0           |                | ns         |

| OE hols time                        | t <sub>EHOL</sub>                      | ;<br> <br>                                                                                                                              | 9, 10, 11          | ALL    | O           | <br> <br> <br> | ns         |

| WF oulse width                      | t <sub>ELEH</sub>                      | <br>                                                                                                                                    | 9, 10, 11          | ALL    | 150         |                | ns         |

| Data setup time                     | TDVEH                                  |                                                                                                                                         | <br> 9, 10, 11<br> | All    | 50          |                | กร         |

| Data hold time                      | t <sub>EHDX</sub>                      |                                                                                                                                         | 9, 10, 11          | ALL    | 0           | <br> <br>      | ns         |

| Byte load cycle                     | twHWL2                                 |                                                                                                                                         | 9, 10, 11          | ALL    | .20         | 149            | hs         |

| Last byte loaded to data polling 4/ | tWHEL<br>tehel                         |                                                                                                                                         | 9, 10, 11          | ALL    | 1           | 0              | ns         |

| CE setup time                       | tELWL                                  | <br> See figure 8 <u>5</u> /<br><u> </u>                                                                                                | 9, 10, 11          | ALL    | 5           |                | μs         |

| Output setup time                   | tovhwL                                 | <br>                                                                                                                                    | 9, 10, 11          | ALL    | 5           |                | μs         |

| CE hold time                        | twHEH                                  |                                                                                                                                         | 9, 10, 11          | ALL    | <br>  5<br> |                | μs         |

| OE hold time                        | twhoh                                  | <u>T</u><br>                                                                                                                            | 9, 10, 11          | ALL    | 5           |                | <br> μs    |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88634 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>7 |

DESC FORM 193A JUL 91

9004708 0010783 858

| Test                          | Symbol             | Conditions                                                                                          |           | Device | Limits |     | Unit |

|-------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|-----------|--------|--------|-----|------|

|                               |                    | $V_{SS} = 0 \text{ V}, 4.5 \text{ V} \leq V_{CC} \leq 5.5 \text{ V},$ unless otherwise specified 1/ | subgroups | types  | Min    | Max |      |

| High voltage                  | v <sub>H</sub>     | See figure 8 <u>5</u> /                                                                             | 9, 10, 11 | All    | 12     | 13  | ٧    |

| Chip erase                    | twLwH2             |                                                                                                     | 9, 10, 11 | All    |        | 210 | ms   |

| WE pulse width for chip erase | t <sub>WLWH1</sub> |                                                                                                     | 9, 10, 11 | All    | 10     |     | ms   |

1/ DC and read mode. 2/ Connect all address inputs and  $\overline{\text{OE}}$  to  $\text{V}_{\text{IH}}$  and measure  $\text{I}_{\text{OLZ}}$  and  $\text{I}_{\text{OHZ}}$  with the output under

test connected to V<sub>OUT</sub>.

All pins not being tested are to be open.

Tested initially and after any design or process changes that affect that parameter, and therefore shall be quaranteed to the limits specified in table I.

5/ Tested by application of specified timing signals and conditions, including:

Equivalent ac test conditions:

Devices: 01 through 05. Output load: 1 TTL gate and  $C_L$  = 100 pF (minimum) or equivalent circuit. Input rise and fall times  $\leq$  10 ns. Input pulse levels: 0.4 V and 2.4 V.

Timing measurements reference levels:

Inputs 1.0 V and 2.0 V. Outputs 0.8 V and 2.0 V.

- 3.7 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DESC-EC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 Processing EEPROMS. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.10.1 <u>Erasure of EEPROMS</u>. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.4.3. Unless otherwise specified, devices shall be shipped in the erased (logic "1's") and verified state.

- 3.10.2 Programmability of EEPROMS. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.4.2. Software data protect procedures shall be as specified in 4.4.5.

- 3.10.3 Verification of erasure or programmability of EEPROMS. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of reading the device in accordance with the procedures and characteristics specified in 4.4.4. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                     | 5962-88634 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET 8    |

DESC FORM 193A **JUL 91**

**9**004708 0010784 794 **9**

Powered by ICminer.com Electronic-Library Service CopyRight 2003

| Device types    | 01 thro         | ugh 05          |

|-----------------|-----------------|-----------------|

| Case outlines   | X, Z, U         | Y               |

| Terminal number | Terminal        | symbol          |

| 1               | A <sub>14</sub> | NC              |

| 2               | A <sub>12</sub> | A <sub>14</sub> |

| 3               | A <sub>7</sub>  | A <sub>12</sub> |

| 4               | A <sub>6</sub>  | A <sub>7</sub>  |

| 5               | A <sub>5</sub>  | A <sub>6</sub>  |

| 6               | A <sub>4</sub>  | A <sub>5</sub>  |

| 7               | A <sub>3</sub>  | A <sub>4</sub>  |

| 8               | A <sub>2</sub>  | A3              |

| 9               | A <sub>1</sub>  | A <sub>2</sub>  |

| 10              | A <sub>O</sub>  | A <sub>1</sub>  |

| 11              | 1/00            | A <sub>O</sub>  |

| 12              | 1/01            | NC              |

| 13              | 1/02            | 1/00            |

| 14              | v <sub>SS</sub> | 1/01            |

| 15              | 1/03            | 1/02            |

| 16              | 1/04            | v <sub>ss</sub> |

| 17              | 1/05            | NC              |

| 18              | 1/06            | 1/03            |

| 19              | 1/07            | 1/04            |

| 20              | <u>CE</u>       | 1/05            |

| 21              | A <sub>10</sub> | 1/06            |

| 22              | ŌĒ              | 1/07            |

| 23              | A <sub>11</sub> | CE '            |

| 24              | A <sub>9</sub>  | <u>A</u> 10     |

| 25              | A <sub>8</sub>  | <u>OE</u>       |

| 26              |                 | NC              |

| 27              | A <sub>13</sub> | A <sub>11</sub> |

| 28              | v <sub>cc</sub> | A <sub>9</sub>  |

| 29              |                 | A <sub>8</sub>  |

| 30              |                 | A <sub>13</sub> |

| 31              |                 | ME <sub>2</sub> |

| 32              |                 | v <sub>cc</sub> |

FIGURE 2. <u>Terminal connections</u>.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88634  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>10 |

**9**004708 0010786 567 **5**

# Device types 01 through 05

| Mode          | ÇE              | <u>OE</u>       | WE              | 1/0                     |

|---------------|-----------------|-----------------|-----------------|-------------------------|

| Read          | V <sub>1L</sub> | VIL             | v <sub>IH</sub> | D <sub>OUT</sub>        |

| Standby       | VIH             | х               | Х               | High Z                  |

| Chip clear    | VIL             | v <sub>H</sub>  | VIL             | x                       |

| Byte write    | VIL             | V <sub>IH</sub> | VIL             | D <sub>IN</sub>         |

| Write inhibit | х               | V <sub>IL</sub> | х               | High Z/D <sub>OUT</sub> |

| Write inhibit | х               | х               | v <sub>IH</sub> | High Z/D <sub>OUT</sub> |

V<sub>IH</sub> = High logic leve?

V<sub>IL</sub> = Low logic leve1

V<sub>H</sub> = Chip clear high voltage

X = Don't care

High Z = High impedance state

D<sub>IN</sub> = Data in

D<sub>OUT</sub> = Data out

FIGURE 3. Truth table for unprogrammed devices.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-88634 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 11   |

DESC FORM 193A JUL 91

9004708 0010787 413

■ 9004708 0010789 276 ■

💌 9004708 0010791 924 💌

🕶 9004708 0010792 860 **=**

**■ 9004708 0010793 7T7 ■**

**∞** 9004708 0010794 633 **■**

Powered by ICminer.com Electronic-Library Service CopyRight 2003

#### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D or F using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_{\Delta} = +125$ °C, minimum.

- (3) Devices shall be burned-in containing a checkerboard pattern or equivalent.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- c. An endurance/retention test prior to burn-in, in accordance with method 1033 of MIL-STD-883, shall be included as part of the screening procedure with the following conditions:

- (1) Cycling may be block, byte, or page at equipment room ambient temperature and shall cycle all bytes for a minimum of 10,000 cycles.

- (2) After cycling, perform a high temperature unbiased bake for 72 hours at +150°C (minimum). The storage time may be accelerated by using higher temperature in accordance with the Arrhenius relationship:

$$A_{F} = e^{-\frac{E_{A}}{K} \left[ \frac{1}{T_{1}} - \frac{1}{T_{2}} \right]}$$

$A_F$  = acceleration factor (unitless quantity) =  $t_1/t_2$ .

$T^{\Gamma}$  = temperature in Kelvin (i.e., °C + 273 = K).

$t_1$  = time (hrs) at temperature  $T_1$ .

$t_2^{\prime}$  = time (hr.s) at temperature  $T_2^{\prime}$ .  $K^{\prime}$  = Boltzmanns constant = 8.62 x  $10^{-5}$  eV/°K using an apparent activation

energy ( $E_{\Delta}$ ) of 0.6 eV.

The maximum storage temperature shall not exceed +200°C for packaged devices or +300°C for unassembled devices.

- (3) Read the data retention pattern and test using subgroups 1, 7, and 9 (at the manufacturer's option, high temperature equivalent subgroups 2, 8A, and 10 or low temperature equivalent subgroups 3, 8B, and 11 may be used in lieu of subgroups 1, 7, and 9) after cycling and bake, prior to burn-in. Devices having bits not in the proper state after storage shall constitute a device failure.

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

# 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5003 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C<sub>I</sub> and C<sub>O</sub> measurements) shall be measured for initial qualification and after process or design changes which may affect capacitance. Sample size is 15 devices, all input and output terminals tested, and no failures.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                     | 5962-88634 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET 20   |

DESC FORM 193A JUL 91

**9**004708 0010796 406 **=**

- 4.3.2 Group C inspection. Group C inspection shall be in accordance with table III of method 5005 of MIL-STD-883 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. All devices requiring end-point electrical testing shall be programmed with a checkerboard or equivalent alternating bit pattern.

- c. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition D or F using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- d. An endurance test, in accordance with method 1033 of MIL-STD-883, shall be added to group C1 inspection prior to performing the steady-state life test (see 4.3.2c) and extended data retention (see 4.3.2e). Cycling may be block, byte, or page from devices passing group A after the completion of the requirements of 4.2 herein. Initially, two groups of devices shall be formed, cell 1 and cell 2. The following conditions shall be met:

- (1) Cell 1 shall be cycled at -55°C and cell 2 shall be cycled at +125°C for a minimum of 10,000 cycles.

- (2) Perform group A, subgroups 1, 7, and 9 after cycling. Form two new cells (cells 3 and 4) for steady-state life and extended data retention. Cell 3 for steady-state life test consists of 1/2 of the devices from cell 1 and 1/2 of the devices from cell 2. Cell 4 for extended data retention consists of the remaining devices from cells 1 and 2.

- (3) The sample plans for cell 1, cell 2, cell 3, and cell 4 shall individually be the same as for group C1, as specified in method 5005 of MIL-STD-883.

- e. Extended data retention shall consist of:

- (1) All devices shall be programmed with a charge on all memory cells in each device, such that the cell will read opposite the state that the cell would read in its equilibrium state (e.g., worst case pattern, see 4.2c(2)).

- (2) Unbiased bake for 1,000 hours (minimum) at +150°C (minimum). The unbiased bake time may be accelerated by using higher temperature in accordance with the Arrhenius Relationship:

$$A_{F} = e^{-\frac{E_{A}}{K} \left[ \frac{1}{T_{1}} - \frac{1}{T_{2}} \right]}$$

$A_F = acceleration factor (unitless quantity) = t_1/t_2$ .

T' = temperature in Kelvin (i.e., °C + 273 = K).

$t_1$  = time (hrs) at temperature  $T_1$ .

$t_2^{1}$  = time (hrs) at temperature  $t_2^{1}$ .  $t_2^{2}$  = time (hrs) at temperature  $t_2^{1}$ . The maximum storage temperature shall not exceed +200°C for packaged devices or +300°C for unassembled devices

- (3) Read the pattern after bake and perform end-point electrical tests for table II herein for group C.

- 4.3.3 Group D inspection. Group D inspection shall be in accordance with table IV of method 5005 of MIL-STD-883 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. All devices requiring end-point electrical testing shall be programmed with a checkerboard or equivalent alternating bit pattern.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88634 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET 21   |

DESC FORM 193A

JUL 91

9004708 0010797 342

- 4.4 Methods of inspection. Methods of inspection shall be as specified in the appropriate tables of method 5005 of MIL-SID-883 and as follows.

- 4.4.1 <u>Voltage and current</u>. All voltages given are referenced to the microcircuit V<sub>SS</sub> terminal. Currents given are conventional current and positive when flowing into the referenced terminal.

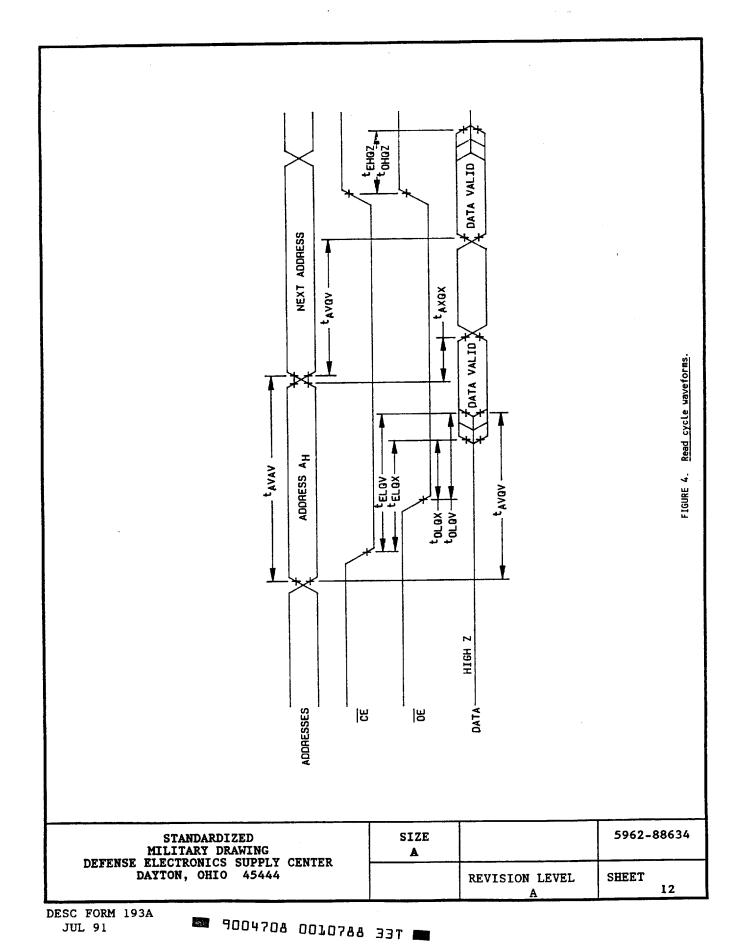

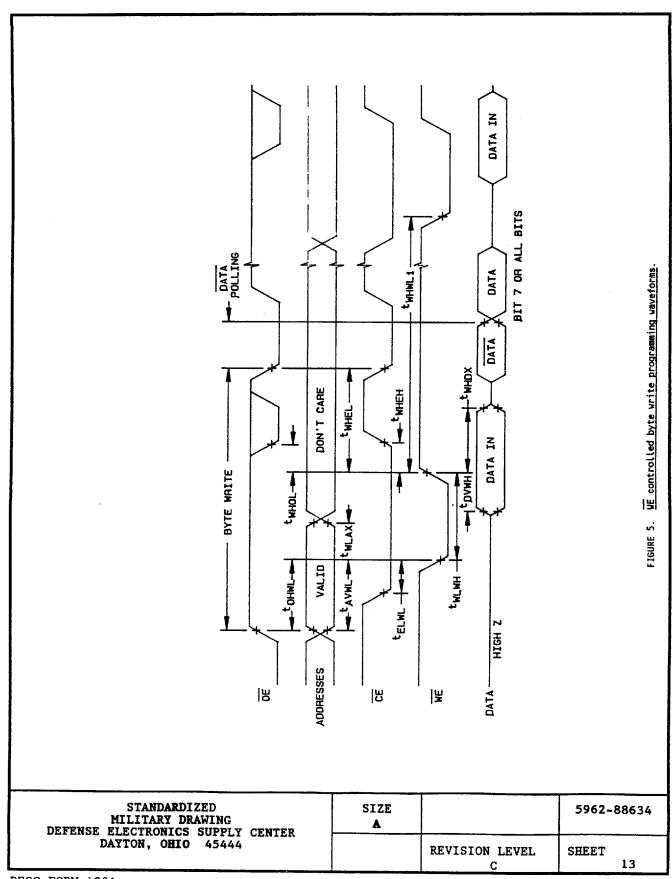

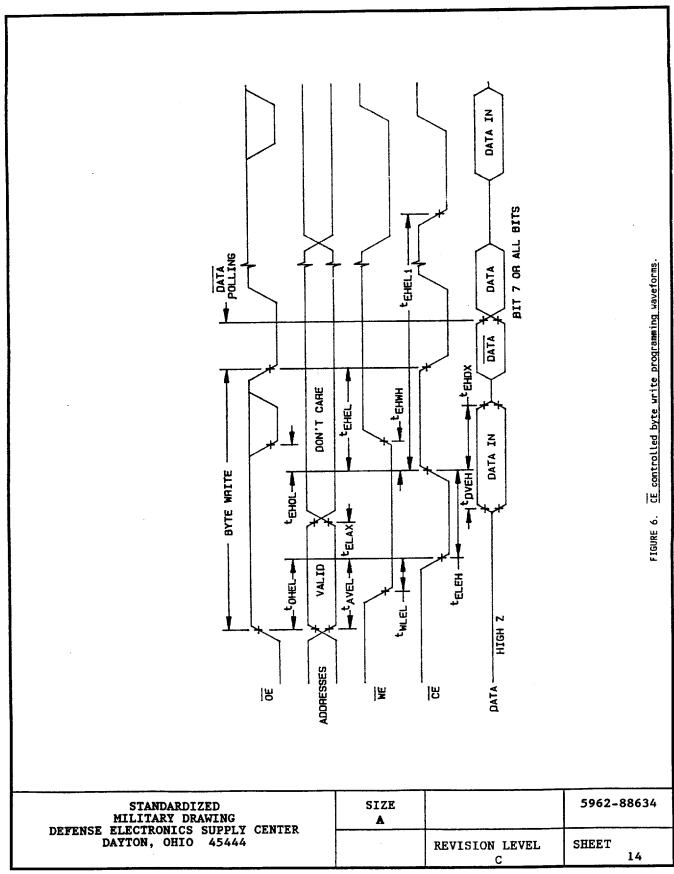

- 4.4.2 <u>Programming procedure</u>. The programming procedures shall be as specified by the device manufacturer. The waveforms and timing relationships shown on figures 4, 5, and 6 and the conditions specified in table I shall be adhered to. Functionality shall be verified at all temperatures (group A, subgroups 7 and 8) by programming all bytes of each device and verifying the pattern used (see 3.10.2).

- 4.4.2.1 <u>Byte write operation</u>. Information is introduced by selectively programming "L" (logic "O" level) or "H" (logic "1" level) into the desired bit locations. A programmed "L" can be changed to an "H" by programming an "H". No erasure is necessary (see 4.4.3).

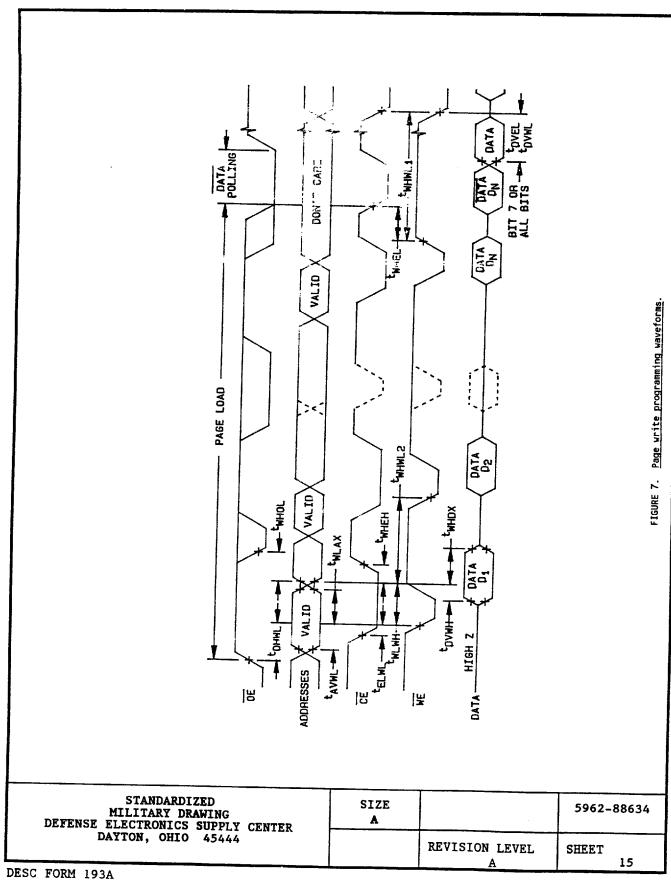

- 4.4.2.2 <u>Page write operation</u>. The page write operation of the device allows 2 to 64 bytes of data to be loaded into the device and then simultaneously <u>written during</u> the internal programming period. Each new <u>by</u>te to <u>be</u> written must have its high to low transition on WE (or CE) within 100  $\mu$ s of the low to high transition of WE (or CE) of the preceding byte. If a high to low transition is not detected within 100  $\mu$ s of the low to high transition, the load period will end and the internal programming period will start.

- 4.4.2.3 <u>Data polling operation</u>. During the internal programming cycle after a byte or page write operation, an attempt to read the last byte written will produce the complement of that data on all I/O or I/O<sub>7</sub> (i.e., write data 0xxx xxxx and read data 1xxx xxx). Once the programming cycle has completed, all I/O or I/O<sub>7</sub> will reflect true data (i.e., write data 0xxx xxx, read data 0xxx xxx).

- 4.4.2.4 <u>Toggle bit</u>. In addition to DATA polling, another method for determining the end of a write cycle can be accomplished during a write operation, successive attempts to read data from the device will result in I/O<sub>6</sub> toggling between one and zero. Once the write has completed, I/O<sub>6</sub> will stop toggling and valid data will be read. Examining the toggle bit may begin at any time during the write cycle.

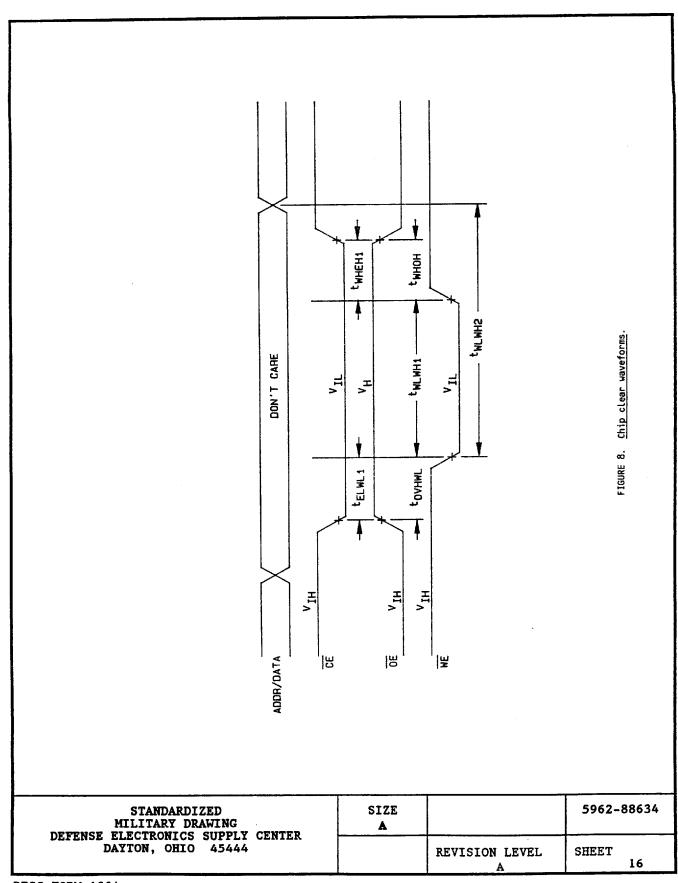

- 4.4.3 <u>Erasing procedure</u>. There are two forms of erasure, chip and byte, whereby all bits or the address selected will be erased to a TTL high (see 3.10.1).

- a. Chip erase is performed in accordance with the waveforms, timing relationships, and instructions shown on figure 8 and the conditions specified in table I.

- b. Byte erase is performed in accordance with the waveforms and timing relationships shown on figures 4, 5, and 6 and the conditions specified in table I.

- 4.4.4 Read mode operation. The waveforms and timing relationships shown on figure 4 and the conditions specified in table I shall be applied when reading the device. Pattern verification utilizes the read mode (see 3.10.3).

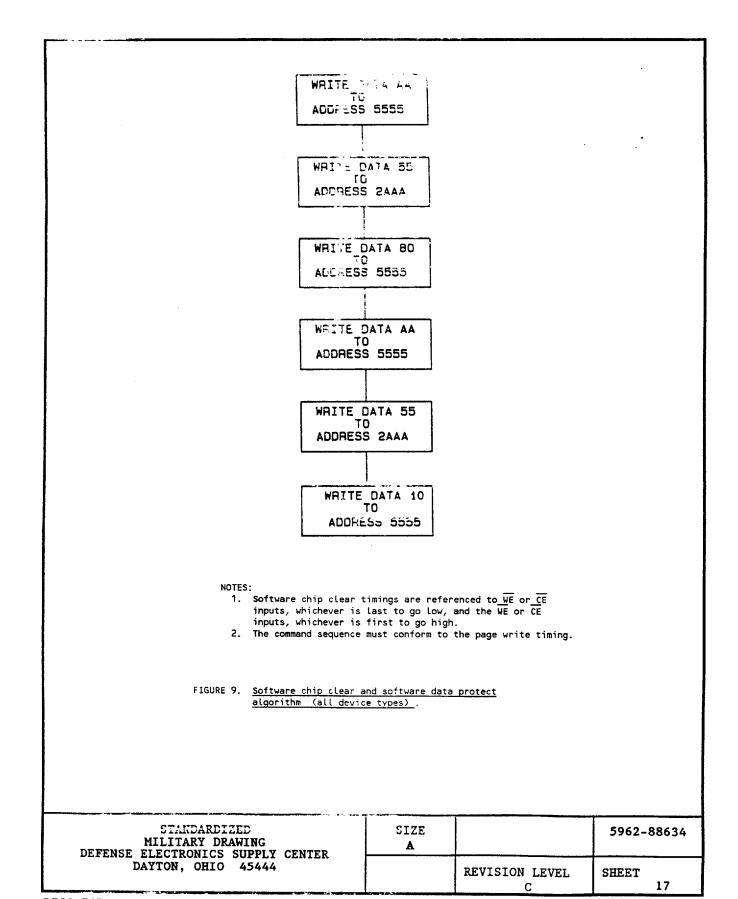

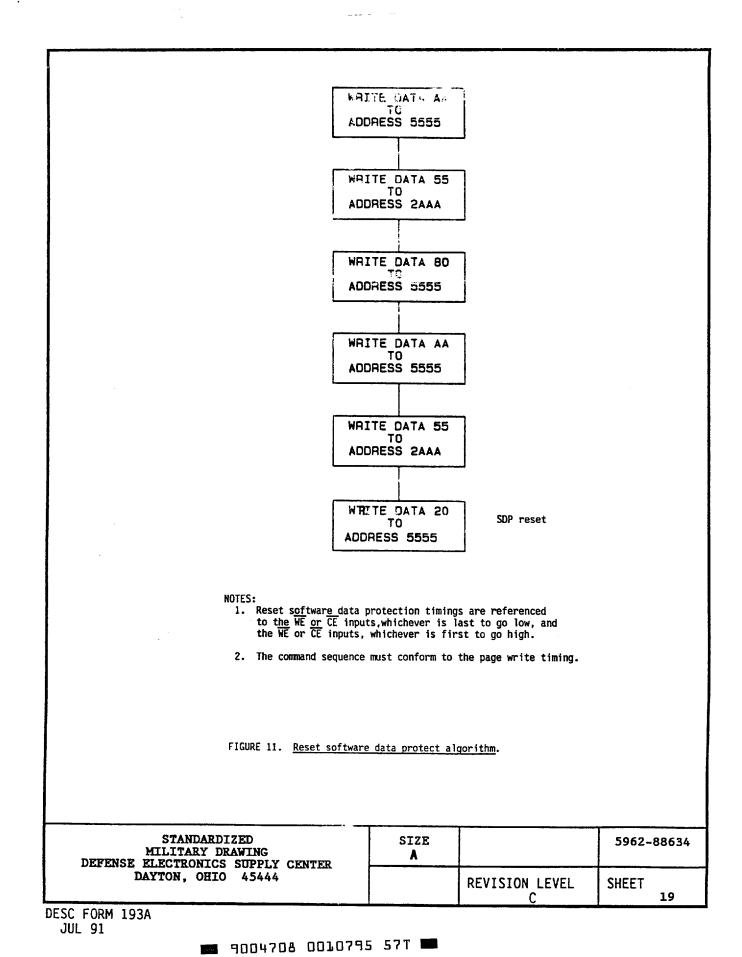

- 4.4.5 <u>Software data protection</u>. Device types 01-05 software data protection offers a method of preventing inadvertent writes (see figure 9). The instructions, waveforms, and timing relationships shown on figures 4, 5, 6, 7, 10, and 11, and the conditions specified in table I shall apply (see 3.10.2).

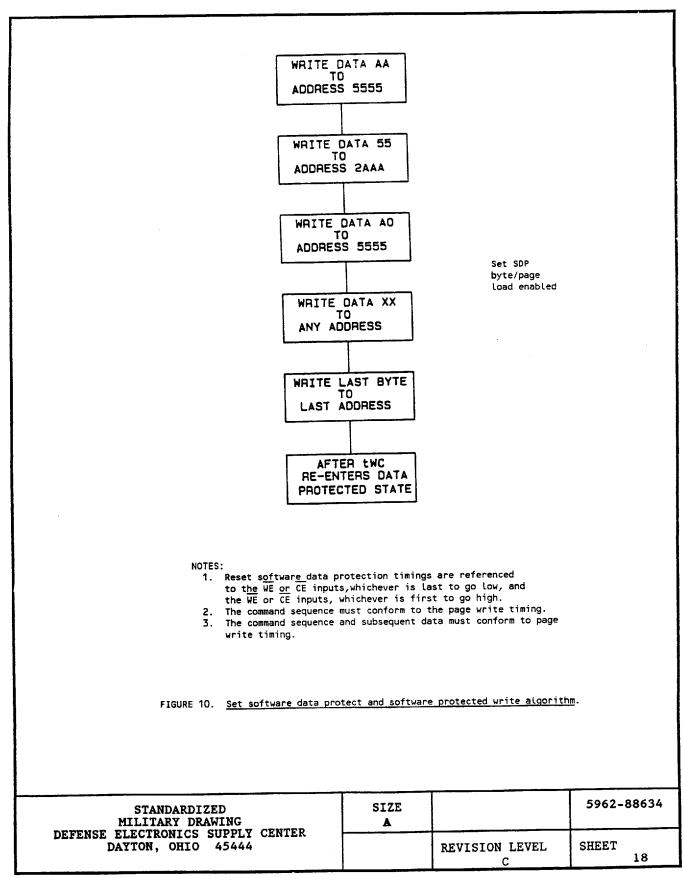

- 4.4.5.1 <u>Set software data protection</u>. Device types 01-05 are placed in protected state by writing a series of instructions (see figure 10) to the device. Once protected, writing to the device may only be performed by executing the same sequence of instructions appended with either a byte write operation or page write operation. The waveforms and timing relationships shown on figures 5, 6, and 7 and the test conditions and limits specified in table I shall apply.

- 4.4.5.2 <u>Reset software data protection</u>. Device types 01-05 protection feature is reset by writing a series of instructions (see figure 11) to the device. The waveforms and timing relationships shown on figures 5, 6, and 7 and the test conditions and limits specified in table I shall apply.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                     | 5962-88634  |

|------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>C | SHEET<br>22 |

**9004708 0010798 289**

TABLE II. Electrical test requirements. 1/2/3/4/5/

| MIL-STD-683 test requirements                                | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters (method 5004)                  | 1, 7, 9, or<br>2, 8(+125°C), 10            |

| Final electrical test parameters (mothod 5004)               | 1*, 2, 3, 7*, 8,<br>9, 10, 11              |

| Group A test requirements Gmethod 5005:                      | 1, 2, 3, 4**, 7,<br>8, 9, 10, 11           |

| Groups C and D end-point electrical parameters (method 5005) | 1, 2, 3, 7, 8,<br>9, 10, 11                |

- $\frac{1}{2}$ / (4) indicates PDA upplies to subgroups 1 and 7.  $\frac{1}{2}$ / Any or all subgroups may be combined when using multifunction testers.

- $\frac{3}{2}$ / Subgroups 7 and 8 shall consist of writing and reading the data pattern specified in accordance with the limits of table I, subgroups 9, 10, and 11.

- 4/ For all electrical tests, the device shall be programmed to the data pattern specified.

- 5/ (\*\*) Indicates that subgroup 4 will only be performed during initial testing and after design or process changes (see 4.3.1c).

## 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

### 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for original equipment manufacturer application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.4 Record of users. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.5 Comments. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444, or telephone (513) 296-5377.

- 6.6 Approved sources of supply. Approved sources of supply are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-EC.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-88634  |

|-----------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>C | SHEET<br>23 |

DESC FORM 193A JUL 91

9004708 0010799 115