# QS7785CF/QS7785PF

QSound Multi-Speaker System

Device Specifications - Preliminary Information

#### Overview:

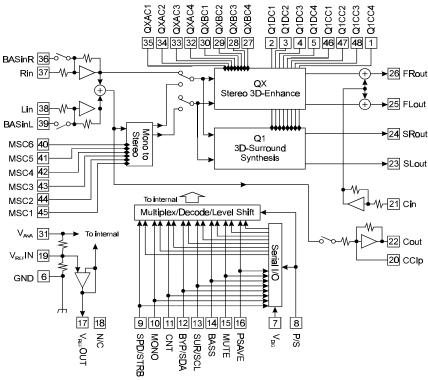

The QS7785 is a 3D audio processor IC that creates 5 speaker surround sounds from 2 channel stereo source using QSurround<sup>TM</sup> technology developed and licensed by QSound Labs, Inc. This chip synthesizes and outputs surround sounds from 2 channel stereo signal for surround speakers as well as an enhanced stereo sound for front speakers.

#### Feature:

- 3D synthesized surround sound for left and right surround speakers

- 3D stereo sound enhancement for left and right front speakers

- Center speaker output

- Parallel and serial digital interface for mode control

- QS7785CF for I<sup>2</sup>C 2 control pins serial interface

- QS7785PF for 3 control pins serial interface (Data, Clock and Strobe)

- DC 5 to 13 volt supply

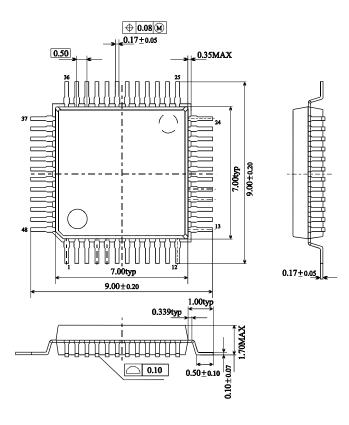

- 48-pin QFP packaging

#### **Application:**

- Audio systems including TV, AV amps, DVD, VCD, SVCD and VCR

- Resynthesis of multi-speaker output from down-mixed surround source. (DVD etc)

- Car audio

- Computer-based multimedia products, including sound cards, powered loud speakers

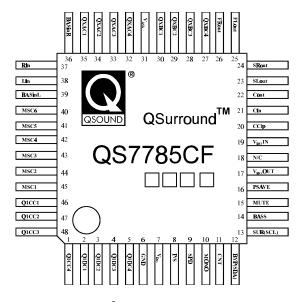

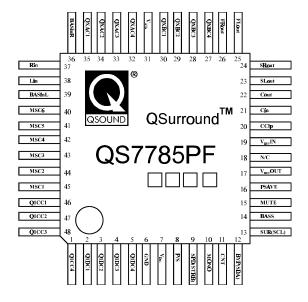

#### **Pin Configuration:**

I<sup>2</sup>C Serial Interface

3 Controls Serial Interface

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 1 of 10   |

# **Packaging Dimension:**

#### IC Block Diagram:

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 2 of 10   |

# QS7785CF/QS7785PF QSound Multi-Speaker System

Device Specifications - Preliminary Information

#### **Pin Functions:**

| Number | Name                 |        | I/O                 | Description                                                               |   |                                                             |

|--------|----------------------|--------|---------------------|---------------------------------------------------------------------------|---|-------------------------------------------------------------|

|        | Parallel             | Serial |                     | ·                                                                         |   |                                                             |

| 1      | Q1CC4                |        | 0                   | Capacitor                                                                 |   |                                                             |

| 2      | Q1DC1                |        | I                   | Capacitor                                                                 |   |                                                             |

| 3      | Q1DC2                |        | I                   | Capacitor                                                                 |   |                                                             |

| 4      | Q1DC3                |        | I                   | Capacitor                                                                 |   |                                                             |

| 5      | Q1DC4                |        | I                   | Capacitor                                                                 |   |                                                             |

| 6      | GND                  |        | -                   | Ground                                                                    |   |                                                             |

| 7      | $V_{\mathrm{DIG}}$   |        | -                   | Digital power supply                                                      |   |                                                             |

| 8      | P/S                  |        | I                   | Interface mode control (H: parallel I/O, L: serial I/O)                   |   |                                                             |

| 9      | SPD                  |        | I                   | Front enhancementcontrol (H: high spread, L: low spread)                  |   |                                                             |

|        |                      | STRB   | I                   | Serial data strobe(Not applicable to I <sup>2</sup> C of QS7785CF)        |   |                                                             |

| 10     | MONO                 |        | I                   | Monaural to virtual stereo control (See operating mode for detail)        |   |                                                             |

| 11     | CNT                  |        | I                   | Center output control (H: center on, L: center off)                       |   |                                                             |

| 12     | BYP                  |        | I                   | Bypass control (See operating mode for detail)                            |   |                                                             |

|        |                      | SDA    | I/O                 | Serial data input (also ACK data output for I <sup>2</sup> C of QS7785CF) |   |                                                             |

| 13     | SUR                  |        | I                   | Surround output control (See operating mode for detail)                   |   |                                                             |

|        |                      | SCL    | I                   | Serial data shift clock                                                   |   |                                                             |

| 14     | BASS                 |        | I                   | Bass boost control (H: on, L: off)                                        |   |                                                             |

| 15     | MUTE                 |        | I                   | Output mute control (H: mute on, L: mute off)                             |   |                                                             |

| 16     | PSAVE                |        | I                   | Power save control (H: power save on, L: power save off)                  |   |                                                             |

| 17     | V <sub>REF</sub> OUT |        | 0                   | Buffered reference voltage (V <sub>ANA</sub> /2)                          |   |                                                             |

| 18     |                      |        | N/C (Not used)      |                                                                           | - | -                                                           |

| 19     |                      |        | V <sub>REF</sub> IN |                                                                           | - | Signal reference input (Self biased to V <sub>ANA</sub> /2) |

| 20     | CClp                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 21     | CIN                  |        | I                   | Center signal input to mix with front signal                              |   |                                                             |

| 22     | COUT                 |        | О                   | Center signal output                                                      |   |                                                             |

| 23     | SLOUT                |        | О                   | Surround left signal output                                               |   |                                                             |

| 24     | SROUT                |        | О                   | Surround right signal output                                              |   |                                                             |

| 25     | FLOUT                |        | 0                   | Front left signal output                                                  |   |                                                             |

| 26     | FROUT                |        | 0                   | Front right signal output                                                 |   |                                                             |

| 27     | QXBC4                |        | I                   | Capacitor                                                                 |   |                                                             |

| 28     | QXBC3                |        | I                   | Capacitor                                                                 |   |                                                             |

| 29     | QXBC2                |        | I                   | Capacitor                                                                 |   |                                                             |

| 30     | QXBC1                |        | I                   | Capacitor                                                                 |   |                                                             |

| 31     | $V_{ANA}$            |        | -                   | Analog power supply                                                       |   |                                                             |

| 32     | QXAC4                |        | I                   | Capacitor                                                                 |   |                                                             |

| 33     | QXAC3                |        | I                   | Capacitor                                                                 |   |                                                             |

| 34     | QXAC2                |        | I                   | Capacitor                                                                 |   |                                                             |

| 35     | QXAC1                |        | I                   | Capacitor                                                                 |   |                                                             |

| 36     | BASinR               |        | I                   | Auxiliary right input for the bass boost (Enabled on BASS = H)            |   |                                                             |

| 37     | RIN                  |        | I                   | Right channel signal input                                                |   |                                                             |

| 38     | LIN                  |        | I                   | Left channel signal input                                                 |   |                                                             |

| 39     | BASinL               |        | I                   | Auxiliary left input for the bass boost (Enabled on BASS = H)             |   |                                                             |

| 40     | MSC6                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 41     | MSC5                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 42     | MSC4                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 43     | MSC3                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 44     | MSC2                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 45     | MSC1                 |        | I                   | Capacitor                                                                 |   |                                                             |

| 46     | Q1CC1                |        | I                   | Capacitor                                                                 |   |                                                             |

| 47     | Q1CC2                |        | I                   | Capacitor                                                                 |   |                                                             |

| 48     | Q1CC3                |        | I                   | Capacitor                                                                 |   |                                                             |

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 3 of 10   |

### **Electrical Specification:**

**Absolute Maximum Ratings**

| Parameter                      | Symbol              | Rating                                   | Unit |

|--------------------------------|---------------------|------------------------------------------|------|

| Supply voltage range (analog)  | V <sub>ANA</sub>    | -0.3 to 15, and $V_{ANA} > V_{DIG}$ -0.3 | V    |

| Supply voltage range (digital) | $V_{\mathrm{DIG}}$  | -0.3 to 7                                | V    |

| Input voltage range (analog)   | $V_{IANA}$          | -0.3 to V <sub>ANA</sub> +0.3            | V    |

| Input voltage range (digital)  | $V_{\mathrm{IDIG}}$ | $-0.3$ to $V_{DIG} + 0.3$                | V    |

| Power dissipation              | $P_{\mathrm{D}}$    |                                          | mW   |

| Storage temperature range      | Tstg                | -40 to 125                               | °C   |

| Soldering temperature          | $T_{SLD}$           | 255                                      | °C   |

| Soldering time                 | t <sub>SLD</sub>    | 10                                       | Sec  |

**Recommended Operating Condition**

| Parameter                   | Symbol             | Limits                                         | Unit |

|-----------------------------|--------------------|------------------------------------------------|------|

| Operating voltage (analog)  | $V_{ANA}$          | 5 to 13 and V <sub>ANA</sub> ≥V <sub>DIG</sub> | V    |

| Operating voltage (digital) | $V_{\mathrm{DIG}}$ | 4.5 to 5.5                                     | V    |

| Operating temperature range | $T_{OPR}$          | 0 to 70                                        | °C   |

$(V_{ANA}=9V, V_{DIG}=5V TA=25^{\circ}C \text{ unless otherwise noted})$ **Electrical Chracteristics** Limits/min Limits/typ Limits/max Parameter Symbol Condition  $V_{RMS}$ Input voltage  $V_{IN1}$ L<sub>IN</sub>, R<sub>IN</sub> 20 kΩ Analog input impedance1  $Z_{AIN1}$  $Z_{\underline{AIN2}}$  $C_{IN}$ 10 kΩ Analog input impedance2 Reference voltage out  $V_{REFOUT} \\$  $V_{ANA}/2$ V 2.4 V HIGH level input voltage  $V_{IH}$ 0.5 LOW level input voltage  $V_{IL}$ V  $V_{IN}=V_{CC}$ μΑ HIGH level input current  $I_{IH}$ LOW level input current V<sub>IN</sub>=GND μΑ  $I_{IL}$ SCL width HIGH 4.0 μS t<sub>1</sub> SCL width LOW 4.7 μS  $t_2$ 250 Set-up time, SDA to SCL nS  $t_3$ 5.0 Hold time, SCL to SDA μS  $t_4$ Set-up time, SCL to STRB 250 nS ts. 5.0 STRB width HIGH μS  $t_6$ 4.0 μS Hold time, SDA to SCL  $t_{\text{HD;STA}}$ Set-up time, SCL to SDA 4.0 μS t<sub>SU;STA</sub> 5.0 μS Hold time, SCL to SDA  $t_{HD;DAT}$ 250 Set-up time, SDA to SCL nS tsu;dat 4.0 SCL width HIGH μS  $t_{HIGH}$ 4.7 μS SCL width LOW  $t_{LOW}$ SCL rise time 1000 nS  $t_R$ SCL fall time 300 nS  $t_{\rm F}$ 10 Operating current (analog)  $I_{ANA}$ mA  $I_{DIG}$ 0.3 mΑ Operating current (digital) 0.1 mA Standby current (analog) I<sub>ANASAVE</sub> 0.035 mA Standby current (digital)  $I_{DIGSAVE}$ Signal to Noise Ratio S/N 96 dB 20 20k Hz Frequency Response F FLIN, SPREAD=HIGH, NO CLIPPING 0.025 THDF % **Total Harmonic Distortion Total Harmonic Distortion**  $THD_R$ RLIN, Q1=ON, NO CLIPPING 0.025 %

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 4 of 10   |

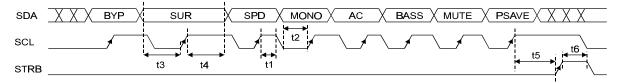

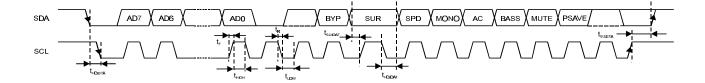

#### **Serial Interface:**

Serial interface with 3 control pins (for QS7785PF)

Serial interface with I<sup>2</sup>C (for QS7785CF)

$I2C \ address \ is \ \{AD7-AD0\} = \{10110110\}$

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 5 of 10   |

## **Operating Mode:**

This chip can be set to desired operating mode by control pins for the parallel interface (P/S pin sets to 1) or control bits for the serial interface (P/S pin sets to 0). The control pins or bits configurations are shown in the following table.

|     | Control 1 | Pins/Bits |     | Output Signal   |                |  |  |

|-----|-----------|-----------|-----|-----------------|----------------|--|--|

| BYP | MONO      | SUR       | SPD | FRout/FLout     | SRout/SLout    |  |  |

| 0   | 0         | 0         | 0   | Stereo QX       | -              |  |  |

| 0   | 0         | 0         | 1   | Stereo QX+      | -              |  |  |

| 0   | 0         | 1         | 0   | Stereo QX       | Stereo Q1      |  |  |

| 0   | 0         | 1         | 1   | Stereo QX+      | Stereo Q1      |  |  |

| 0   | 1         | 0         | 0   | Mono→Stereo QX  | -              |  |  |

| 0   | 1         | 0         | 1   | Mono→Stereo QX+ | -              |  |  |

| 0   | 1         | 1         | 0   | Mono→Stereo QX  | Mono→Stereo Q1 |  |  |

| 0   | 1         | 1         | 1   | Mono→Stereo QX+ | Mono→Stereo Q1 |  |  |

| 1   | 0         | 0         | X   | Stereo Bypass   | -              |  |  |

| 1   | 0         | 1         | X   | Stereo Bypass   | Stereo Bypass  |  |  |

| 1   | 1         | 0         | X   | -               | Stereo Bypass  |  |  |

| 1   | 1         | 1         | X   | Stereo Bypass   | Stereo Q1      |  |  |

|     | Control Pins/Bits |     |     |     | Output Signal |

|-----|-------------------|-----|-----|-----|---------------|

| BYP | MONO              | SUR | SPD | CNT | Cout          |

| X   | X                 | X   | X   | 0   | -             |

| X   | X                 | X   | X   | 1   | (Rin+Lin)/2   |

| Control Pins/Bits |      |     |     |     |      | Output Signal               |                |                |  |  |

|-------------------|------|-----|-----|-----|------|-----------------------------|----------------|----------------|--|--|

| BYP               | MONO | SUR | SPD | CNT | BASS | FRout/FLout SRout/SLout Cou |                |                |  |  |

| X                 | X    | X   | X   | X   | 0    | Bass Boost OFF              | Bass Boost OFF | Bass Boost OFF |  |  |

| X                 | X    | X   | X   | X   | 1    | Bass Boost ON               | Bass Boost ON  | Bass Boost ON  |  |  |

|                                      | Control Pins/Bits |   |   |   |   |   |             |             | Output Signal |           |

|--------------------------------------|-------------------|---|---|---|---|---|-------------|-------------|---------------|-----------|

| BYP MONO SUR SPD CNT BASS MUTE PSAVE |                   |   |   |   |   |   | FRout/FLout | SRout/SLout | Cout          |           |

| X                                    | X                 | X | X | X | X | 0 | 0           | Available   | Available     | Available |

| X                                    | X                 | X | X | X | X | 1 | 0           | -           | -             | -         |

| X                                    | X                 | X | X | X | X | X | 1           | =           | =             | -         |

NOTE-1 '\_' indicates NO OUTPUT.

NOTE-2 QX+ has higher expansion than QX.

NOTE-3 PSAVE = 1 disables chip. Please refer to the electrical specification for its power consumption.

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 6 of 10   |

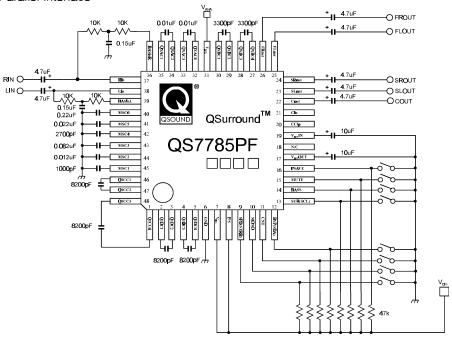

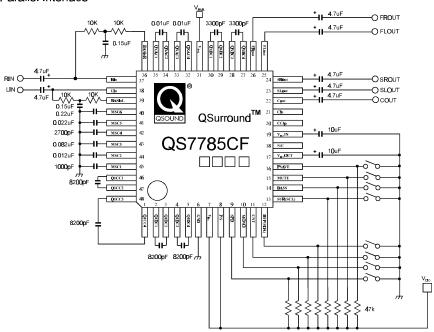

#### **Application (QS7785PF):**

#### Parallel Interface

#### Serial Interface

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 7 of 10   |

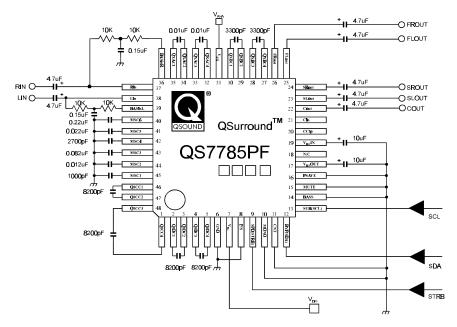

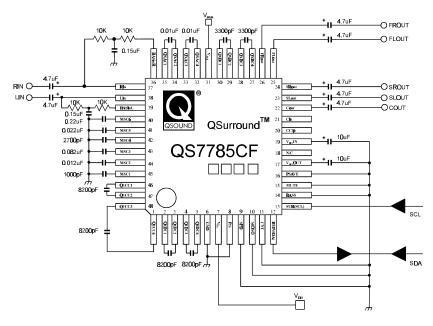

# **Application (QS7785CF):**

#### Parallel Interface

# Serial Interface

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 8 of 10   |

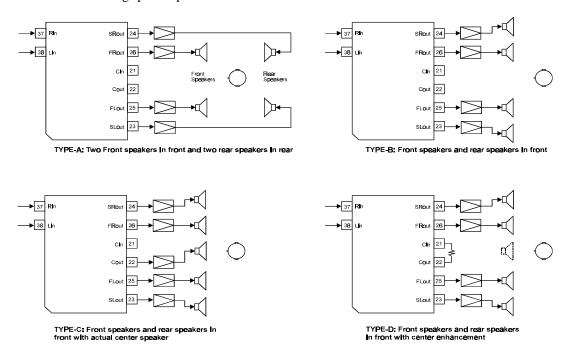

# Speaker configuration:

The QS7785 allows the following speaker position.

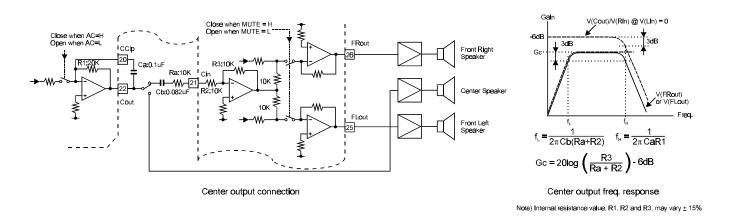

#### **Center control:**

The output level of this device is optimized for the speaker layout TYPE-A, two front speakers in front and two rear speakers in rear, shown above. In case of TYPE-B, having four speakers in front, the surround may sound too rich or the center may sound too thin. In such case, either mixing an auxiliary center output, Cout, to two front speakers, TYPE-D, or driving a center speaker from the Cout, TYPE-C, can enhance the center. It may be good idea to filter only voice band of the center signal to enhance a dialog of movies etc. The Cout becomes available by setting AC control to High.

Ref: QS7785R1.DOCQS7785 Data Sheet -- PreliminaryDate: 06/11/99Rev: 1.00QSound Labs, Inc.Page 9 of 10

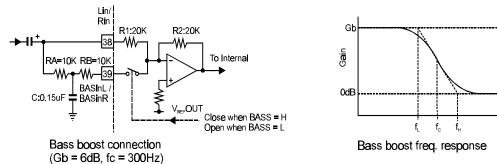

### **Bass boost:**

The signal input of BASinR and BASinL can be used for a bass boosting as shown below. When the BAS control pin is set to H, a low pass filter, consisting of RA, RB and C in the figure below, is connected to the input buffer in parallel to R1.

$Gb = 20\log(1 + \frac{R1}{RA + RB})$ Freq.

Note) Internal resistance value, R1 and R2, may vary ± 15%

| Ref: QS7785R1.DOC | QS7785 Data Sheet Preliminary | Date: 06/11/99 |

|-------------------|-------------------------------|----------------|

| Rev: 1.00         | QSound Labs, Inc.             | Page 10 of 10  |