# CAT27C210/CAT27C210I

# 1 Megabit HIGH SPEED CMOS EPROM

## **FEATURES**

- Fast Read Access Times:

- -150/170/200/250ns (Commercial)

- -170/200/250ns (Industrial)

- Single 5V Supply—Read Mode

- Low Power CMOS Dissipation:

- -Active: 50 mA (Commercial) 60 mA (Industrial)

- -Standby: 100 µA

- High Speed Programming: 100 us/word

- CMOS and TTL Compatible I/O

- 12.5V Programming Level

- JEDEC Standard Pinouts: -40 pin DIP and CERDIP

- -44 pin PLCC

- **■** Electronic Signature

### DESCRIPTION

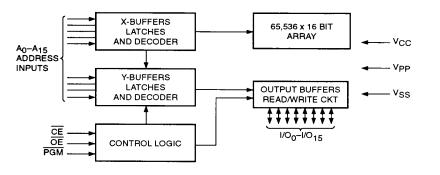

The CAT27C210/CAT27C210I is a high speed low power 64K x 16 bits UV erasable and electronically reprogrammable EPROM ideally suited for high speed applications. Any word can be accessed in less than 150ns making this device compatible with high performance microprocessor systems by eliminating the need for speed-robbing wait states.

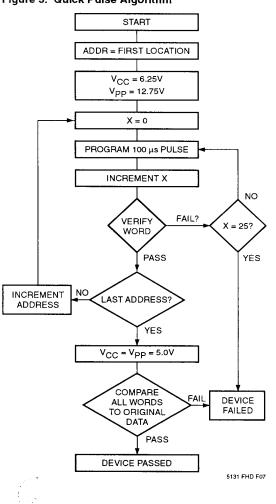

The Quick-Pulse<sup>(1)</sup> programming algorithm reduces the time required to program the chip and ensures more reliable programming. The CAT27C210/CAT27C210I is

used in applications where fast turnaround and pattern experimentation are important requirements.

The CAT27C210/CAT27C210I is manufactured using Catalyst's advanced CMOS floating gate technology. The device is available in JEDEC approved 40 pin DIP and CERDIP and 44 pin PLCC packages. The transparent lid on the 40 pin CERDIP allows the user the option of UV erasing the bit pattern in the device, thus allowing a new pattern to be written in.

# **BLOCK DIAGRAM**

Note:

(1) Quick-Pulse is a trademark of Intel Corporation.

TD 5131

5131 FHD F08

© 1992 by Catalyst Semiconductor, Inc.

9-13

Characteristics subject to change without notice

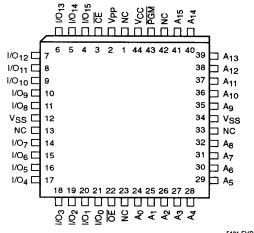

# **PIN CONFIGURATION**

## **DIP and CERDIP Package**

| O                                                                                                              | 1114   | . 01                                | LND    | 11                                                                               | a | chay                                                                                                  |

|----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|--------|----------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------|

| VPP<br>CE<br>I/O15<br>I/O14<br>I/O13<br>I/O12<br>I/O11<br>I/O10<br>I/O9<br>I/O8<br>VSS<br>I/O7<br>I/O6<br>I/O5 |        | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | 0      | 40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>31<br>30<br>29<br>28<br>27 |   | V <sub>CC</sub><br>PGM<br>NC<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>VSS<br>A8<br>A7<br>A6 |

| _                                                                                                              | 밁      | -                                   | _      |                                                                                  | E |                                                                                                       |

| 1/010                                                                                                          | ㅁ      | 8                                   |        | 33                                                                               | Þ | A <sub>11</sub>                                                                                       |

| I/O <sub>9</sub>                                                                                               | $\neg$ | 9                                   |        | 32                                                                               | P | A <sub>10</sub>                                                                                       |

| 1/08                                                                                                           | 口      | 10                                  | $\cap$ | 31                                                                               | 口 | A <sub>9</sub>                                                                                        |

| ٧ss                                                                                                            | ㅁ      | 11                                  |        | 30                                                                               | Þ | $V_{SS}$                                                                                              |

| 1/07                                                                                                           | ㅁ      | 12                                  |        | 29                                                                               | Þ | A <sub>8</sub>                                                                                        |

| 1/06                                                                                                           | ㅁ      | 13                                  |        | 28                                                                               | Þ | A <sub>7</sub>                                                                                        |

| 1/05                                                                                                           | ㅁ      | 14                                  |        | 27                                                                               | Þ | A <sub>6</sub>                                                                                        |

| 1/04                                                                                                           | ㅁ      | 15                                  |        | 26                                                                               | Þ | A <sub>5</sub>                                                                                        |

| 1/03                                                                                                           | d      | 16                                  |        | 25                                                                               | Ь | A4                                                                                                    |

| 1/02                                                                                                           | ᆸ      | 17                                  |        | 24                                                                               | Ь | Аз                                                                                                    |

| 1/01                                                                                                           | ᆸ      | 18                                  |        | 23                                                                               | Ь | Ā2                                                                                                    |

| 1/00                                                                                                           | Ы      | 19                                  |        | 22                                                                               | Ь | A <sub>1</sub>                                                                                        |

| ŌĔ                                                                                                             | 4      | 20                                  |        | 21                                                                               | Þ | A <sub>O</sub>                                                                                        |

|                                                                                                                |        |                                     |        |                                                                                  | - |                                                                                                       |

# **PIN FUNCTIONS**

| A <sub>0</sub> A <sub>15</sub>      | Addresses              |

|-------------------------------------|------------------------|

| I/O <sub>0</sub> –I/O <sub>15</sub> | Data Inputs/Outputs    |

| CE                                  | Chip Enable            |

| ŌĒ                                  | Output Enable          |

| PGM                                 | Write Enable           |

| NC                                  | No Connect             |

| V <sub>PP</sub>                     | Program Supply Voltage |

| Vcc                                 | 5V Supply              |

| Vss                                 | Ground                 |

# **PLCC Package**

5131 FHD F01

# **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias55°C to +125°C                                                   |

|----------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                      |

| Voltage on Any Pin with Respect to Ground <sup>(3)</sup> 2.0V to V <sub>CC</sub> +2.0V |

| Voltage on Pin A <sub>9</sub> with<br>Respect to Ground <sup>(3)</sup> 2.0V to +13.5V  |

| V <sub>PP</sub> with Respect to Ground during Program/Erase2.0V to +14.0V              |

| $V_{CC}$ with Respect to Ground–2.0V to +7.0V                                          |

| Package Power Dissipation Capability (T <sub>A</sub> = 25°C)                           |

| Lead Soldering Temperature (10 secs)300°C                                              |

| Output Short-Circuit Current <sup>(4)</sup> 100 mA                                     |

## \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

## RELIABILITY CHARACTERISTICS

| Symbol                  | Parameter          | Min. | Max. | Units | Test Method                   |

|-------------------------|--------------------|------|------|-------|-------------------------------|

| V <sub>ZAP</sub> (2)    | ESD Susceptibility | 2000 |      | Volts | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> (2)(5) | Latch-Up           | 100  |      | mA    | JEDEC Standard 17             |

# CAPACITANCE $T_A = 25$ °C, f = 1.0 MHz, $V_{CC} = 5$ V

| Symbol                          | Test                               | Max. | Units | Conditions            |  |

|---------------------------------|------------------------------------|------|-------|-----------------------|--|

| C <sub>IN</sub> <sup>(2)</sup>  | Input Capacitance                  | 6    | pF    | V <sub>IN</sub> = OV  |  |

| Cout <sup>(2)</sup>             | Output Pin Capacitance             | 10   | pF    | V <sub>OUT</sub> = 0V |  |

| CV <sub>PP</sub> <sup>(2)</sup> | V <sub>PP</sub> Supply Capacitance | 25   | pF    | V <sub>PP</sub> = 0V  |  |

- (2) This parameter is tested initially and after a design or process change.

- (3) The minimum DC input voltage is -0.5. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> + 0.5V, which may overshoot to V<sub>CC</sub> + 2.0V for periods of less than 20 ns.

- (4) Output shorted for no more than one second. No more than one output shorted at a time.

- (5) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to  $V_{CC} + 1V$ .

# D.C. OPERATING CHARACTERISTICS, Read Operation

CAT27C210 T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = +5V  $\pm$ 10%, unless otherwise specified. CAT27C210I T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = +5V  $\pm$ 10%, unless otherwise specified.

|                     |                                           |      |                       | Limits |                      |       |                                                    |

|---------------------|-------------------------------------------|------|-----------------------|--------|----------------------|-------|----------------------------------------------------|

| Symbol              | Parameter                                 |      | Min.                  | Тур.   | Max.                 | Units | Test Conditions                                    |

| ICC <sup>(6)</sup>  | V <sub>CC</sub> Operating Current (TTL)   | Com. |                       |        | 60<br>70             | mA    | CE = V <sub>IL</sub> , f = 5MHz<br>All I/O's Open  |

| ICCC <sup>(6)</sup> | V <sub>CC</sub> Operating Current (CMOS)  | Com. |                       |        | 50<br>60             | mA    | CE = V <sub>ILC</sub> , f = 5MHz<br>All I/O's Open |

| I <sub>SB1</sub>    | V <sub>CC</sub> Standby Current (TTL)     | Com. |                       |        | 1                    | mA    | CE = V <sub>IL</sub>                               |

| I <sub>SB2</sub>    | V <sub>CC</sub> Standby Current<br>(CMOS) | Com. |                       |        | 100<br>100           | μА    | CE = V <sub>IL</sub>                               |

| ILI                 | Input Leakage Current                     |      |                       |        | 1                    | μА    | V <sub>IN</sub> = 5.5V                             |

| ILO                 | Output Leakage Current                    |      |                       |        | 1                    | μА    | V <sub>OUT</sub> = 5.5V                            |

| I <sub>PP1</sub>    | V <sub>PP</sub> Leakage Current           |      |                       |        | 1                    | μА    | V <sub>PP</sub> = 5.5V                             |

| V <sub>IH</sub>     | Input High Level TTL                      |      | 2.0                   |        | V <sub>CC</sub> +0.5 | V     |                                                    |

| VIL                 | Input Low Level TTL                       |      | -0.5                  |        | 0.8                  | V     |                                                    |

| V <sub>OH</sub>     | Output Voltage High Level                 |      | 2.4                   | 1.5    |                      | ٧     | l <sub>OH</sub> = −1.0 mA                          |

| V <sub>OL</sub>     | Output Voltage Low Level                  |      |                       |        | 0.40                 | V     | I <sub>OL</sub> = 4.0 mA                           |

| V <sub>ILC</sub>    | Input Low Level CMOS                      |      | -0.5                  |        | 0.30                 | V     |                                                    |

| V <sub>IHC</sub>    | Input High Level CMOS                     |      | V <sub>CC</sub> – 0.5 |        | V <sub>CC</sub> +0.5 | V     |                                                    |

<sup>(6)</sup> The maximum current value is with outputs I/O<sub>0</sub> to I/O<sub>15</sub> unloaded.

# A.C. CHARACTERISTICS, Read Operation

CAT27C210 T<sub>A</sub> = 0°C to +70°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified. CAT27C210I T<sub>A</sub> = -40°C to +85°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified.

|                        |                          | 27C210-15 |      | 27C210-17<br>27C210I-17 |      | 27C210-20<br>27C210I-20 |      | 27C210-25<br>27C210I-25 |      |      |  |

|------------------------|--------------------------|-----------|------|-------------------------|------|-------------------------|------|-------------------------|------|------|--|

| Symbol                 | Parameter                | Min       | Max. | Min.                    | Max. | Min.                    | Max. | Min.                    | Max. | Unit |  |

| tacc                   | Address Access Time      |           | 150  |                         | 170  |                         | 200  |                         | 250  | ns   |  |

| tce                    | CE to Output Delay       |           | 150  |                         | 170  |                         | 200  |                         | 250  | ns   |  |

| toE                    | OE to Output Delay       |           | 60   |                         | 70   |                         | 80   |                         | 100  | ns   |  |

| t <sub>OH</sub> (2)(7) | Output Hold A, OE, CE    | 0         |      | 0                       |      | 0                       |      | 0                       |      | ns   |  |

| t <sub>DF</sub> (2)(7) | OE High to High-Z Output | 0         | 35   | 0                       | 40   | 0                       | 50   | 0                       | 60   | ns   |  |

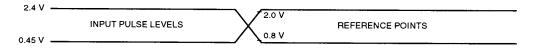

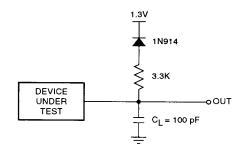

Figure 1. A.C. Testing Input/Output Waveform<sup>(8)</sup>

Figure 2. A.C. Testing Load Circuit (example)

C<sub>L</sub> INCLUDES JIG CAPACITANCE

5129 FHD F03

5131 FHD F02

- (2) This parameter is tested initially and after a design or process change.

- (7) Output floating (High-Z) is defined as the state where the external data line is no longer driven by the output buffer.

- (8) Input rise and fall times (10% to 90%) <10ns.

# D.C. CHARACTERISTICS, Programming Operation

CAT27C210  $T_A = 25^{\circ}C \pm 5^{\circ}C$ CAT27C210I  $T_A = 25^{\circ}C \pm 5^{\circ}C$

|                                    |                                                      |                        | Limits |                       |       |                          |

|------------------------------------|------------------------------------------------------|------------------------|--------|-----------------------|-------|--------------------------|

| Symbol                             | Parameter                                            | Min. Typ.              |        | Max.                  | Units | <b>Test Conditions</b>   |

| V <sub>CC</sub> <sup>(10)</sup>    | Supply Voltage<br>(Quick Pulse Algorithm)            | 6.0                    | 6.25   | 6.5                   | V     |                          |

|                                    | Supply Voltage<br>(Intelligent Algorithm)            | 5.75                   | 6.0    | 6.25                  | V     |                          |

| V <sub>PP</sub> <sup>(9)(10)</sup> | Programming Voltage<br>(Quick Pulse Algorithm)       | 12.5                   | 12.75  | 13.0                  | V     |                          |

|                                    | Programming Voltage<br>(Intelligent Algorithm)       | 12.0                   | 12.5   | 13.0                  | V     |                          |

| ICCP <sup>(6)</sup>                | V <sub>CC</sub> Supply Current<br>Program and Verify |                        |        | 45                    | mA    | CE = V <sub>IL</sub>     |

| 1 <sub>PP</sub> (6)                | V <sub>PP</sub> Supply Current<br>Program Operation  |                        |        | 40                    | mA    | CE = VIL                 |

| ILI                                | Input Leakage Current                                |                        |        | 10                    | μА    | V <sub>IN</sub> = 5.25V  |

| lLO                                | Output Leakage Current                               |                        |        | 10                    | μА    | V <sub>OUT</sub> = 5.25V |

| V <sub>IL</sub>                    | Input Low-Level TTL                                  | -0.50                  |        | 0.80                  | V     |                          |

| VILC                               | Input Low-Level CMOS                                 | -0.50                  |        | 0.30                  | V     |                          |

| VIH                                | Input High-Level TTL                                 | 2.0                    |        | V <sub>CC</sub> + 0.5 | V     |                          |

| V <sub>IHC</sub>                   | Input High-Level CMOS                                | V <sub>CC</sub> - 0.50 |        | V <sub>CC</sub> + 0.5 | V     |                          |

| V <sub>OL</sub>                    | Output Low Voltage (Verify)                          |                        |        | 0.40                  | V     | I <sub>OL</sub> = 2.4 mA |

| VoH                                | Output High Voltage (Verify)                         | 2.4                    |        |                       | V     | $I_{OH} = -400  \mu A$   |

| VH(6)(9)                           | A <sub>9</sub> Signature Mode Voltage                | 11.5                   |        | 12.5                  | V     |                          |

<sup>(6)</sup> The maximum current value is with outputs  $I/O_0$  to  $I/O_{15}$  unloaded.

<sup>(9)</sup> V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

<sup>(10)</sup> When programming, a 0.1 μF capacitor is required across V<sub>PP</sub> and GND to suppress spurious voltage transients which can damage the device.

# A.C. CHARACTERISTICS, Programming Operation

CAT27C210 T<sub>A</sub> = 25°C ±5°C CAT27C210I T<sub>A</sub> = 25°C ±5°C

|                                 |                                                    |      | Limits |      |      |                        |

|---------------------------------|----------------------------------------------------|------|--------|------|------|------------------------|

| Symbol                          | Parameter                                          | Min. | Тур.   | Max. | Unit | <b>Test Conditions</b> |

| tas                             | Address Setup Time                                 | 2    |        |      | μs   |                        |

| toes                            | OE Setup Time                                      | 2    |        |      | μs   |                        |

| t <sub>DS</sub>                 | Data Setup Time                                    | 2    |        |      | μs   |                        |

| t <sub>AH</sub>                 | Address Hold Time                                  | 0    |        |      | μs   |                        |

| t <sub>DH</sub>                 | Data Hold Time                                     | 2    |        |      | μs   | 1,2,0                  |

| tvps <sup>(9)</sup>             | V <sub>PP</sub> Setup Time                         | 2    |        |      | μs   |                        |

| t <sub>VCS</sub> <sup>(9)</sup> | V <sub>CC</sub> Setup Time                         | 2    |        |      | μѕ   |                        |

| t <sub>PW</sub>                 | CE Program Pulse Width<br>(Quick Pulse Algorithm)  | 95   | 100    | 105  | μs   | _                      |

| tpw                             | CE Program Pulse Width<br>(Intelligent Algorithm)  | 0.95 | 1.0    | 1.05 | ms   |                        |

| topw                            | CE Overprogram Pulse Width (Intelligent Algorithm) | 2.85 |        | 78.5 | ms   |                        |

| t <sub>DFP</sub> (2)(7)         | OE High to Output High-Z                           | 0    |        | 130  | ns   |                        |

| toE                             | Data Valid from OE                                 |      |        | 150  | ns   |                        |

- (2) This parameter is tested initially and after a design or process change.

- (7) Output floating (High-Z) is defined as the state where the external data line is no longer driven by the output buffer.

- (9) V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

# **FUNCTION TABLE**

|                  | Pins            |                 |                 |                 |                 |                |                  |  |  |  |

|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|------------------|--|--|--|

| Mode             | CE              | ŌĒ              | V <sub>PP</sub> | PGM             | Ao              | A <sub>9</sub> | I/O              |  |  |  |

| Read             | V <sub>IL</sub> | VIL             | Vcc             | Х               | Х               | Х              | Dout             |  |  |  |

| Output Disable   | VIL             | V <sub>IH</sub> | Vcc             | Х               | Х               | Х              | High-Z           |  |  |  |

| Standby          | ViH             | Х               | Vcc             | Х               | Х               | Х              | High-Z           |  |  |  |

| Program          | VIL             | V <sub>IH</sub> | V <sub>PP</sub> | VIL             | Х               | Х              | DIN              |  |  |  |

| Program Verify   | V <sub>IL</sub> | VIL             | V <sub>PP</sub> | V <sub>IH</sub> | Х               | Х              | D <sub>OUT</sub> |  |  |  |

| Program Inhibit  | V <sub>IH</sub> | Х               | V <sub>PP</sub> | Х               | Х               | Х              | High-Z           |  |  |  |

| Signature MFG.   | VIL             | V <sub>IL</sub> | Vcc             | Х               | V <sub>IL</sub> | VH             | 0031H            |  |  |  |

| Signature Device | VIL             | V <sub>IL</sub> | Vcc             | Х               | ViH             | V <sub>H</sub> | 0007H            |  |  |  |

## NOTES ON THE FUNCTION TABLE

Logic Levels:  $V_{1H} = TTL \text{ Logic 1 level}$  $V_{1L} = TTL \text{ Logic 0 level}$

X = Logic "Do not care," VIH or VIL

Supply Voltage:  $V_{PP} = Programming/High-Voltage$

V<sub>CC</sub> = Read/Low-Voltage

$V_H = 12.0V \pm 0.5V$

Read: Read Mode: The content of the addressed memory word is placed on the I/O pins I/O<sub>0</sub> to I/O<sub>15</sub>.

Output Disable: Device is selected (active mode), programming is disabled and I/O<sub>0</sub> to I/O<sub>15</sub> output buffers are tristated (PMOS and NMOS drivers turned-off).

Standby: Device is deselected, low power dissipation.

Program: Word Programming Mode: Logic zeros in the bit pattern driving the I/O<sub>0</sub> to I/O<sub>15</sub> data input

buffers are written into the respective memory cells of the addressed word.

Program Verify: Following a programming cycle, to verify the cell contents of the memory word being

programmed (not recommended as a normal read operation).

Program Inhibit: CE set to logic one prevents programming and deselects the device.

Signature MFG: Signature mode with all other addresses at V<sub>IL</sub>, code of IC manufacturer (Catalyst) output

on I/O pins I/O<sub>0</sub> to I/O<sub>15</sub>.

Signature Device: Signature mode with all other addresses at V<sub>IL</sub>, code of IC type output on I/O pins I/O<sub>0</sub> to I/O<sub>15</sub>.

## **DEVICE OPERATION**

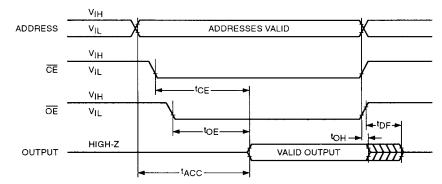

# Read Operation and Standby Modes

Memory access for reading an address location is controlled by  $\overline{CE}$  and  $\overline{OE}$ . Chip enable  $\overline{CE}$  is used independently of all other input signals as the primary device selection. In the logic zero state (TTL level  $V_{IL}$ ),  $\overline{CE}$  powers up all inputs and enables internal circuitry. In the logic one state (CMOS level  $V_{IHC}$ )  $\overline{CE}$  places the device in standby mode, all DC paths to ground are shut-off, and the power dissipation is reduced to a minimum. A logic one on Output Enable  $\overline{OE}$  disables the output buffers and places the output pads in a high impedance state. Assuming that the address lines  $A_0$  to  $A_{15}$  have been stable for a time equal to  $t_{ACC}-t_{OE}$ , the output data is available after a delay of  $t_{OE}$  from the falling edge of  $\overline{OE}$ .

## Signature Mode

The Signature Mode allows one to identify the IC manufacturer and the device type. This mode is entered as a regular Read Mode by driving the  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  inputs low, and additionally driving the A<sub>9</sub> pin to high-voltage (V<sub>H</sub>) with all other address lines at V<sub>IL</sub>.

Driving  $A_0$  to  $V_{IL}$  with all other addresses at  $V_{IL}$ , gives the the binary code of the IC manufacturer on outputs I/O<sub>0</sub> to I/O<sub>15</sub>.

CATALYST Code: 0 0 0 0 0 0 0 0 1 1 0 0 0 1 (0031H)

Driving  $A_0$  to  $V_{IH}$  with all other addresses at  $V_{IL}$ , gives the the binary code of the device type on outputs  $I/O_0$  to  $I/O_{15}$ .

27C210/27C210l Code: 0 0 0 0 0 0 0 0 1 1 1 (0007H)

Figure 3. Read Operation Timing

5129 FHD F04

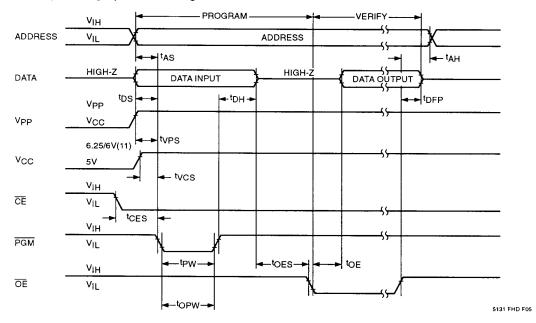

# **Programming Mode**

As shipped, all the bits of the CAT27C210/CAT27C210I are in the logic "1" state. The device is programmed by selectively writing logic "0"s into the desired bit locations. To enter the programming mode, V<sub>CC</sub> and V<sub>PP</sub> must be adjusted to their programming levels,  $\overline{\text{CE}}$  pulled to V<sub>IL</sub>, and a program write pulse applied to the  $\overline{\text{PGM}}$  pin. After

the program write pulse, the programmed data may then be verified by enabling the outputs ( $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ , and  $\overline{PGM} = V_{IH}$ ), then comparing the written data to the read data. This device is compatible with Intelligent<sup>TM</sup> (12) and the Quick-Pulse Programming<sup>TM</sup> algorithms.

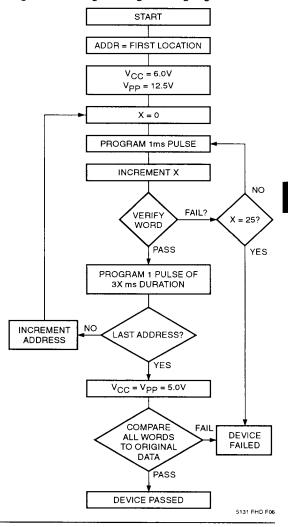

The flow charts for both the algorithms are given in Figures 5 and 6.

Figure 4. Programming Operation Timing

Note:

(12) Intelligent is a trademark of Intel Corporation.

<sup>(11)</sup> V<sub>CC</sub> = 6.25V ±0.25V for Quick Pulse algorithm; 6.0V ±0.25V for Intelligent Programming algorithm.

# U.V. ERASURE OPERATION FOR CERDIP EPROMS

Direct exposure to fluorescent lamps such as those used in room light fixtures, can erase the CAT27C210/CAT27C210I EPROM in less than three years. When exposed to direct sun light the EPROM can be erased in less than a week.

The recommended erasure procedure is to expose the CAT27C210/CAT27C210I EPROM to a standard ultraviolet light with a wavelength of 2537 Angstroms. The integrated dose for proper erasure is 15 Wsec/cm<sup>2</sup>. The

erasure time with this dosage is approximately 15 to 60 minutes using an ultraviolet lamp with a 1200  $\mu$ W/cm<sup>2</sup> power rating. The EPROM should be placed within 1 inch of the lamp tubes.

The maximum integrated dose a CAT27C210/CAT27C210I EPROM can be exposed to is 7258 Wsec/cm² (one week at 1200 uW/cm²). Exposure of the device to higher U.V. doses may cause permanent damage and loss of functionality.

Figure 5. Quick Pulse Algorithm

Figure 6. Intelligent Programming Algorithm