#### 2048 BIT BIPOLAR TTL

#### PROGRAMMABLE READ ONLY MEMORY

#### **Description**

The  $\mu$ PB421C and  $\mu$ PB421D are high speed, electrically programmable, fully decoded 2048 bit TTL read only memories. On-chip address decoding, two chip select inputs and three-state outputs allow easy expansion of memory capability. The  $\mu$ PB421C and  $\mu$ PB421D are fabricated with logic level zero (low); logic level one High) can be electrically programmed into the selected bit locations. The same address inputs are used for both programming and reading.

#### **Features**

256 WORDS x 8 BITS organization (Fully decoded)

TTL Interface

● Fast read access time : 40 ns MAX. (µPB421-1)

Medium power consumption : 500 mW TYP.

Two chip select inputs for memory expansion

Three-state outputs

Cerdip 20-Lead Dual In-Line Package (μPB421D)

Plastic 20-Lead Dual In-Line Package (μPB421C)

Plastic 20-Lead Dual in-Line Package (µPB421C

Fast programming time : 200 µs/bit TYP.

Compatibility with : MMI's 6309 and equivalent devices (as a

ROM)

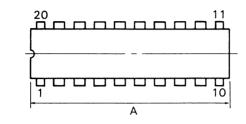

#### **Connection Diagram (Top View)**

| A0    | 1<br>2<br>3<br>4<br>5<br>6<br>7 | 20<br>19<br>18<br>17<br>16<br>15 | VCC A7 A6 A5 CS2 CS1 08 |

|-------|---------------------------------|----------------------------------|-------------------------|

|       | _                               |                                  |                         |

| 03 □  | 8                               | 13                               | <b>□</b> 07             |

| 04 🗆  | 9                               | 12                               | □ 06                    |

| GND 🗀 | 10                              | 11                               | □ 05                    |

A0 to A7 : Address Inputs 01 to 08 : Data Outputs

CS<sub>1</sub>, CS<sub>2</sub>: Chip Select Inputs (Active Low)

VCC : Power Supply (+5V)

GND : Ground

#### Operation

#### 1. Programming

A logic one can be permanently programmed into a selected bit location by using special equipment (programmer). First, the desired word is selected by the eight address inputs in TTL levels. Either or both of the Chip Select inputs should be at a logical one. Secondly, a train of high current programming pulses is applied to the desired output. After the sensed voltage indicates that the selected bit is in the logic one state, an additional pulse train is applied, then is stopped.

#### 2. Reading

To read the memory, both of the two Chip Select inputs must be held at a logical zero. The outputs then correspond to the data programmed in the selected words. When either or both of the two Chip Select inputs are at a logical one, all the outputs will be high (floating).

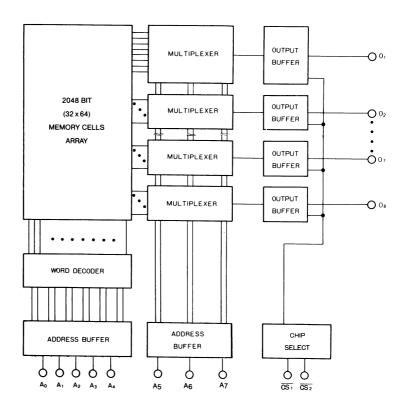

#### **Logic Diagram**

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                        | Vcc       | -0.5  to  +7.0 | V  |

|---------------------------------------|-----------|----------------|----|

| Input Voltage                         | Vi        | -0.5 to $+5.5$ | ٧  |

| Output Voltage                        | Vo        | -0.5  to  +5.5 | ٧  |

| Output Current                        | lo        | 50             | mΑ |

| Operating Temperature                 | $T_{opt}$ | -25  to  +75   | .c |

| Storage Temperature (Cerdip Package)  | $T_{stg}$ | -65  to  +150  | °C |

| Storage Temperature (Plastic Package) | $T_{stg}$ | -55 to $+125$  | °C |

## D.C. CHARACTERISTICS ( $V_{CC}$ =4.5 to 5.5 V, $T_a$ =0 to +75 °C)

| CHARACTERISTIC               | SYMBOL             | MIN. | TYP. | MAX. | UNIT | TEST CONDIT             | IONS                     |

|------------------------------|--------------------|------|------|------|------|-------------------------|--------------------------|

| Input High Voltage           | ViH                | 2.0  |      |      | V    |                         |                          |

| Input Low Voltage            | VIL                |      |      | 0.85 | V    |                         |                          |

| Input High Current           | i <sub>IH</sub>    |      |      | 40   | μА   | V <sub>I</sub> = 5.5 V  | $V_{CC} = 5.5 \text{ V}$ |

| Input Low Current            | - I <sub>IL</sub>  |      |      | 0.25 | mA   | V <sub>I</sub> = 0.4 V  | $V_{CC} = 5.5 V$         |

| Output Low Voltage           | VoL                |      |      | 0.45 | V    | $I_0 = 16 \text{ mA}$   | $V_{CC} = 4.5 \text{ V}$ |

| Output Leakage Current       | loffi              |      |      | 40   | μΑ   | V <sub>0</sub> = 5.5 V  | $V_{CC} = 5.5 \text{ V}$ |

| Output Leakage Current       | -1 <sub>0FF2</sub> |      |      | 40   | μА   | V <sub>0</sub> = 0.4 V  | V <sub>CC</sub> =5.5 V   |

| Input Clamp Voltage          | - Vic              |      |      | 1.2  | V    | $I_1 = -18 \text{ mA}$  | $V_{CC} = 4.5 \text{ V}$ |

| Power Supply Current         | lcc                |      | 90   | 140  | mA   | All Inputs Grounded.    | $V_{CC} = 5.5 \text{ V}$ |

| Output High Voltage          | VoH                | 2.4  |      |      | V    | $I_0 = -2.4 \text{ mA}$ | $V_{CC} = 4.5 \text{ V}$ |

| Output Short Circuit Current | -1 sc              | 15   |      | 60   | mA   | V <sub>0</sub> =0 V     |                          |

## CAPACITANCE (V<sub>CC</sub>=5 V, f=1 MHz, T<sub>a</sub>=25 °C)

| CHARACTERISTIC     | SYMB0L | MIN. | MAX. | UNIT | TEST CONDITIONS          |

|--------------------|--------|------|------|------|--------------------------|

| Input Capacitance  | CIN    |      | 8    | pF   | V <sub>IN</sub> =2.5 V   |

| Output Capacitance | Соит   |      | 10   | pF   | V <sub>OUT</sub> = 2.5 V |

## A.C. CHARACTERISTICS (VCC=4.5 to 5.5 V, Ta=0 to +75°C)

| Ol saladatia             | Symbol | μPB421C/D-1 |      | μPB421C/D |      | Unit  |

|--------------------------|--------|-------------|------|-----------|------|-------|

| Characteristic           |        | min.        | max. | min.      | max. | 0,,,, |

| Address Access Time      | tAA    |             | 40   |           | 50   | ns    |

| Chip Select Access Time  | tACS   |             | 30   |           | 30   | ns    |

| Chip Select Disable Time | tDCS   |             | 30   |           | 30   | ns    |

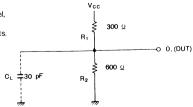

Note 1. Output Load: See Fig. 1.

Note 2. Input Waveform: 0.0 V for low level and 3.0 V for high level, less than 10 ns for both rise and fall times.

Note 3. Measurement References: 1.5 V for both inputs and outputs.

Note 4. C<sub>L</sub> in Fig. 1 includes jig and probe stray capacitances.

# Programming Specification

It is imperative that this specification be rigorously observed in order to correctly program the  $\mu PB421C$  and  $\mu PB421D$ . NEC will not accept responsibilty for any device found to be defective if it were not programmed according to this specification.

| CHARACTERISTIC.                                                             | LIMIT         | UNIT | NOTES                 |

|-----------------------------------------------------------------------------|---------------|------|-----------------------|

| Ambient Temperature                                                         | 25 ±5         | °C   |                       |

| Programming Pulse                                                           |               |      |                       |

| Amplitude                                                                   | 200 ± 5 %     | mA   |                       |

| Clamp Voltage                                                               | 28 +0 % -2 %  | ٧    |                       |

| Ramp Rate (Both in Rise and in Fall)                                        | 70 MAX.       | V/μs |                       |

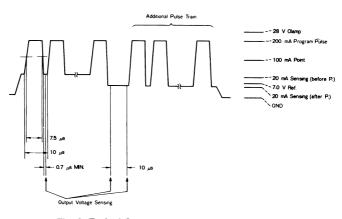

| Pulse Width                                                                 | 7.5 ± 5 %     | μS   | 15 V point/150 Ω load |

| Duty Cycle                                                                  | 70 % MIN.     |      |                       |

| Sense Current                                                               |               |      |                       |

| Amplitude                                                                   | 20 ± 0.5      | mA   |                       |

| Clamp Voltage                                                               | 28 +0 % -2 %  | V    |                       |

| Ramp Rate                                                                   | 70 MAX.       | V/μs | 15 V point/150 Ω load |

| Sense Current Interruption before and after address change                  | 10 MIN.       | μS   | , , ,                 |

| Programming V <sub>CC</sub>                                                 | 5.0 +5 % -0 % | V    |                       |

| Maximum Sensed Voltage * for programmed "1"                                 | 7.0 ± 0.1     | V    |                       |

| Delay from trailing edge of programming pulse before sensing output voltage | 0.7 MIN.      | μs   |                       |

A bit is judged to be programmed when two successive sense readings 10 µs apart with no intervening programming

pulse, pass the limit. When this condition has been met, four additional pulses are applied and the pulse train,

then the sense current is terminated.

Fig. 2 Typical Output Voltage Waveform.

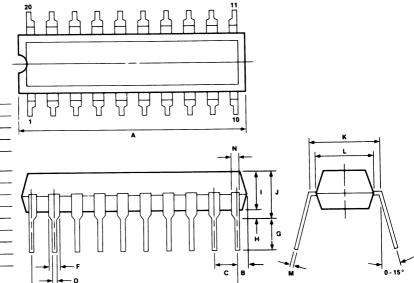

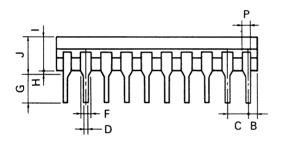

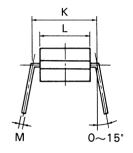

## **Package Dimensions**

Millimeters 25.40 max

1.27 max

2.54 [TP]

.50 ± .10

1.1 min

3.5 ± .30

4.31 max 5.08 max 7.62 (TP)

6.4 .25 <sup>+.10</sup> -.05

.9 min

#### **20PIN Plastic DIP**

Item

A

С

D

E

G

H

K

M

| A | 02 |  |

|---|----|--|

## Package Dimensions 20 PIN Cerdip (300mil)

| ITEM | MILLIMETERS           |

|------|-----------------------|

| Α    | 25.40 MAX.            |

| В    | 1.27 MAX.             |

| С    | 2.54 (T.P.)           |

| D    | 0.46 <sup>±0.05</sup> |

| F    | 1.42 MIN.             |

| G    | 3.5 <sup>±0.3</sup>   |

| Н    | 0.51 MIN.             |

| ı    | 3.95                  |

| J    | 5.08 MAX.             |

| Κ    | 7.62 (T.P.)           |

| L    | 7.32                  |

| М    | $0.25^{\pm0.06}$      |

| N    | 0.25                  |

| Р    | 0.89 MIN.             |

|      |                       |