### STMEC001

### Power interface switch for ExpressCard<sup>TM</sup>

#### **Features**

- Compliant with PC Card<sup>™</sup> standard for ExpressCard

- 3-channel power interface switch

- Built-in under-voltage lockout (UVLO) circuit

- Ultra-low standby-mode current

- Additional 5 V or 12 V power supply not required

- High reliability ensured with integrated overcurrent, thermal and undervoltage protection circuitries applied to each voltage rail

- Soft start function for non-rush current

- Ultra-low standby-mode current for power saving

- Ultra-low ON resistance for fast switching

#### **Description**

The STMEC001 is an ExpressCard power interface switch which provides the complete power management solution required by the ExpressCard specification.

The STMEC001 consists of 3 internal switches distributing 3.3 V, 3.3V<sub>AUX</sub>, and 1.5 V to the ExpressCard socket without the need of additional charge pump or external switches.

The STMEC001 ExpressCard power switch is ideal for notebook computers, desktop computers, personal digital assistants (PDA), or other handheld devices implementing the ExpressCard schematic.

Table 1. Device summary

| Order code   | Package | Packing       |

|--------------|---------|---------------|

| STMEC001QTR  | QFN16   | Tape and reel |

| STMEC001ATTR | TSSOP20 | Tape and reel |

Contents STMEC001

## **Contents**

| 1 | Pin description                | 3 |

|---|--------------------------------|---|

|   | 1.1 Pin functional description | 5 |

| 2 | Logic diagram                  | 6 |

| 3 | Maximum ratings                | 8 |

| 4 | Power states                   |   |

|   | 4.1 Power states description   | 9 |

| 5 | Electrical characteristics1    | 0 |

| 6 | Logic characteristics          | 3 |

| 7 | Switching times 1              | 4 |

| 8 | Package mechanical data 1      | 6 |

| 9 | Revision history               | 8 |

STMEC001 Pin description

## 1 Pin description

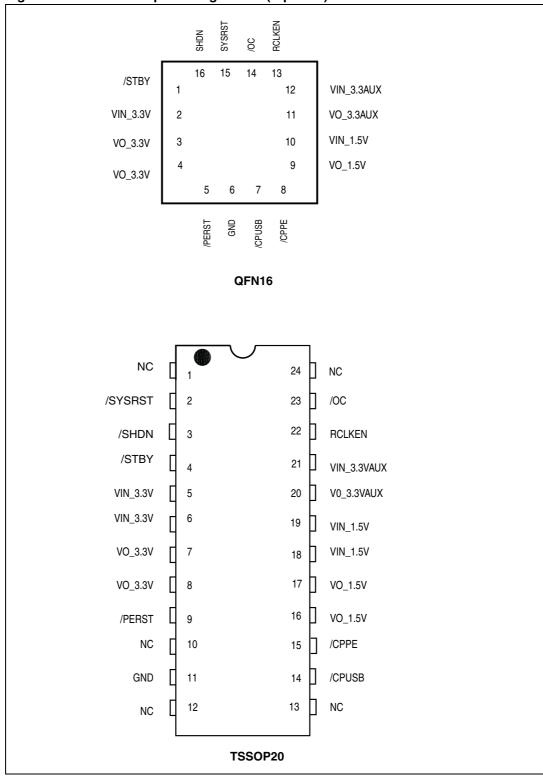

Figure 1. STMEC001 pin configuration (top view)

577

Pin description STMEC001

Table 2. Pin assignments

| F     | Pin     | Norre                   | Turne | December                                                                                                                                                                                                                |

|-------|---------|-------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN16 | TSSOP20 | Name                    | Туре  | Description                                                                                                                                                                                                             |

| -     | 1       | NC                      | -     | No connection                                                                                                                                                                                                           |

| 15    | 2       | /SYSRST                 | I     | System Reset input - active low, logic level signal, internal 150 K $\Omega$ pull-up                                                                                                                                    |

| 16    | 3       | /SHDN                   | I     | Shutdown input - active low, logic level signal, internal 150 KΩ pull-down                                                                                                                                              |

| 1     | 4       | /STBY                   | I     | Standby input - active low, logic level signal, internal 150 $\mathrm{K}\Omega$ pull-down                                                                                                                               |

| 2     | 5       | VIN_3.3V                | I     | 3.3 V input for VO_3.3V                                                                                                                                                                                                 |

| -     | 6       | VIN_3.3V                | I     | 3.3 V input for VO_3.3V                                                                                                                                                                                                 |

| 3     | 7       | VO_3.3V                 | 0     | Switched output that delivers 0 V, 3.3 V or high impedance to card                                                                                                                                                      |

| 4     | 8       | VO_3.3V                 | 0     | Switched output that delivers 0 V, 3.3 V or high impedance to card                                                                                                                                                      |

| 5     | 9       | /PERST                  | 0     | A logic level power good to slot (delayed)                                                                                                                                                                              |

| -     | 10      | NC                      | -     | No connection                                                                                                                                                                                                           |

| 6     | 11      | GND                     | -     | Ground                                                                                                                                                                                                                  |

| -     | 12      | NC                      | -     | No connection                                                                                                                                                                                                           |

| -     | 13      | NC                      | -     | No connection                                                                                                                                                                                                           |

| 7     | 14      | /CPUSB                  | I     | Card Present input for USB cards, internal 150 $\mbox{K}\Omega$ pull-up                                                                                                                                                 |

| 8     | 15      | /CPPE                   | I     | Card Present input for PCI ExpressCard, internal 150 $\rm K\Omega$ pull-up                                                                                                                                              |

| 9     | 16      | VO_1.5V                 | 0     | Switched output that delivers 0 V, 1.5 V or high impedance to card                                                                                                                                                      |

| -     | 17      | VO_1.5V                 | 0     | Switched output that delivers 0 V, 1.5 V or high impedance to card                                                                                                                                                      |

| 10    | 18      | VIN_1.5V                | I     | 1.5 V input for 1.5Vout                                                                                                                                                                                                 |

| -     | 19      | VIN_1.5V                | I     | 1.5 V input for 1.5V <sub>OUT</sub>                                                                                                                                                                                     |

| 11    | 20      | VO_3.3V <sub>AUX</sub>  | 0     | Switched output that delivers 0 V, 3.3 V or high impedance to card                                                                                                                                                      |

| 12    | 21      | VIN_3.3V <sub>AUX</sub> | I     | 3.3 V input for VO_3.3V <sub>AUX</sub> and chip power                                                                                                                                                                   |

| 13    | 22      | RCLKEN                  | I/O   | Reference Clock Enable signal. As an output, a logic level power good to host for slot (open drain). As an input, if kept inactive by the host, prevents /PERST from being de-asserted, internal 150 K $\Omega$ pull-up |

| 14    | 23      | /OC                     | 0     | Over-current status output for slot (open drain)                                                                                                                                                                        |

| -     | 24      | NC                      | -     | No connection                                                                                                                                                                                                           |

STMEC001 Pin description

## 1.1 Pin functional description

Table 3. Pin detailed descriptions

| Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPPE   | A logic low level on this input indicates that the card present supports PCI Express functions. This input pin connects to the 3.3 $V_{AUX}$ input through a 150 $k\Omega$ internal pull up. When inserted, the card physically connects this input to ground if the card supports PCI Express functions.                                                                                                                                                                                                                                                                                                                                  |

| CPUSB  | A logic low level on this input indicates that the card present supports USB functions. The input pin CPUSB connects to the 3.3 $V_{AUX}$ input through a 150 $k\Omega$ internal pull up. When inserted, the card physically connects CPUSB to ground if the card supports USB functions.                                                                                                                                                                                                                                                                                                                                                  |

| SHDN   | When asserted (logic low), this input instructs the STMEC001 to turn off all voltage outputs and the discharge FETs at the 3 outputs are activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| STBY   | When asserted (logic low), this input places the power switch in Standby Mode by turning off the 3.3 V and 1.5 V power switches and keeping the 3.3 V <sub>AUX</sub> switch on.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RCLKEN | This pin serves as both an input and an output. On power up, the power switch keeps this signal at a low state as long as any of the output power rails are out of their tolerance range. Once all output power rails are within tolerance, the power switch releases RCLKEN allowing it to transition to a high state (internally pulled up to 3.3 $V_{AUX}$ ). The transition of RCLKEN from a low to a high state starts an internal timer for the purpose of de-asserting /PERST. As an input, RCLKEN can be kept low to delay the start of the /PERST internal timer. RCLKEN can be used by the host system to enable a clock driver. |

| PERST  | On power up, this output remains asserted. Once all power rails are within tolerance, RCLKEN is asserted and /PERST is de-asserted after a time delay. On power down, this output is asserted whenever any of the power rails drop below their voltage tolerance.                                                                                                                                                                                                                                                                                                                                                                          |

| SYSRST | This input is driven by the host system and directly affects /PERST. Asserting /SYSRST (logic level: low) forces /PERST to assert.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OC     | The OC pin is an open drain output for over-current indication. Output does not turn off during over-current condition. The output voltage decreases as the output current exceeds over-current limit. Only if the temperature increases above the limit the output is turned off completely. Over-current in one output does not affect the other outputs.                                                                                                                                                                                                                                                                                |

Logic diagram STMEC001

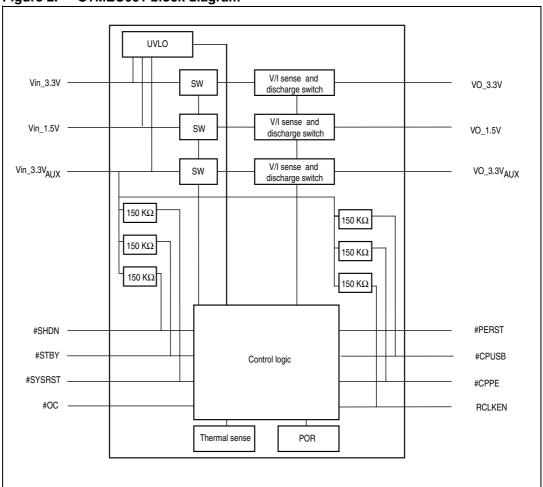

## 2 Logic diagram

STMEC001 Logic diagram

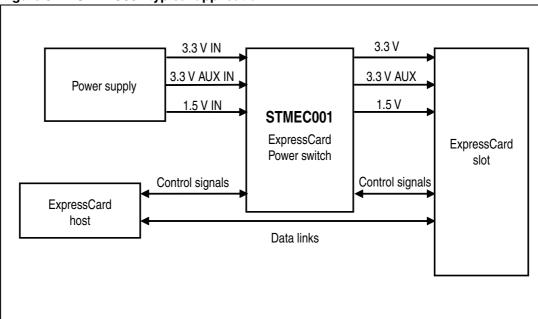

Figure 3. STMEC001 typical application

**577**

Maximum ratings STMEC001

### 3 Maximum ratings

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 4. Absolute maximum ratings<sup>(1)</sup>

| Symbol           | Parameter                                                                                          | Value                                                    | Unit |

|------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|

|                  |                                                                                                    | V <sub>I</sub> (3.3V <sub>IN</sub> ) – 0.3 to 4.6        | V    |

| VI               | Input voltage                                                                                      | V <sub>I</sub> (1.5V <sub>IN</sub> ) – 0.3 to 4.6        | V    |

|                  |                                                                                                    | $V_{I}(3.3V_{AUX}) - 0.3 \text{ to } 4.6$                | V    |

|                  | Output current                                                                                     | V <sub>I</sub> (3.3V <sub>IN</sub> ) internally limited  |      |

| I <sub>O</sub>   |                                                                                                    | V <sub>I</sub> (1.5V <sub>IN</sub> ) internally limited  |      |

|                  |                                                                                                    | V <sub>I</sub> (3.3V <sub>AUX</sub> ) internally limited |      |

| T <sub>OP</sub>  | Operating junction temperature, T <sub>J</sub> (max to be calc. at worst case PD at 85° C ambient) | -40 to 120                                               | °C   |

| T <sub>STG</sub> | Storage temperature range                                                                          | -55 to 150                                               | °C   |

Absolute maximum ratings are those values above which damage to the device may occur. Functional

operation under these conditions is not implied. All voltages are referenced to GND.

STMEC001 Power states

#### 4 Power states

The STMEC001 operates in a number of states, as described in the following table:

Table 5. Power states

| Vo                  | Voltage inputs |       |       | Logic states |       |       | Outputs             |       | Mode  |            |

|---------------------|----------------|-------|-------|--------------|-------|-------|---------------------|-------|-------|------------|

| 3.3V <sub>AUX</sub> | 3.3 V          | 1.5 V | /SHDN | /CPUSB       | /CPPE | /STBY | 3.3V <sub>AUX</sub> | 3.3 V | 1.5 V |            |

| ON                  | Х              | Х     | 1     | 1            | 1     | Х     | GND                 | GND   | GND   | No card    |

| ON                  | Х              | Х     | 0     | Х            | Х     | Х     | GND                 | GND   | GND   | Shutdown   |

| ON                  | ON             | ON    | 1     | 0            | Х     | 1     | ON                  | ON    | ON    | USB enable |

| ON                  | ON             | ON    | 1     | Х            | 0     | 1     | ON                  | ON    | ON    | PE enable  |

| ON                  | ON             | ON    | 1     | Х            | Х     | 0     | ON                  | OFF   | OFF   | Standby    |

| OFF                 | Х              | X     | Х     | Х            | Х     | X     | OFF                 | OFF   | OFF   | OFF        |

#### 4.1 Power states description

- No card mode: when no card is inserted, and at least 3.3 V<sub>AUX</sub> is available, all outputs are grounded

- Shutdown mode: when /SHDN is asserted, and at least 3.3 V<sub>AUX</sub> is available all outputs are grounded

- **USB/PW enable mode**: when all 3 inputs are available, detection of cartd insertion turns on all 3 outputs.

- VIN\_3.3 V, VIN\_3.3V<sub>AUX</sub> and VIN\_1.5 V are present at the USB/PW enable input of the power switch prior to a card being inserted. Power to the card is based on the state of /CPUSB and /CPPE (see table).

- The card is present and VIN\_1.5 V or/and VIN\_3.3 V is removed from the input of the power switch; VIN\_3.3V<sub>AUX</sub> will still be provided to the card, VIN\_1.5 and VIN\_3.3 V will be disabled (see table). If power to VIN\_1.5 V and VIN\_3.3 V is restored, output to the card will be restored.

- Prior to the insertion of a card, VIN\_3.3 V<sub>AUX</sub> is available, VIN\_3.3 V and VIN\_1.5 V are not available; no power is made available to the card. If VIN\_1.5 V and VIN\_3.3 V are made available at the input of the power switch after the card is inserted, both VO\_3.3 V and VO\_1.5 V are made available to the card.

- Standy mode: when all 3 supplies are available and /STBY is asserted. Only 3.3 V<sub>AUX</sub> output is on.

- OFF mode: if V<sub>AUX</sub> is off, all outpus are off. When VIN\_3.3V<sub>AUX</sub> is not present, VIN\_1.5 V or/and VIN\_3.3 V must not be present.

Electrical characteristics STMEC001

### 5 Electrical characteristics

Table 6. Recommended operating conditions

| Symbol          | Parameter                                                                                                 | Value        | Unit |

|-----------------|-----------------------------------------------------------------------------------------------------------|--------------|------|

|                 | Input voltage: $V_I(3.3V_{IN})$ is required for its respective functions                                  | 3.0 to 3.6   | V    |

| VI              | Input voltage: V <sub>I</sub> (1.5V <sub>IN</sub> ) is required for its respective functions              | 1.35 to 1.65 | ٧    |

|                 | Input voltage: V <sub>I</sub> (3.3V <sub>AUX</sub> ) is required for all circuit operations               | 3.0 to 3.6   | ٧    |

|                 | Output current: I <sub>O</sub> (3.3V) at T <sub>J</sub> = 100 ° C                                         | 1.3 (max.)   | Α    |

| Io              | Output current: I <sub>O</sub> (1.5V) at T <sub>J</sub> = 100 ° C                                         | 650 (max.)   | mA   |

|                 | Output current: I <sub>O</sub> (AuxV) at T <sub>J</sub> = 100 °C                                          | 275 (max.)   | mA   |

| T <sub>OP</sub> | Operating junction temperature, $T_{\rm J}$ (max to be calc. at worst case PD at 85 $^{\circ}$ C ambient) | 100          | °C   |

Table 7.

Electrical characteristics

$T_{J} = 25^{\circ} \underline{C}, \ V_{I}(V_{IN} \ 3.3 \ V) = \underline{V_{I}(V_{IN} \ 3.3 V_{AUX})} = 3.3 \ V, \ V_{I}(V_{IN} \ 1.5 \ V) = 1.5 \ V$

| Symbol                         | Parameter                                      | Test conditions                       | Min   | Тур | Max | Unit  |

|--------------------------------|------------------------------------------------|---------------------------------------|-------|-----|-----|-------|

|                                | VIN_3.3 V to VO_3.3 V                          | I = 1300 mA, T <sub>J</sub> = 25 °C   | 53 64 |     | 64  |       |

|                                | VIIV_3.3 V 10 VO_3.3 V                         | I = 1300 mA, T <sub>J</sub> = 100 ° C |       |     | 80  |       |

| R <sub>SW</sub> <sup>(1)</sup> | VIN_1.5 V to VO_1.5 V                          | I = 650 mA, T <sub>J</sub> = 25 °C    |       | 70  | 88  | mΩ    |

| TSSOP20                        | VIIV_1.5 V 10 VO_1.5 V                         | I = 650 mA, T <sub>J</sub> = 100 °C   |       |     | 105 | 11122 |

|                                | VIN 2 2V + 5 VO V                              | I = 275 mA, T <sub>J</sub> = 25 ° C   |       | 140 | 170 |       |

|                                | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub> | I = 275 mA, T <sub>J</sub> = 100 °C   |       |     | 210 |       |

|                                | VIN_3.3 V to VO_3.3 V                          | I = 1300 mA, T <sub>J</sub> = 25 °C   |       | 53  | 64  |       |

|                                | VIIV_0.0 V 10 VO_0.0 V                         | I = 1300 mA, T <sub>J</sub> = 100 ° C |       |     | 80  |       |

| R <sub>SW</sub> <sup>(1)</sup> | VIN_1.5 V to VO_1.5 V                          | I = 650 mA, T <sub>J</sub> = 25 ° C   |       | 80  | 92  | mΩ    |

| QFN16                          | VIIV_1.5 V to VO_1.5 V                         | I = 650 mA, T <sub>J</sub> = 100 °C   |       |     | 115 | 11152 |

|                                | VIN 2 2V + 5 VO V                              | I = 275 mA, T <sub>J</sub> = 25 ° C   |       | 170 | 192 |       |

|                                | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub> | I = 275 mA, T <sub>J</sub> = 100 °C   |       |     | 230 |       |

|                                | R <sub>O</sub> (3.3 V)<br>discharge resistance | I discharge = 1 mA                    | 0.1   |     | 0.5 |       |

| R <sub>O</sub>                 | R <sub>O</sub> (1.5 V)<br>discharge resistance | I discharge = 1 mA                    | 0.1   |     | 0.5 | ΚΩ    |

|                                | R <sub>O</sub> (1.5 V)<br>discharge resistance | I discharge = 1 mA                    | 0.1   |     | 0.5 |       |

Table 7. Electrical characteristics  $T_J = 25^{\circ} \text{ C}, \ V_I(V_{IN} \ 3.3 \ V) = V_I(V_{IN} \ 3.3 V_{AUX}) = 3.3 \ V, \ V_I(V_{IN} \ 1.5 \ V) = 1.5 \ V \text{ (continued)}$

| Symbol          | Parameter                                                            | Test conditions                                                | Min | Тур | Max  | Unit |

|-----------------|----------------------------------------------------------------------|----------------------------------------------------------------|-----|-----|------|------|

|                 | I <sub>O</sub> (3.3 V) limit<br>(limit is the steady state<br>value) | T <sub>J</sub> -40° C to100° C<br>Output powered into a short  |     |     | 2.5  | А    |

| I <sub>OS</sub> | I <sub>O</sub> (1.5 V) limit                                         | T <sub>J</sub> -40° C to100° C<br>Output powered into a short  | 650 |     | 1300 | mA   |

|                 | I <sub>O</sub> (V <sub>AUX</sub> ) limit                             | T <sub>J</sub> -40° C to 100° C<br>Output powered into a short | 275 |     | 660  |      |

<sup>1.</sup> Switch resistance (in production - probe testing at 1.3 A. Final test at 1.0 A and apply guard band)

Table 8. Power switching

| Symbol                           | Parameter                                                  |                                      | Test condition                                                                                                                         | Min | Тур | Max | Unit |

|----------------------------------|------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Tsh                              | Thermal shutdown, trip point, T <sub>J.</sub>              |                                      | Over-current condition                                                                                                                 | 155 |     | 165 | °C   |

|                                  | Hysteresis                                                 |                                      |                                                                                                                                        |     | 10  |     | °C   |

|                                  | Current limit response time.                               |                                      | $V_O$ (3.3 $V_{OUT}$ ) with 100 m $\Omega$ short                                                                                       |     | 5   | 20  |      |

| I <sub>OL</sub>                  | From short to first threshold wit                          | hin 1.1 times                        | V <sub>O</sub> (1.5V <sub>OUT</sub> ) with100 mΩ short                                                                                 |     | 5   | 20  | μs   |

|                                  | of the final current limit                                 |                                      | V <sub>O</sub> (V <sub>AUX</sub> ) with100 mΩ short                                                                                    |     | 5   | 20  |      |

|                                  |                                                            | V <sub>IN_3.3</sub> V <sub>AUX</sub> | $V_{O}(V_{AUX}) = V_{I}(3.3V_{AUX}) =$                                                                                                 |     |     | 120 |      |

|                                  | Input quiescent current: normal operation                  | V <sub>IN_3.3V</sub>                 | $V_I(3.3V_{IN}) V_O(1.5V) = VI(1.5VIN)$<br>$T_J -40^{\circ} C,100^{\circ} C$                                                           |     |     | 40  |      |

|                                  | normal operation                                           | V <sub>IN_1.5V</sub>                 | Outputs are ON and unloaded                                                                                                            |     |     | 10  | μΑ   |

|                                  |                                                            | V <sub>IN_3.3</sub> V <sub>AUX</sub> | $V_O(V_{AUX}) = V_I(3.3V_{AUX}) = V_I(3.3V_I)$                                                                                         |     | 150 | 180 |      |

| IQ                               | Input quiescient current:<br>normal operation with pull-up | V <sub>IN_3.3V</sub>                 | N) $V_O(1.5 \text{ V}) = V_I(1.5 \text{V}_{IN})$<br>$T_J -40^{\circ} \text{ C}, 100^{\circ} \text{ C}]$<br>Outputs are ON and unloaded |     | 25  | 40  |      |

|                                  |                                                            | V <sub>IN_1.5V</sub>                 |                                                                                                                                        |     | 10  | 25  |      |

|                                  | Input quiescient current: /SHDN asserted with pull-up      | V <sub>IN_3.3</sub> V <sub>AUX</sub> | T <sub>J</sub> -40° C,100° C<br>discharge FETs are ON                                                                                  |     | 150 | 270 |      |

|                                  |                                                            | V <sub>IN_3.3V</sub>                 |                                                                                                                                        |     | 10  | 15  |      |

|                                  | 7011DIV asserted with pull-up                              | V <sub>IN_1.5V</sub>                 |                                                                                                                                        |     | 10  | 15  | •    |

|                                  | Forward leakage current (curre                             | nt measured                          | $V_{IN\_3.3}V_{AUX}$                                                                                                                   |     |     |     |      |

| SHDN                             | at input pins/no card present)                             |                                      | V <sub>IN</sub> _3.3V                                                                                                                  |     | 15  | 20  | μΑ   |

|                                  | /SHDN inactive                                             |                                      | V <sub>IN</sub> _1.5V                                                                                                                  |     | 5   | 10  |      |

|                                  |                                                            | V V                                  | T <sub>J</sub> = 25 ° C                                                                                                                |     | 5   | 10  |      |

|                                  |                                                            | V <sub>IN_3.3</sub> V <sub>AUX</sub> | T <sub>J</sub> = 100 ° C                                                                                                               |     | 20  | 50  |      |

| I <sub>LEAK</sub> <sup>(1)</sup> | Reverse leakage current (current measured from             | V                                    | T <sub>J</sub> = 25 ° C                                                                                                                |     | 10  | 15  | μΑ   |

| 'LEAK`                           | output pins / input grounded)                              | V <sub>IN_1.5V</sub>                 | T <sub>J</sub> = 100 ° C                                                                                                               |     | 30  | 50  | μΑ   |

|                                  |                                                            | V                                    | T <sub>J</sub> = 25 ° C                                                                                                                |     | 10  | 15  |      |

|                                  |                                                            | V <sub>IN_3.3V</sub>                 | T <sub>J</sub> = 100 ° C                                                                                                               |     | 30  | 50  |      |

<sup>1.</sup> All high side switches are in Hi-Z state,  $V_O$  (AUX) =  $V_O$  (3.3 V) = 3.3 V, Vo (1.5 V) = 1.5 V,  $T_J$  -40 ° C,100 ° C

477

Electrical characteristics STMEC001

Table 9. Undervoltage lockout (UVLO)

| Symbol | Parameter         | Test condition                                                        | Min | Тур | Max  | Unit |

|--------|-------------------|-----------------------------------------------------------------------|-----|-----|------|------|

|        | VIN_3.3 UVLO      | VIN_3.3 level, below which<br>VIN_3.3 and VIN_1.5 switches<br>are off | 2.6 |     | 2.9  | V    |

| UVLO   | VIN_1.5 UVLO      | VIN_1.5 level, below which<br>VIN_3.3 and VIN_1.5 switches<br>are off | 1   |     | 1.25 | V    |

|        | VIN_3.3 VAUX UVLO | VIN_3.3VAUX level, below which sets the device into OFF state         | 2.6 |     | 2.9  | ٧    |

|        | UVLO hysteresis   |                                                                       |     | 100 |      | mV   |

# 6 Logic characteristics

Table 10. Logic states

| Logic transition                                   | Condition                                        | Min | Тур | Max  | Unit |

|----------------------------------------------------|--------------------------------------------------|-----|-----|------|------|

| Logic input valtage                                | High level                                       | 2.0 |     |      | V    |

| Logic input voltage                                | Low level                                        |     |     | 0.8  | V    |

|                                                    | 3.3 V output falling                             | 2.7 |     | 3.0  |      |

| PERST# assertion threshold of output voltage       | AUX output falling                               | 2.7 |     | 3.0  | V    |

| voitage                                            | 1.5 V output falling                             | 1.2 |     | 1.35 |      |

| PERST# assertion delay from output voltage invalid | Output falling below threshold                   |     |     | 500  | ns   |

| PERST# de-assertion from output voltage valid      | Output rising above threshold                    | 4   | 10  | 20   | ms   |

| PERST# assertion delay from SYSRST#                | STSRST asserted or de-asserted                   |     |     | 500  | ns   |

| RCLKEN assertion delay from output voltage valid   | Output rising above threshold                    |     |     | 100  | μs   |

| OC# output low voltage                             | I <sub>OC</sub> = 2 mA                           |     |     | 0.4  | V    |

| OC# leakage current                                | V <sub>OC</sub> = 3.6 V                          |     |     | 1    | μΑ   |

| OC# deglitch                                       | Falling into or out of an over-current condition | 6   |     | 20   | μѕ   |

Table 11. ESD protections

| Pin                                  | Condition           | ESD tolerance | Unit |

|--------------------------------------|---------------------|---------------|------|

| V <sub>OUT</sub> (3.3 V, 1.5 V, AUX) | Versus GND & supply | 6             |      |

| All other pins (except RCLKEN)       | Versus GND & supply | 2             | kV   |

| RCLKEN                               | Versus GND          | 2             | KV   |

| RCLKEN                               | Versus supply       | 1             |      |

**47/**

Switching times STMEC001

## 7 Switching times

Table 12. Switching characteristics

| Symbol                          | Parameter                                                   |                                                                               | Condition                                                          | Min | Тур | Max  | Unit |

|---------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------|------|

|                                 | VIN_3.3V to VO_3.3V                                         | $C_{L(3.3V)} = 0.1 \ \mu F$<br>$I_{o(3.3V)} = 0 \ A$                          | 0.1                                                                |     | 3   |      |      |

|                                 | t <sub>R</sub> Output rise time                             | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>                                | $C_{L(AUX)} = 0.1 \mu F$<br>$I_{o(AUX)} = 0A$                      | 0.1 |     | 3    |      |

|                                 |                                                             | VIN_1.5V to VO_1.5V                                                           | $C_{L(1.5V)} = 0.1 \mu F$<br>$I_{o(1.5V)} = 0 A$                   | 0.1 |     | 3    |      |

| t <sub>R</sub>                  |                                                             | VIN_3.3V to VO_3.3V                                                           | C <sub>L(3.3V)</sub> = 100 μF<br>R <sub>L</sub> = VO_3.3V / 1.0 A  | 0.1 |     | 6    | ms   |

|                                 |                                                             | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>                                | $C_{L(3.3V)} = 100 \mu F$<br>$R_L = VO_{V_{AUX}} / 0.25 A$         | 0.1 |     | 6    |      |

|                                 |                                                             | VIN_1.5V to VO_1.5V                                                           | C <sub>L(3.3V)</sub> = 100 μF<br>R <sub>L</sub> = VO_1.5 V / 0.5 A | 0.1 |     | 6    |      |

|                                 |                                                             | VIN_3.3V to VO_3.3V                                                           | $C_{L(3.3V)} = 0.1 \mu F$<br>$I_{o(3.3V)} = 0 A$                   | 10  |     | 150  |      |

| Output fall time                | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>              | $C_{L(AUX)} = 0.1 \mu F$<br>$I_{o(AUX)} = 0 A$                                | 10                                                                 |     | 150 | μs   |      |

| t <sub>F</sub>                  | Output fall time t <sub>F</sub> (/CPUSB and /CPPE inactive) | VIN_1.5V to VO_1.5V                                                           | $C_{L(1.5V)} = 0.1 \mu F$<br>$I_{o(1.5V)} = 0 A$                   | 10  |     | 150  |      |

|                                 |                                                             | VIN_3.3V to VO_3.3V                                                           | $C_{L(3.3V)} = 20 \mu F$ , no load                                 | 2.0 |     | 30.0 |      |

|                                 |                                                             | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>                                | $C_{L(AUX)} = 20 \mu F$ , no load                                  | 2.0 |     | 30.0 | ms   |

|                                 |                                                             | VIN_1.5V to VO_1.5V                                                           | $C_{L(1.5V)} = 20 \mu F$ , no load                                 | 2.0 |     | 30.0 |      |

|                                 |                                                             | VIN_3.3V to VO_3.3V                                                           | $C_{L(3.3V)} = 0.1 \mu F$<br>$I_{o(3.3V)} = 0 A$                   | 10  |     | 80   |      |

| Output fall time (/SHDN active) | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>              | $C_{L(AUX)} = 0.1 \mu F$<br>$I_{o(AUX)} = 0 A$                                | 10                                                                 |     | 80  | μs   |      |

|                                 | VIN_1.5V to VO_1.5V                                         | $C_{L(1.5V)} = 0.1 \mu F$<br>$I_{o(1.5V)} = 0 A$                              | 10                                                                 |     | 80  |      |      |

|                                 | VIN_3.3V to VO_3.3V                                         | C <sub>L(3.3V)</sub> = 100 μF<br>R <sub>L</sub> = VO_3.3V/1.0 A               | 0.1                                                                |     | 5.0 |      |      |

|                                 | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub>              | C <sub>L(3.3V)</sub> = 100 μF<br>R <sub>L</sub> = VO_V <sub>AUX</sub> /0.25 A | 0.1                                                                |     | 5.0 | ms   |      |

|                                 |                                                             | VIN_1.5V to VO_1.5V                                                           | C <sub>L(3.3V)</sub> = 100 μF<br>R <sub>L</sub> = VO_1.5V/0.5 A    | 0.1 |     | 5.0  |      |

STMEC001 Switching times

Table 12. Switching characteristics (continued)

| Symbol |                                   | Parameter                                      | Condition                                                      | Min  | Тур | Max | Unit |  |

|--------|-----------------------------------|------------------------------------------------|----------------------------------------------------------------|------|-----|-----|------|--|

|        |                                   | VIN_3.3V to VO_3.3V                            | $C_{L(3.3V)} = 0.1 \mu F$<br>$I_{o(3.3V)} = 0 A$               | 0.02 |     | 1.0 |      |  |

|        | t <sub>PD</sub> Propagation delay | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub> | $C_{L(AUX)} = 0.1 \mu F,$<br>$I_{o(AUX)} = 0 A$                | 0.02 |     | 1.0 | ı    |  |

| +      |                                   | VIN_1.5V to VO_1.5V                            | $C_{L(1.5V)} = 0.1 \mu F$<br>$I_{o(1.5V)} = 0 A$               | 0.02 |     | 1.0 | ms   |  |

| чPD    |                                   | VIN_3.3V to VO_3.3V                            | C <sub>L(3.3V)</sub> =100μF<br>R <sub>L</sub> = VO_3.3V/1.0 A  | 0.05 |     | 1.0 | 1115 |  |

|        |                                   | VIN_3.3V <sub>AUX</sub> to VO_V <sub>AUX</sub> | $C_{L(3.3V)} = 100 \mu F$<br>$R_L = VO_V_{AUX}/0.25 A$         | 0.05 |     | 1.0 |      |  |

|        |                                   | VIN_1.5V to VO_1.5V                            | C <sub>L(3.3V)</sub> = 100μF<br>R <sub>L</sub> = VO_1.5V/0.5 A | 0.05 |     | 1.0 |      |  |

### 8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 4. QFN16 (3 x 3 mm) package outline

1. Drawing not to scale.

Table 13. QFN16 (3 x 3 mm) mechanical data

| Table 10. | Q: 11:0 (0 X | o mini) meen | arriodi data |        |       |       |

|-----------|--------------|--------------|--------------|--------|-------|-------|

| Compleal  |              | millimeters  |              | inches |       |       |

| Symbol    | Min          | Тур          | Max          | Min    | Тур   | Max   |

| Α         | 0.80         | 0.90         | 1.00         | 0.032  | 0.035 | 0.039 |

| A1        |              | 0.02         | 0.05         |        | 0.001 | 0.002 |

| A3        |              | 0.20         |              |        | 0.008 |       |

| b         | 0.18         | 0.25         | 0.30         | 0.007  | 0.010 | 0.012 |

| D         |              | 3.00         |              |        | 0.118 |       |

| D2        | 1.55         | 1.70         | 1.80         | 0.061  | 0.067 | 0.071 |

| E         |              | 3.00         |              |        | 0.118 |       |

| E2        | 1.55         | 1.70         | 1.80         | 0.061  | 0.067 | 0.071 |

| е         |              | 0.50         |              |        | 0.020 |       |

| K         |              | 0.20         |              |        | 0.008 |       |

| L         | 0.30         | 0.40         | 0.50         | 0.012  | 0.016 | 0.020 |

| r         |              | 0.09         |              | 0.006  |       |       |

Figure 5. TSSOP20 package outline

1. Drawing not to scale.

Table 14. TSSOP20 mechanical data

| Complete | millimeters |          |      | inches |            |        |

|----------|-------------|----------|------|--------|------------|--------|

| Symbol   | Min         | Тур      | Max  | Min    | Тур        | Max    |

| Α        |             |          | 1.2  |        |            | 0.047  |

| A1       | 0.05        |          | 0.15 | 0.002  | 0.004      | 0.006  |

| A2       | 0.8         | 1        | 1.05 | 0.031  | 0.039      | 0.041  |

| b        | 0.19        |          | 0.30 | 0.007  |            | 0.012  |

| С        | 0.09        |          | 0.20 | 0.004  |            | 0.0079 |

| D        | 6.4         | 6.5      | 6.6  | 0.252  | 0.256      | 0.260  |

| E        | 6.2         | 6.4      | 6.6  | 0.244  | 0.252      | 0.260  |

| E1       | 4.3         | 4.4      | 4.48 | 0.169  | 0.173      | 0.176  |

| е        |             | 0.65 BSC |      |        | 0.0256 BSC |        |

| K        | 0°          |          | 8°   | 0°     |            | 8°     |

| L        | 0.45        | 0.60     | 0.75 | 0.018  | 0.024      | 0.030  |

**\_\_\_\_**

Revision history STMEC001

## 9 Revision history

Table 15. Document revision history

| Date        | Revision                                          | Change                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Aug-2006 | 1                                                 | First release                                                                                                                                                                                                                                                                                |

| 08-Feb-2007 | 2 Replaced TSSOP24 package information with QFN16 |                                                                                                                                                                                                                                                                                              |

| 18-Oct-2007 | 3                                                 | Modified title, added R <sub>SW</sub> values for QFN16 in <i>Table 7 on page 10</i> , small text changes, layout restructure, content reworked to improve readability in <i>Section 4.1: Power states description on page 9</i> , modified <i>Figure 2: STMEC001 block diagram on page 6</i> |

| 17-Apr-2008 | 4                                                 | Modified: Figure 2 and Table 2: Pin assignments on page 4 and Table 5: Power states on page 9, minor text changes.                                                                                                                                                                           |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com