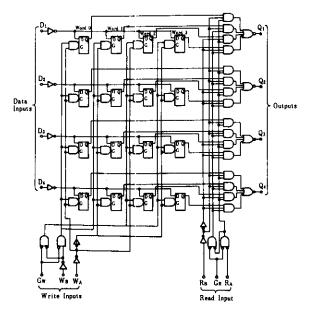

The HD74LS670, 16-bit register files incorporate the equivalent of 98 gates. The register file is organized as 4 words of 4 bits each and separate on-chip decoding is provided for addressing the the four word locations to either write-in or retrieve data.

This permits simultaneous writing into one location and reading from another word location. Four data inputs are available which are used to supply the 4-bit word to be stored. Location of the word is determined by the write-address inputs A and B in conjunction with a write-enable signal. Data applied at the inputs should be in its true form. That is, if a high-level signal is desired from the output, a high-level is applied at the data input for that particular bit location. The latch inputs are arranged so that new data will be accepted only if both internal address gate inputs are high. When this condition exists, data at the D input is transferred to the latch output. When the write-enable input, Gw, is high, the data inputs are inhibited and their levels can cause no change in the information stored in the internal latches. When the read-enable input, GR, is high, the data outputs are inhibited and go into the highimpedance state. The individual address lines permit direct acquisition of data stored in any four of the latches. Four individual decoding gates are used to complete the address for reading a word.

When the read address is made in conjunction with the readenable signal, the word appears at the four outputs.

# **BLOCK DIAGRAM**

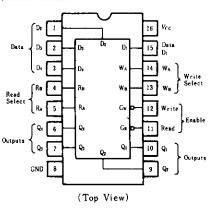

#### **■PIN ARRANGEMENT**

#### **EFUNCTION TABLE**

| W  | rite Inpu | ts | Word           |                  |                |                |  |  |

|----|-----------|----|----------------|------------------|----------------|----------------|--|--|

| Wв | WA        | Gw | 0              | 1                | 2              | 3              |  |  |

| L  | L         | L  | Q-D            | $\mathbf{Q}_{o}$ | Q <sub>0</sub> | Q <sub>0</sub> |  |  |

| L  | н         | L  | Q <sub>0</sub> | Q-D              | Q.             | Q <sub>0</sub> |  |  |

| Н  | L         | L  | Q <sub>0</sub> | Q <sub>0</sub>   | Q=D            | Q,             |  |  |

| Н  | Н         | L  | Q <sub>o</sub> | Qo               | Q <sub>0</sub> | Q-D            |  |  |

| ×  | ×         | Н  | Q <sub>0</sub> | Q <sub>0</sub>   | Q,             | Q <sub>0</sub> |  |  |

| F              | lead Input | s              | Outputs                       |                               |                               |                               |  |  |

|----------------|------------|----------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--|--|

| R <sub>B</sub> | R₄         | G <sub>R</sub> | Qı                            | $Q_2$                         | Q <sub>3</sub>                | Q,                            |  |  |

| L              | L          | L              | W 0 B1                        | W <sub>0</sub> B <sub>2</sub> | W <sub>0</sub> B <sub>3</sub> | W₀B₄                          |  |  |

| L              | Н          | L              | W <sub>1</sub> B <sub>1</sub> | W <sub>1</sub> B <sub>2</sub> | W <sub>1</sub> B <sub>3</sub> | W <sub>1</sub> B <sub>2</sub> |  |  |

| H              | L          | L              | W 2 B1                        | W <sub>2</sub> B <sub>2</sub> | W 2 B3                        | W <sub>2</sub> B <sub>4</sub> |  |  |

| Н              | Н          | L              | W 1 B1                        | W <sub>3</sub> B <sub>2</sub> | W 3 B 3                       | W <sub>3</sub> B              |  |  |

| ×              | ×          | Н              | Z                             | Z                             | Z                             | Z                             |  |  |

Notes: H = high level, L = low level, X = irrelevant, Z = high impedance (off)

(Q=D) = The four selected internal flip-flop outputs will assume the states applied to the four external data inputs.

Q<sub>e</sub> = The level of Q before the indicated input conditions were established.

$W_0B_1$  = The first bit of word 0, etc.

# **PRECOMMENDED OPERATING CONDITIONS**

| 1t             | em           | Symbol   | min                  | typ  | max  | Unit |

|----------------|--------------|----------|----------------------|------|------|------|

| Supply voltage |              | $V_{cc}$ | V <sub>CC</sub> 4.75 | 5.00 | 5.25 | v    |

|                |              | $I_{OH}$ | _                    | -    | -2.6 | mА   |

| Output curren  | t            | $I_{oL}$ | _                    |      | 8    | mΑ   |

| Pulse width    | Read enable  |          | 25                   | _    | -    |      |

|                | Write enable | i i u    | 60                   |      | _    | ns   |

|                | Data         |          | 10                   |      | _    |      |

| Setup time     | Write enable | t.,,     | 15                   | -    | -    | ns   |

| 77 11          | Data         |          | 15                   |      |      |      |

| Hold time      | Write enable | t,       | 5                    |      |      | ns   |

| Latch time     |              | tiesch   | 60                   | _    | -    | ns   |

# **MELECTRICAL CHARACTERISTICS** $(Ta = -20 \sim +75^{\circ}C)$

| Item                         | Symbol           | Test Condi                                       | tions                | min   | typ* | max  | Unit |

|------------------------------|------------------|--------------------------------------------------|----------------------|-------|------|------|------|

|                              | $V_{IH}$         |                                                  |                      | 2.0   | -    |      | V    |

| Input voltage                | $V_{II.}$        |                                                  |                      | _     | -    | 0.8  | V    |

|                              | Von              | Vcc-4.75V, ViH-2V, ViL-0.                        | 8V, Ion = -2.6mA     | 2.4   | _    |      | V    |

| Output voltage               |                  | $V_{CC} = 4.75 \text{V}, V_{IH} = 2 \text{V},$   | Io1 - 4mA            | _     | _    | 0.4  | v    |

|                              | Vol              | $V_{IL}=0.8V$                                    | Io1 = 8mA            | -     | _    | 0.5  | l v  |

| 0.00                         | I <sub>02H</sub> | 1/ f 053/ 1/ 03/                                 | $V_o = 2.7 \text{V}$ |       |      | 20   | μA   |

| Off-state output current     | IozL             | $V_{CC} = 5.25 \text{V}, V_{IH} = 2 \text{V}$    | Vo-0.4V              |       | _    | 20   |      |

|                              | In Vcc*          | $V_{CC} = 5.25 \text{V}, V_I = 2.7 \text{V}$     | Any D, R or W        |       |      | 20   | μΑ   |

|                              |                  |                                                  | Gw                   | _     |      | 40   |      |

|                              |                  |                                                  | $G_R$                |       | _    | 60   |      |

|                              |                  | V <sub>cc</sub> -5.25V, V <sub>i</sub> -0.4V     | Any D, R or W        |       |      | -0.4 | mA   |

| Input current                |                  |                                                  | Gw                   |       | _    | -0.8 |      |

|                              |                  |                                                  | $G_R$                |       |      | -1.2 |      |

|                              |                  |                                                  | Any D, R or W        | -     |      | 0.1  | mA   |

|                              |                  | $V_{CC} = 5.25 \text{V}, V_{I} = 7 \text{V}$     | Gw                   |       | _    | 0.2  |      |

|                              |                  |                                                  | G <sub>R</sub>       | _     |      | 0.3  |      |

| Short-circuit output current | Ios              | $V_{cc}$ =5.25V                                  |                      | ···30 |      | -130 | mΑ   |

| Supply current               | Icc**            | Vcc-5.25V                                        |                      | _     | 30   | 50   | mA   |

| Input clamp voltage          | $V_{IX}$         | $V_{CC} = 4.75 \text{V}, I_{IN} = -18 \text{mA}$ |                      |       | _    | -1.5 | ν    |

<sup>\*</sup> V<sub>CC</sub>=5V, Ta=25°C

# **SWITCHING CHARACTERISTICS** $(V_{CC}=5V, Ta=25^{\circ}C)$

| Item                   | Symbol           | Inputs | Outputs                       | Test Conditions                     | min | typ | max | Unit |

|------------------------|------------------|--------|-------------------------------|-------------------------------------|-----|-----|-----|------|

| Propagation delay time | I P L H          | Read   | Qı~Qı                         | Q <sub>1</sub> ~Q <sub>4</sub>      | _   | 23  | 40  |      |

|                        | t <sub>PHL</sub> | select |                               |                                     |     | 25  | 45  |      |

|                        | tpin             | Write  |                               |                                     |     | 26  | 45  |      |

|                        | t <sub>PHL</sub> | enable | $Q_1 \sim Q_i$ $Q_1 \sim Q_i$ | $Q_1 \sim Q_1$ $C_L = 15 \text{pF}$ |     | 28  | 50  |      |

|                        | tplH             |        |                               | $R_L = 2k\Omega$                    |     | 25  | 45  |      |

|                        | t <sub>PHI</sub> | Data   |                               | Q <sub>1</sub> ~Q <sub>4</sub>      |     |     | 23  | 40   |

|                        | t <sub>ZH</sub>  |        | <u> </u>                      |                                     | _   | 15  | 35  |      |

| Output enable time     | tzi              | Read   |                               |                                     | _   | 22  | 40  |      |

| Output disable time    | tuz              | enable | $Q_1 \sim Q_1$                | $C_L$ - 5pF,                        |     | 30  | 50  |      |

|                        | tLZ              |        |                               | $R_L = 2k\Omega$                    |     | 16  | 35  |      |

<sup>\*\*:</sup> Maximum I<sub>CC</sub> is guaranteed for the following worst case conditions: 4.5V is applied to all data inputs and both enable inputs, all address inputs are grounded and all outputs are open.

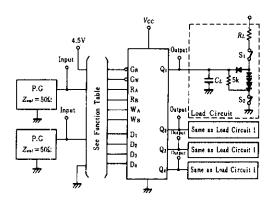

### **TESTING METHOD**

#### Test Circuit

Notes:

- 1.  $C_L$  includes probe and jig capacitance. 2. All diodes are 1S2074 B.

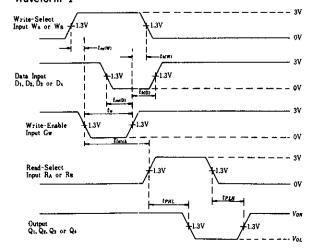

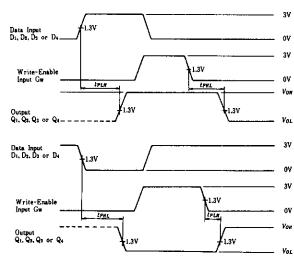

#### Waveform-1

#### Notes:

- 1. High-level input pulses at the select and data inputs are illustrated; however, times associated with low-level pulses are measured from the same reference points.

- 2. When measuring delay times from a read-select inputs, the read-enable input is low.

- 3. Input pulse;  $t_{TLH} \le 15$ ns,  $t_{THL} \le 6$ ns, PRR = 1MHz, duty cycle 50%

#### Waveform-2

Each select address is tested. Prior to the start of each of the Note: above test both write and read address inputs are stabilized with  $W_A = R_A$  and  $W_B = R_B$ . During the test  $G_R$  is low.

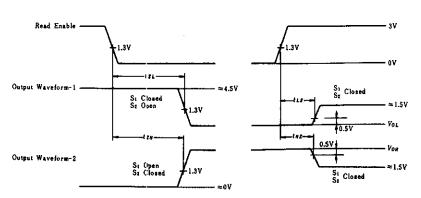

#### Waveform-3

Waveform A is for an output with internal conditions such that the output is low except when disabled by the read-enable input. Waveform B is for an output with internal conditions such that the output is high except when disabled by the read-enable input.

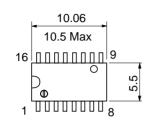

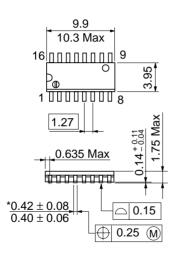

Unit: mm 19.20 20.00 Max 16 7.40 Max 6.30 1.3 1.11 Max 7.62 5.06 Max 2.54 Min 0.51 Min  $0.25^{+0.13}_{-0.05}$  $0.48 \pm 0.10$  $2.54\pm0.25$  $0^{\circ} - 15^{\circ}$ Hitachi Code DP-16 **JEDEC** Conforms EIAJ Conforms Weight (reference value) 1.07 g

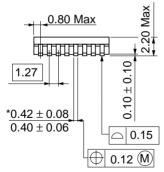

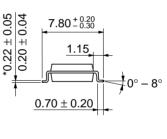

Unit: mm

| Hitachi Code             | FP-16DA  |

|--------------------------|----------|

| JEDEC                    | _        |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.24 g   |

\*Dimension including the plating thickness

Base material dimension

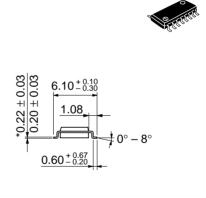

Unit: mm

\*Dimension including the plating thickness

Base material dimension

| Hitachi Code             | FP-16DN  |

|--------------------------|----------|

| JEDEC                    | Conforms |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.15 g   |

# **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HTACHI

## Hitachi, Ltd.

Semiconductor & Integrated Circuits.

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

NorthAmerica URL Europe

http://www.hitachi-eu.com/hel/ecg http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKong) http://www.hitachi.com.hk/eng/bo/grp3/index.htm

http:semiconductor.hitachi.com/

http://www.hitachi.co.jp/Sicd/indx.htm Japan

#### For further information write to:

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose,CA 95134 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Hitachi Europe GmbH Electronic components Group Dornacher Stra§e 3 D-85622 Feldkirchen, Munich Germany Tel: <49> (89) 9 9180-0

Fax: <49> (89) 9 29 30 00 Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road

Maidenhead Berkshire SL6 8YA, United Kingdom

Tel: <44> (1628) 585000 Fax: <44> (1628) 778322 Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666

Fax: <886> (2) 2718-8180

Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong Tel: <852> (2) 735 9218

Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.