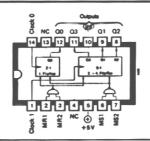

### Description:

This package contains a divide-by-two and a divide-by-five counter.

### Mode of operation:

The device consists of 4 flip-flops which are connected internally to create one divide-by-2 and one divide-by-5 counters.

All flip-flops have a common reset line controlled by two inputs MR1 and MR2. When both MR1 and MR2 are high the counters are cleared.

Flip-flop 1 is not internally connected to the other stages, thus providing a variety of counter

- a) Counting to 10 (BCD): Output Q0 is connected to the Clock 1 input. The input pulses are applied to the Clock 0 input and the divided signal is extracted at Q3. The device counts in binary code up to 9, with the outputs returning to zero on the 10th clock pulse. Pins 2, 3 and 6, 7 must be grounded.

- b) Divide by 2 and divide by 5: Flip-flop 1 is used as a 2:1 divider and flip-flops 2,3 and 4 are used as a 5:1 divider.

- 5:1 divider.

c) Symmetrical biquinary divider 10:1:

Q3 is connected to Clock 0. Clock 1

is used as the clock input. A

symmetrical square-wave with a

frequency 1/10 that of the input

signal is obtained at output Q0.

The flip-flops are triggered on the falling edge of the clock pulse.

When inputs MS1 and MS2 are both

high the counter is preset to 9.

| R   | Outputs |     |     |          |       |   |    |  |  |  |

|-----|---------|-----|-----|----------|-------|---|----|--|--|--|

| MR1 | MR2     | MS1 | MS2 | 00       | Q1 Q2 |   | 03 |  |  |  |

| н   | н       | L   | х   | L        | L     | L | L  |  |  |  |

| н   | н       | ×   | L   | L        | L.    | L | L  |  |  |  |

| X   | X       | н   | H   | Н        | L     | L | Н  |  |  |  |

| L   | х       | L   | х   | Counting |       |   |    |  |  |  |

| x   | L       | x   | L   | Counting |       |   |    |  |  |  |

| L   | x       | X   | L   | Counting |       |   |    |  |  |  |

| x   | L       | L   | x   | Counting |       |   |    |  |  |  |

Application: Counters and dividers 2:1, 5:1 and 10:1

| Families:                                                           |           | •        |     |    |   |   | •        | •       |   |

|---------------------------------------------------------------------|-----------|----------|-----|----|---|---|----------|---------|---|

|                                                                     |           | Std      | ALS | AS | F | Н | L        | LS      | S |

| Min. guaranteed clock<br>frequency flip-flops 2-4<br>Supply Current | MHz<br>mA | 16<br>32 |     |    |   |   | 3<br>3.2 | 16<br>9 |   |

| Data:<br>Min. guaranteed clock<br>frequency flip-flop 1             | MHz       | 32       |     |    |   |   | 3        | 32      |   |

## **DECADE COUNTER**

# 7490