### **PRELIMINARY**

# XRK69772

## 1:12 LVCMOS PLL CLOCK GENERATOR

APRIL 2006 REV. P1.0.0

#### **GENERAL DESCRIPTION**

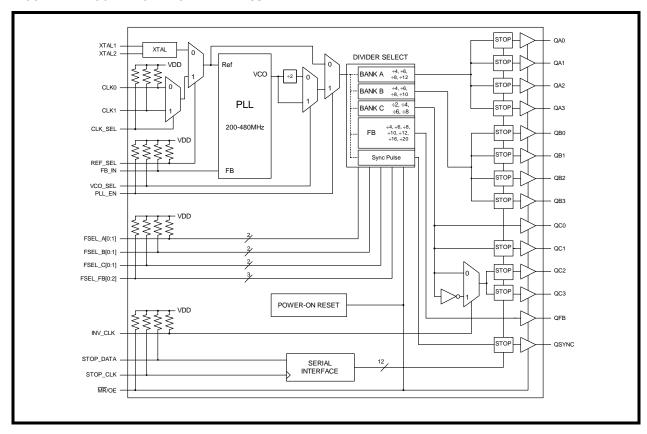

The XRK69772 is a PLL based LVCMOS Clock Generator targeted for high performance and low skew clock distribution applications. The XRK69772 can select between one of three reference inputs and provides 14 LVCMOS outputs -12 outputs (3 banks of 4) for clock distribution, 1 for feedback and 1 for synchronization.

The XRK69772 is a highly flexible device. It can be configured to accept either a crystal oscillator input or one of two LVCMOS compatible inputs for use as the input reference clock source. To support clock redundancy, two LVCMOS inputs are provided. Switching the internal reference clock is controlled by the control input, CLK\_SEL.

The XRK69772 uses PLL technology to frequency lock its outputs to the input reference clock. The divider in the feedback path will determine the frequency of the VCO. Each of the separate output banks can individually divide down the VCO output frequency. This allows the XRK69772 to generate a multitude of different bank frequency ratios and output-to-input frequency ratios.

The outputs of the XRK69772 can individually be immobilized, in the low state, by use of the stop clock feature. All outputs except QC0 and QFB can be immobilized through a 2 pin serial interface. Global output disabling and reset can be achieved the control input  $\overline{\text{MR}}/\text{OE}$ .

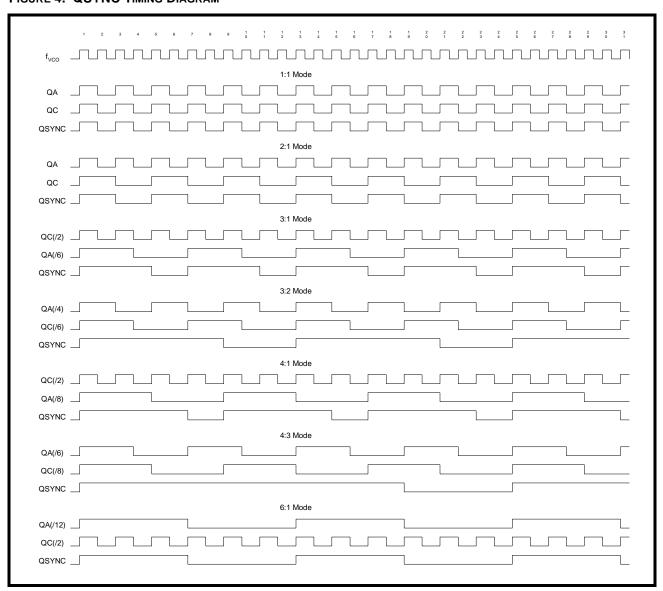

The XRK69772 also has a QSYNC output which can be used for system synchronization purposes. It monitors Bank A and Bank C outputs and goes low one period of the faster clock prior to coincident rising edges of Bank A and

Bank C clocks. QSYNC then goes high again when the coincident rising edges of Bank A and Bank C occur. This feature is used primarily in applications where Bank A and Bank C are running at different frequencies, and is particularly useful when they are running at non-integer multiples of one another.

The XRK69772 has an output frequency range of 8.33MHz to 125MHz and an input frequency range of 5MHz to 120MHz.

#### **FEATURES**

- Fully Integrated PLL

- Selectable crystal oscillator or LVCMOS inputs for reference clock source

- 14 LVCMOS outputs

- 3 banks with 4 outputs each. Frequencies can be individually controlled by bank

- 1 dedicated feedback with frequency control

- 1 Sync

- VCO Range 200MHz to 480MHz

- Output freq. range: 5MHz to 240MHz

- Max Output Skew of 250ps

- Cycle-to-cycle jitter: 150ps (typ)

#### **APPLICATIONS**

- System Clock generator

- Zero Delay Buffer

#### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |

|----------------|--------------|-----------------------------|

| XRK69772CR     | 52-LEAD LQFP | 0°C to +70°C                |

| XRK69772IR     | 52-LEAD LQFP | -40°C to +85°C              |

FIGURE 1. BLOCK DIAGRAM OF THE XRK69772

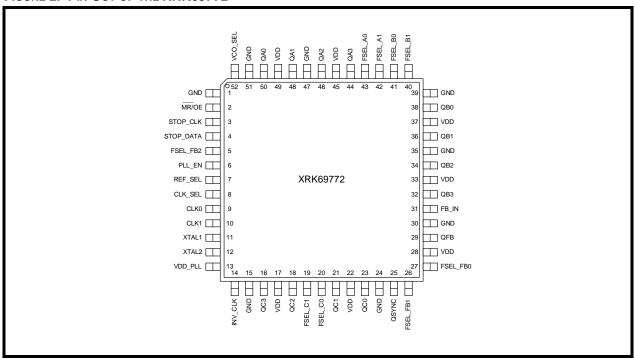

FIGURE 2. PIN OUT OF THE XRK69772

# **PIN DESCRIPTIONS**

| Pin#                             | NAME         | TYPE   | DESCRIPTION                                                                                    |

|----------------------------------|--------------|--------|------------------------------------------------------------------------------------------------|

| 1, 15, 24, 30,<br>35, 39, 47, 51 | GND          | POWER  | Power supply ground                                                                            |

| 2                                | MR/OE        | INPUT* | Master reset and output enable. High = output enabled, Low = device reset & outputs tri-stated |

| 3                                | STOP_CLK     | INPUT* | Clock input for serial control.                                                                |

| 4                                | STOP_DATA    | INPUT* | Data input for serial control                                                                  |

| 5, 26, 27                        | FSEL_FB[2:0] | INPUT* | Select inputs for control of feedback divide value.                                            |

| 6                                | PLL_EN       | INPUT* | PLL bypass. High = PLL, Low = PLL bypass                                                       |

| 7                                | REF_SEL      | INPUT* | Xtal or CLKx select. High = Xtal input selected, Low = CLK0 or CLK1 selected                   |

| 8                                | CLK_SEL      | INPUT* | CLK0 or CLK1 Select. High = CLK1selected, Low = CLK0 selected                                  |

| 9,10                             | CLK0, CLK1   | INPUT* | Reference clock inputs.                                                                        |

| 11                               | XTAL1        | INPUT  | Crystal oscillator input                                                                       |

| 12                               | XTAL2        | OUTPUT | Crystal oscillator output                                                                      |

| 13                               | VDD_PLL      | POWER  | Analog supply for PLL                                                                          |

| 14                               | INV_CLK      | INPUT* | Invert clock select for QC3 & QC2. High = invert, Low = normal operation                       |

| 16, 18, 21, 23                   | QC[3:0]      | OUTPUT | Clock outputs (Bank C)                                                                         |

| 17, 22, 33,<br>37, 45, 49        | VDD          | POWER  | Power supply for outputs.                                                                      |

| 19, 20                           | FSEL_C[1:0]  | INPUT* | Bank C divide select pins.                                                                     |

| 25                               | QSYNC        | OUTPUT | Synchronization output for Bank A and Bank C.                                                  |

| 28                               | VDD          | POWER  | Power supply for core.                                                                         |

| 29                               | QFB          | OUTPUT | Feedback clock output                                                                          |

| 31                               | FB_IN        | INPUT* | Feedback input                                                                                 |

| 32, 34, 36, 38                   | QB[3:0]      | OUTPUT | Clock outputs (Bank B)                                                                         |

| 40, 41                           | FSEL_B[1:0]  | INPUT* | Bank B divide select pins.                                                                     |

| 42, 43                           | FSEL_A[1:0]  | INPUT* | Bank A divide select pins.                                                                     |

| 44, 46, 48, 50                   | QA[3:0]      | OUTPUT | Clock outputs (Bank A)                                                                         |

| 52                               | VCO_SEL      | INPUT* | VCO select. High = VCO/1, Low = VCO/2.                                                         |

<sup>\* 25</sup>K $\Omega$  pull-up resistor

# 1:12 LVCMOS PLL CLOCK GENERATOR

## 1.0 DEVICE SPECIFICATIONS

### **TABLE 1: GENERAL SPECIFICATIONS**

| SYMBOL             | CHARACTERISTICS                   | CONDITION | MIN  | TYP                | MAX | UNIT |

|--------------------|-----------------------------------|-----------|------|--------------------|-----|------|

| V <sub>TT</sub>    | Output Termination Voltage        |           |      | V <sub>DD</sub> ÷2 |     | V    |

| ESD <sub>MM</sub>  | ESD Protection (Machine model)    |           | 200  |                    |     | V    |

| ESD <sub>HBM</sub> | ESD Protection (Human body model) |           | 2000 |                    |     | V    |

| LU                 | Latch-up Immunity                 |           | 200  |                    |     | mA   |

| C <sub>IN</sub>    | Input capacitance                 | per input |      | 4                  |     | pf   |

### TABLE 2: ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | CHARACTERISTICS     | CONDITION | MIN  | TYP | MAX                   | UNIT |

|------------------|---------------------|-----------|------|-----|-----------------------|------|

| $V_{DD}$         | Supply Voltage      |           | -0.3 |     | 3.9                   | V    |

| V <sub>IN</sub>  | DC Input Voltage    |           | -0.3 |     | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OUT</sub> | DC Output Voltage   |           | -0.3 |     | V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>  | DC Input Current    |           |      |     | +/-20                 | mA   |

| I <sub>OUT</sub> | DC Output Current   |           |      |     | +/-50                 | mA   |

| T <sub>S</sub>   | Storage Temperature |           | -65  |     | 125                   | С    |

# TABLE 3: DC CHARACTERISTICS (V<sub>DD</sub> = 3.3V +/- 5%)

| SYMBOL              | CHARACTERISTICS          | CONDITION                         | MIN  | TYP    | MAX                   | UNIT |

|---------------------|--------------------------|-----------------------------------|------|--------|-----------------------|------|

| $V_{DD\_PLL}$       | PLL Supply Voltage       |                                   | 3.0  |        | $V_{DD}$              | V    |

| V <sub>IH</sub>     | Input High Voltage       |                                   | 2.0  |        | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>     | Input Low Voltage        |                                   |      |        | 0.8                   | V    |

| V <sub>OH</sub>     | Output High Voltage      | IOH = -24mA                       | 2.4  |        |                       | V    |

| V <sub>OL</sub>     | Output Low Voltage       | IOL = 24mA<br>IOL = 12mA          |      |        | 0.55<br>0.30          | V    |

| Z <sub>OUT</sub>    | Output Impedance         |                                   |      | 14 -17 |                       | Ω    |

| I <sub>PU</sub>     | Input Current            | $V_{IN} = GND \text{ or } V_{DD}$ | -100 |        | 200                   | μА   |

| I <sub>DD_PLL</sub> | PLL Supply Current       | @ V <sub>DD_PLL</sub> Pin         |      | 8      | 13.5                  | mA   |

| I <sub>DDQ</sub>    | Quiescent Supply Current | All V <sub>DD</sub> pins          |      |        | 35                    | mA   |

# TABLE 4: AC CHARACTERISTICS (V<sub>DD</sub> = 3.3V +/- 5%)

| SYMBOL                            | CHARACTERISTICS                        | CONDITION                            | MIN       | TYP | MAX       | UNIT |

|-----------------------------------|----------------------------------------|--------------------------------------|-----------|-----|-----------|------|

| f <sub>REF</sub>                  | Input reference frequency <sup>a</sup> | ÷4 feedback                          | 50.0      |     | 120       | MHz  |

|                                   |                                        | ÷6 feedback                          | 33.3      |     | 80.0      | MHz  |

|                                   |                                        | ÷8 feedback                          | 25.0      |     | 60.0      | MHz  |

|                                   |                                        | ÷10 feedback                         | 20.0      |     | 48.0      | MHz  |

|                                   |                                        | ÷12 feedback                         | 16.6      |     | 40.0      | MHz  |

|                                   |                                        | ÷16 feedback                         | 12.5      |     | 30.0      | MHz  |

|                                   |                                        | ÷20 feedback                         | 10.0      |     | 24.0      | MHz  |

|                                   |                                        | ÷24 feedback                         | 8.33      |     | 20.0      | MHz  |

|                                   |                                        | ÷32 feedback                         | 6.25      |     | 15.0      | MHz  |

|                                   |                                        | ÷40 feedback                         | 5.00      |     | 12.0      | MHz  |

|                                   |                                        | PLL bypass mode                      |           |     | 250       | MHz  |

| $f_{VCO}$                         | VCO frequency range                    |                                      | 200       |     | 480       | MHz  |

| f <sub>XTAL</sub>                 | Crystal input frequency range          |                                      | 10        |     | 25        | MHz  |

| f <sub>MAX</sub>                  | Output frequency <sup>a</sup>          | ÷2 output                            | 100.0     |     | 240.0     | MHz  |

|                                   |                                        | ÷4 output                            | 50.0      |     | 120.0     | MHz  |

|                                   |                                        | ÷6 output                            | 33.3      |     | 80.0      | MHz  |

|                                   |                                        | ÷8 output                            | 25.0      |     | 60.0      | MHz  |

|                                   |                                        | ÷10 output                           | 20.0      |     | 48.0      | MHz  |

|                                   |                                        | ÷12 output                           | 16.6      |     | 40.0      | MHz  |

|                                   |                                        | ÷16 output                           | 12.5      |     | 30.0      | MHz  |

|                                   |                                        | ÷20 output                           | 10.0      |     | 24.0      | MHz  |

|                                   |                                        | ÷24 output                           | 8.33      |     | 20.0      | MHz  |

| f <sub>STOP_CLK</sub>             | Serial interface max.<br>frequency     |                                      |           |     | 20.0      | MHz  |

| t <sub>PW</sub>                   | CLKx pulse min. width                  |                                      | 2.0       |     |           | ns   |

| It <sub>R</sub> , It <sub>F</sub> | Input CLKx Rise/Fall time              | 0.8V to 2.0V                         |           |     | 1.0       | ns   |

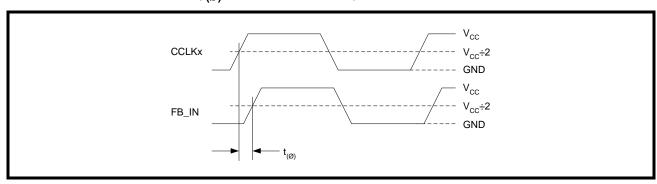

| t <sub>(∅)</sub>                  | Propagation Delay (static              | 6.25MHz < f <sub>REF</sub> < 65.0MHz | -3        |     | +3        | 0    |

| V= /                              | phase offset) CLKx to FB_INb           | 65.0MHz < f <sub>REF</sub> < 125MHz  | -4        |     | +4        | 0    |

|                                   |                                        | f <sub>REF</sub> = 50MHz & FB = ÷8   | -166      |     | +166      | ps   |

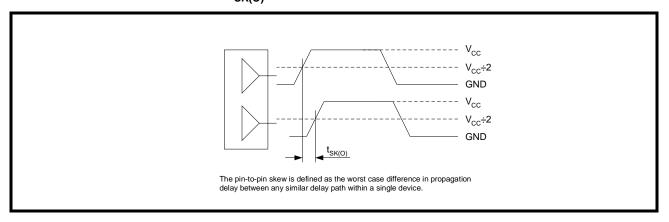

| t <sub>SK(O)</sub>                | Output to output skew <sup>c</sup>     | Bank A (QAx to QAy)                  |           |     | 100       | ps   |

| 5.1(5)                            |                                        | Bank B (QBx to QBy)                  |           |     | 100       | ps   |

|                                   |                                        | Bank C (QCx to QCy)                  |           |     | 100       | ps   |

|                                   |                                        | all outputs (QXy to QWz)             |           |     | 250       | ps   |

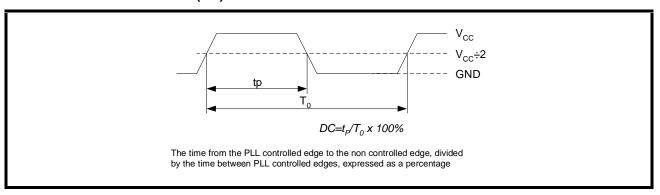

| DC                                | Output duty cycle <sup>d</sup>         |                                      | (T÷2)-200 | T÷2 | (T÷2)+200 | ps   |

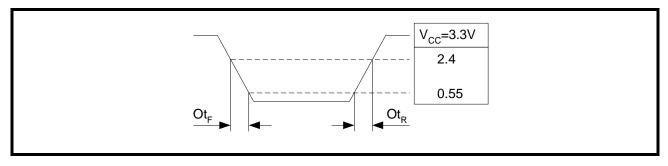

| Ot <sub>R</sub> , Ot <sub>F</sub> | Output Rise/Fall time                  | 0.55V to 2.4V                        | 0.1       |     | 1.0       | ns   |

# TABLE 5: AC CHARACTERISTICS (CON'T) (V<sub>DD</sub> = 3.3V +/- 5%)

| SYMBOL                             | CHARACTERISTICS                  | CONDITION                                                                                                                               | MIN | TYP                                                                                                                           | MAX                                                      | UNIT                                                        |

|------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| $t_{PLZ,} t_{PHZ}$                 | Output Disable Time              |                                                                                                                                         |     |                                                                                                                               | 8                                                        | ns                                                          |

| t <sub>PZL,</sub> t <sub>PZH</sub> | Output Enable Time               |                                                                                                                                         |     |                                                                                                                               | 8                                                        | ns                                                          |

| t <sub>JIT(CC)</sub>               | Cycle-to-Cycle Jitter            | All outputs in same divider configuration                                                                                               |     | 150                                                                                                                           | 200                                                      | ps                                                          |

| t <sub>JIT(PER)</sub>              | Period Jitter                    | All outputs in same divider configuration                                                                                               |     |                                                                                                                               | 150                                                      | ps                                                          |

| t <sub>JIT(I/O)RMS</sub>           | I/O Jitter (RMS)<br>VCO @ 400MHz | ÷4 feedback  ÷6 feedback  ÷8 feedback  ÷10 feedback  ÷12 feedback  ÷16 feedback  ÷20 feedback  ÷24 feedback  ÷32 feedback  ÷40 feedback |     |                                                                                                                               | 11<br>86<br>13<br>88<br>16<br>19<br>21<br>22<br>27<br>30 | ps<br>ps<br>ps<br>ps<br>ps<br>ps<br>ps<br>ps                |

| BW                                 | PLL closed loop bandwidth        | ÷4 feedback ÷6 feedback ÷8 feedback ÷10 feedback ÷12 feedback ÷16 feedback ÷20 feedback ÷24 feedback ÷32 feedback ÷40 feedback          |     | 1.20-3.5<br>0.70-2.50<br>0.50-1.80<br>0.45-1.20<br>0.30-1.00<br>0.25-0.70<br>0.20-0.55<br>0.17-0.40<br>0.12-0.30<br>0.11-0.28 |                                                          | MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz |

| t <sub>LOCK</sub>                  | Max PLL Lock Time                |                                                                                                                                         |     |                                                                                                                               | 10                                                       | ns                                                          |

#### NOTES:

- a. PLL locked, except when configured in bypass mode.

- **b.**  $t_{(\emptyset)}[s] = t_{(\emptyset)}[^{\circ}] \div (\text{fref x 360}^{\circ})$

- c. Not including Qsync output

- **d.** T is the output period.

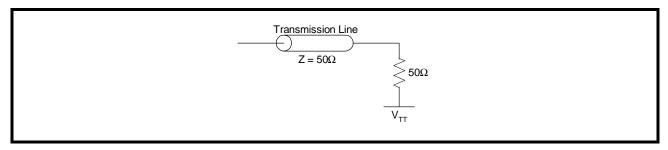

### FIGURE 3. TEST LOAD

### 2.0 CONFIGURATION TABLES

**TABLE 6: FUNCTION CONTROLS**

| CONTROL PIN | Logic 0                                                                                                                           | Logic 1                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| MR/OE       | Resets the output divide circuitry and serial interface, tri-states all outputs                                                   | Enables all outputs - normal operation            |

| PLL_SEL     | PLL bypass mode enabled. This is a test mode in which the reference clock is provided to the output dividers in place of the VCO. | PLL enabled - normal operation                    |

| REF_SEL     | CLKx selected as ref source to PLL                                                                                                | Crystal Oscillator selected as ref source to PLL. |

| CLK_SEL     | CLK0 selected                                                                                                                     | CLK1 selected                                     |

| INV_CLK     | QC2 & QC3 are in phase with QC1 & QC4                                                                                             | QC2 & QC3 are 180° out of phase with QC1 & QC4    |

| VCO_SEL     | VCO ÷ 2                                                                                                                           | no divide of VCO                                  |

TABLE 7: BANK OUTPUT DIVIDER CONTROLS

| INI     | PUT     | OUTPUT | INF     | PUT     | OUTPUT | INF     | PUT     | OUTPUT |

|---------|---------|--------|---------|---------|--------|---------|---------|--------|

| FSEL_A1 | FSEL_A0 | QA     | FSEL_B1 | FSEL_B0 | QB     | FSEL_C1 | FSEL_C0 | QC     |

| 0       | 0       | ÷4     | 0       | 0       | ÷4     | 0       | 0       | ÷2     |

| 0       | 1       | ÷6     | 0       | 1       | ÷6     | 0       | 1       | ÷4     |

| 1       | 0       | ÷8     | 1       | 0       | ÷8     | 1       | 0       | ÷6     |

| 1       | 1       | ÷12    | 1       | 1       | ÷10    | 1       | 1       | ÷8     |

TABLE 8: FEEDBACK DIVIDER CONTROL

| FSEL_FB2 | FSEL_FB1 | FSEL_FB0 | QFB |

|----------|----------|----------|-----|

| 0        | 0        | 0        | ÷4  |

| 0        | 0        | 1        | ÷6  |

| 0        | 1        | 0        | ÷8  |

| 0        | 1        | 1        | ÷10 |

| 1        | 0        | 0        | ÷8  |

| 1        | 0        | 1        | ÷12 |

| 1        | 1        | 0        | ÷16 |

| 1        | 1        | 1        | ÷20 |

## 3.0 QSYNC TIMING

#### FIGURE 4. QSYNC TIMING DIAGRAM

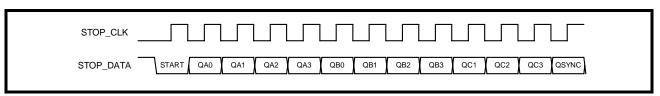

#### XRK69772 INDIVIDUAL OUTPUT DISABLE (STOP CLOCK) CIRCUITRY

The user can write to the serial input register through the STOP\_DATA input by supplying a logic '0' start bit followed serially by 12 NRZ disable/enable bits. The period of each STOP\_DATA bit equals the period of the free-running STOP\_CLK signal. The STOP\_DATA serial transmission should be timed so the XRK69772 can sample each STOP\_DATA bit with the rising edge of the free-running STOP\_CLK signal. A logic "0" to any stop bit location will disable the corresponding device output while a logic "1" will enable. All outputs are by default, enabled.

FIGURE 5. STOP CLOCK CIRCUIT PROGRAMMING

# FIGURE 6. OUTPUT-TO-OUTPUT SKEW $t_{SK(O)}$

Figure 7. Propogation delay  $(t_{(\emptyset)},$  static phase offset) test reference

### FIGURE 8. OUTPUT DUTY CYCLE (DC)

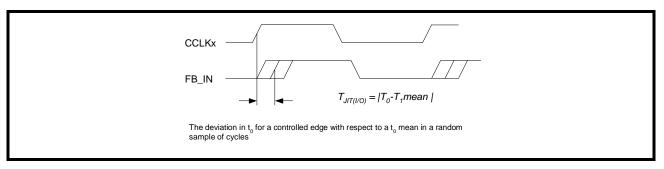

#### FIGURE 9. I/O JITTER

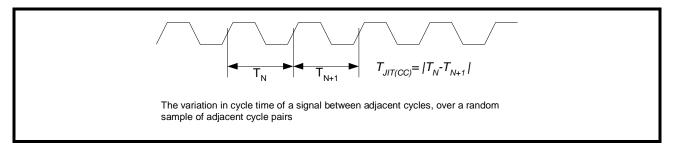

#### FIGURE 10. CYCLE-TO-CYCLE JITTER

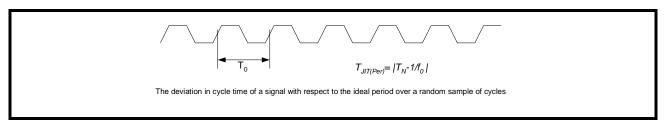

### FIGURE 11. PERIOD JITTER

### FIGURE 12. OUTPUT TRANSITION TIME TEST REFERENCE

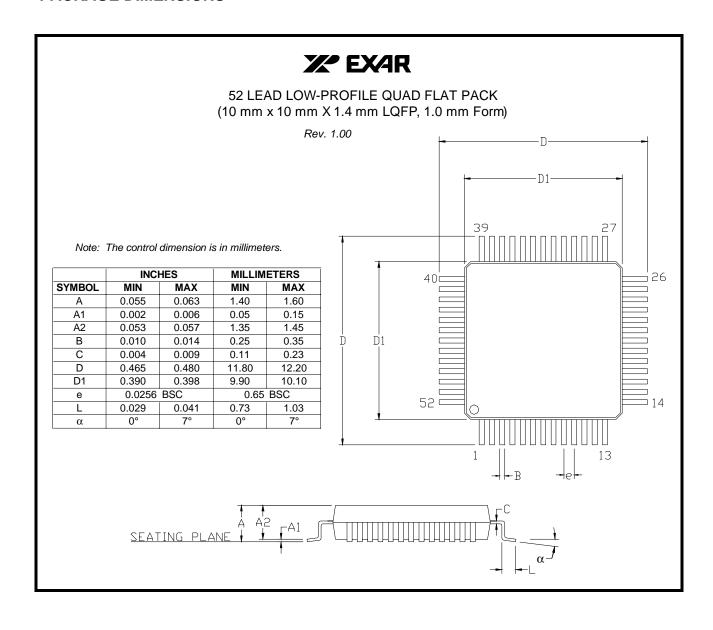

### **PACKAGE DIMENSIONS**

#### **REVISION HISTORY**

| REVISION # | DATE          | DESCRIPTION      |

|------------|---------------|------------------|

| P1.0.0     | April 6, 2006 | Initial release. |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

|            |               |                  |

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2006 EXAR Corporation

Datasheet April 2006.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.