# **FUJITSU**

#### 930 Series 32-BIT RISC EMBEDDED PROCESSOR

June 1996

#### **FEATURES**

- 50 MHz operating frequency, 40 MHz operating frequency when FIFO is used

- SPARC\* high performance RISC architecture

- High Performance SPARC FPU, ANSI/IEEE 754 compatible

- 8 Kbytes 2-way set associative instruction cache

- 2 Kbytes 2-way set associative data cache

- High Bandwidth synchronous DRAM (SDRAM) interface

- 6 on-chip FIFOs which can be used as source and destination for FPU operations

- 2 channel DMA controller capable of transferring data to and from the FIFOs

- Support for burst mode cache fills

- Flexible locking mechanism for data and instruction cache entries

- Harvard-style separate instruction and data buses onchip

- 8 window, 136 word register file

- Fast interrupt response time

- 247 address spaces, 4 Gbyte each

- Bus Interface Unit runs at half the 50/40 MHz processor speed

- Buffered writes and instruction pre-fetching

- Fast page-mode DRAM support

- Support for execution out of 8, 16, or 32-bit wide boot memory

- · Parity generation and checking

- Programmable address decoder and wait-state generator

- 16-bit auto reload timer

- JTAG test interface

- Emulator support hardware

- Single vector trapping

- Power down modes

- 0.5 micron gate, 3 level metal CMOS technology, 3.3V internal and 3.3V/5V I/O

#### **GENERAL DISCUSSION**

The MB86934 is the fifth of the 930 series of RISC processors which offers high performance and high integration for a wide range of embedded applications. The processor is based on the SPARC architecture and is upward code compatible with previous implementations. At 50 MHz, the processor executes with 50 MIPs peak and 46 MIPs sustained performance.

The FPU implemented on the MB86934 is compatible with ANSI/IEEE-754-1985. It is also fully compatible with Ver. 8 SPARC FPU. To improve the performance of the chip, the MB86934 supports "Enhanced Floating Point Operations". These operations can have their operands in 6 on-chip FIFOs or the floating point registers. The on-chip FIFOs decouple the FPU from external memory latency. Using the Enhanced Floating Point operations, the FIFOs and SDRAMs the MB86934 can perform single precision floating point operations at the rate of 40 MFLOPS, at 40 MHz.

The SDRAM interface allows the MB86934 to interface to SDRAMs, which can provide data at the peak rate of 400 MBytes/sec.

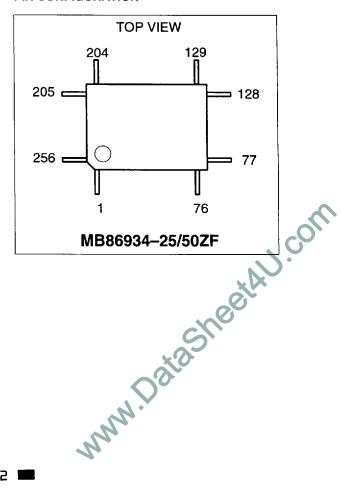

#### **PIN CONFIGURATION**

#### **PIN CONFIGURATIONS**

| PIN<br>NO. | PIN NAME TYPE | PIN<br>NO. | PIN NAME TYPE | PIN<br>NO. | PIN NAME TYPE      | PIN<br>NO. | PIN NAME TYPE  |

|------------|---------------|------------|---------------|------------|--------------------|------------|----------------|

| 1          | D<40>         | 55         | IRL<1>        | 109        | VSS                | 163        | VSS            |

| 2          | D<41>         | 56         | IRL<2>        | 110        | IO_VDD             | 164        | IO_VDD         |

| 3          | VSS           | 57         | IRL<3>        | 111        | VSS                | 165        | -SCS0          |

| 4          | VDD           | 58         | TDO           | 112        | VDD                | 166        | -SCS1          |

| 5          | VSS           | 59         | TRST          | 113        | ADR<18>            | 167        | -SCS2          |

| 6          | D<42>         | 60         | TDI           | 114        | ADR<10><br>ADR<19> | ı          |                |

| 7          | D<43>         | 61         | TMS           | 115        |                    | 168        | -SCS3          |

| 8          | IO VDD        | 62         | TCK           |            | ADR<20>            | 169        | -SCAS          |

| 9          | VSS           | 63         | EMU_SD<3>     | 116        | ADR<21>            | 170        | VSS            |

| 10         | D<44>         | 64         |               | 117        | ADR<22>            | 171        | -SRAS          |

| 11         | D<45>         | 1          | EMU_SD<2>     | 118        | ADR<23>            | 172        | -OE            |

| 12         |               | 65         | EMU_SD<1>     | 119        | VSS                | 173        | -NVWE          |

|            | D<46>         | 66         | EMU_SD<0>     | 120        | IO_VDD             | 174        | -ERROR         |

| 13         | D<47>         | 67         | EMU_VDD       | 121        | ADR<24>            | 175        | -LOCK          |

| 14         | VSS           | 68         | VSS           | 122        | ADR<25>            | 176        | -BGRNT         |

| 15         | VDD           | 69         | EMU_D<3>      | 123        | ADR<26>            | 177        | -PBREQ         |

| 16         | D<48>         | 70         | EMU_D<2>      | 124        | ADR<27>            | 178        | VSS            |

| 17         | D<49>         | 71         | EMU_D<1>      | 125        | ADR<28>            | 179        | IO_VDD         |

| 18         | D<50>         | 72         | EMU_D<0>      | 126        | ADR<29>            | 180        | -BMREQ         |

| 19         | IO_VDD        | 73         | -EMU_ENB      | 127        | ADR<30>            | 181        | VSS            |

| 20         | VSS           | 74         | -EMU_BRK      | 128        | VSS                | 182        | VDD            |

| 21         | D<51>         | 75         | VDD           | 129        | VDD                | 183        | RD/ <b>–WR</b> |

| 22         | D<52>         | 76         | VSS           | 130        | ADR<31>            | 184        | -AS            |

| 23         | D<53>         | 77         | -DACK0        | 131        | ASI<0>             | 185        | VSS            |

| 24         | VSS           | 78         | -EOP0         | 132        | ASI<1>             | 186        | VDD            |

| 25         | VDD           | 79         | -DREQ0        | 133        | VSS                | 187        | -READYOUT      |

| 26         | D<54>         | 80         | -DACK1        | 134        | IO_VDD             | 188        | -READY         |

| 27         | D<55>         | 81         | VSS           | 135        | ASI<2>             | 189        | -MEXC          |

| 28         | D<56>         | 82         | IO_VDD        | 136        | ASI<3>             | 190        | -BMACK         |

| 29         | D<57>         | 83         | -EOP1         | 137        | -BE3               | 191        | VSS            |

| 30         | IO_VDD        | 84         | -DREQ1        | 138        | -BE2               | 192        | VDD            |

| 31         | VSS           | 85         | ADR<2>        | 139        | -BE1               | 193        | -BREQ          |

| 32         | D<58>         | 86         | ADR<3>        | 140        | –BE0               | 194        | -RESET         |

| 33         | D<59>         | 87         | ADR<4>        | 141        | -SAME_PAGE         | 195        | -PDRESET       |

| 34         | D<60>         | 88         | ADR<5>        | 142        | –CS0               | 196        | D<0>           |

| 35         | D<61>         | 89         | VSS           | 143        | –CS1               | 197        | D<1>           |

| 36         | D<62>         | 90         | VDD           | 144        | -CS2               | 198        | D<2>           |

| 37         | VSS           | 91         | VSS           | 145        | VSS                | 199        | VSS            |

| 38         | VDD           | 92         | IO_VDD        | 146        | IO_VDD             | 200        | IO_VDD         |

| 39         | D<63>         | 93         | ADR<6>        | 147        | -CS3               | 201        | D<3>           |

| 40         | PARITY<0>     | 94         | ADR<7>        | 148        | VSS                | 202        | D<4>           |

| 41         | IO_VDD        | 95         | ADR<8>        | 149        | VDD                | 203        | D<5>           |

| 42         | VSS           | 96         | ADR<9>        | 150        | -CS4               | 204        | VDD            |

| 43         | PARITY<1 >    | 97         | ADR<10>       | 151        | XTAL2              | 205        | VSS            |

| 44         | PARITY<2>     | 98         | VSS           | 152        | XTAL1 / CLKIN      | 206        | D<6>           |

| 45         | PARITY<3>     | 99         | VDD           | 153        | CLKOUT1            | 207        | D<7>           |

| 46         | -TIMER_OVF    | 100        | ADR<11>       | 154        | CLKOUT2            | 208        | D<8>           |

| 47         | BIUCLOCK      | 101        | VSS           | 155        | A_VSS              | 209        | D<9>           |

| 48         | -CLKDBL       | 102        | IO_VDD        | 156        | A_VDD              | 210        | VDD            |

| 49         | CLK_ECB       | 103        | ADR<12>       | 157        | VSS                | 211        | VSS            |

| 50         | -BMODE8       | 104        | ADR<13>       | 158        | VDD                | 212        | D<10>          |

| 51         | -BMODE16      | 105        | ADR<14>       | 159        | SCKE               | 213        | VSS            |

| 52         | IRL<0>        | 106        | ADR<15>       | 160        | -SWE               | 214        | IO_VDD         |

| 53<br>54   | VSS           | 107        | ADR<16>       | 161        | SDQM0              | 215        | D<11>          |

|            | VDD           | 108        | ADR<17>       | 162        | SDQM1              | 216        | D<12>          |

#### **PIN CONFIGURATIONS**

| PIN<br>NO. | PIN NAME TYPE |

|------------|---------------|------------|---------------|------------|---------------|------------|---------------|

| 217        | D<13>         | 227        | D<19>         | 237        | VSS           | 247        | D<33>         |

| 218        | D<14>         | 228        | D<20>         | 238        | IO VDD        | 248        | D<34>         |

| 219        | D<15>         | 229        | D<21>         | 239        | D<27>         | 249        | VSS           |

| 220        | VDD           | 230        | D<22>         | 240        | D<28>         | 250        | IO VDD        |

| 221        | VSS           | 231        | D<23>         | 241        | D<29>         | 251        | D<35>         |

| 222        | D<16>         | 232        | VDD           | 242        | D<30>         | 252        | D<36>         |

| 223        | D<17>         | 233        | VSS           | 243        | D<31>         | 253        | D<37>         |

| 224        | D<18>         | 234        | D<24>         | 244        | D<32>         | 254        | D<38>         |

| 225        | VSS           | 235        | D<25>         | 243        | VDD           | 255        | D<39>         |

| 226        | IO_VDD        | 236        | D<26>         | 246        | VSS           | 256        | IO_VDD        |

NOTE:

① PIN47(BIUCLOCK) must be tied to I/O\_VDD.

NOTE:

② PIN49 (CLK\_ECB) must be tied to VSS.

NOTE:

③ PIN155 (A\_VSS) and PIN156 (A\_VDD) must be very clean.

If necessary, use LC type Low-pass Filter.

NOTE:

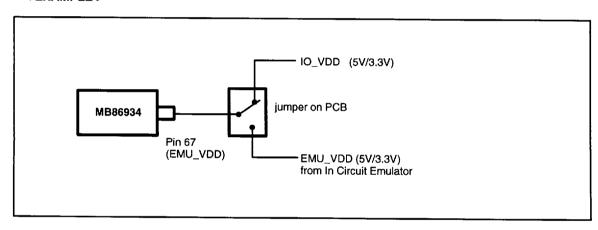

④ PIN67 (EMU\_VDD) must be tied to IO\_VDD when in circuit emulator is not used as shown below.

#### < EXAMPLE >

#### **ORDERING CODE**

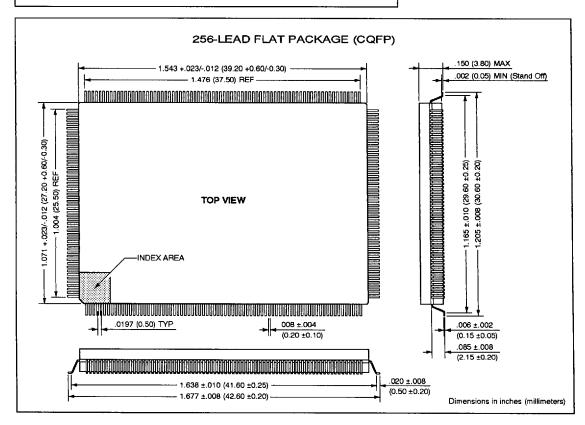

| Clock Frequency (MHz) | Ordering Code      | Package Type |

|-----------------------|--------------------|--------------|

| 25/50                 | MB86934-25/50ZFVES | 256-Pin CQFP |

On-chip data and instruction caches are included to help decouple the processor from external memory latency. Separate on-chip instruction and data paths provide a high bandwidth interface between the IU and caches. An on-chip 2-channel DMA controller makes use of the processor bus even while the integer unit or floating point unit are executing out of cache. Included to maximize the performance of the system with minimum glue logic, are chip select outputs, programmable wait state generation, built-in support for connection to page-mode DRAM and support for booting from 8 and 16-bit memory. See

MB86934 block diagram.

Support for debug and diagnostic tools has been included on-chip and allows for direct connection to hardware emulators and improves debug capability when using ROM based monitors.

These features combine to give the MB86934 superior speed, flexibility and efficiency to make it the ideal choice for a wide variety of low cost, high performance embedded systems.

Figure 1: BLOCK DIAGRAM OF MB86934 DEBUG SUP-ICACHE DCACHE **EMULATOR** ΙU PORT UNIT **8 KBYTES** 2 KBYTES 32 DD 64 64 64 64 32 DMA BIU CONTROL SDRAM 64 DATA Interface DRAM SUPPORT INTERFACE TO 16-BIT TIMER MB8693x BUS ADDRESS DECODE WAIT STATE GENERATOR ADR/CONTROL 64 DATA

#### SIGNAL DESCRIPTIONS<sup>1</sup>

| SYMBOL                        | TYPE                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

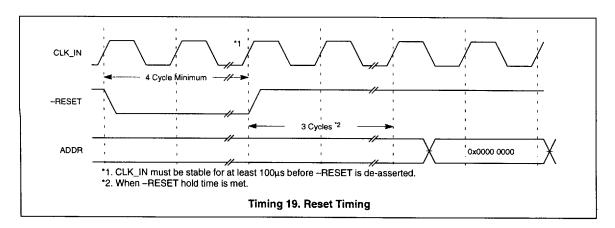

| -RESET                        | I                         | SYSTEM RESET: Asserting reset for at least 4 processor cycles after the clock has stabilized, causes the MB86934 to be initialized.                                                                                                                                                                                                                                                                                                                                                                                   |  |

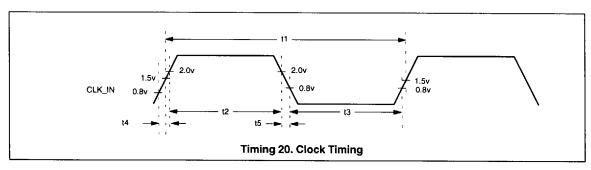

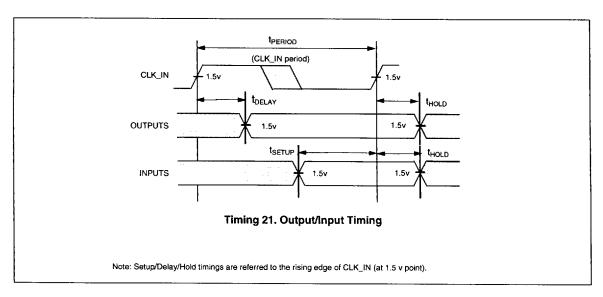

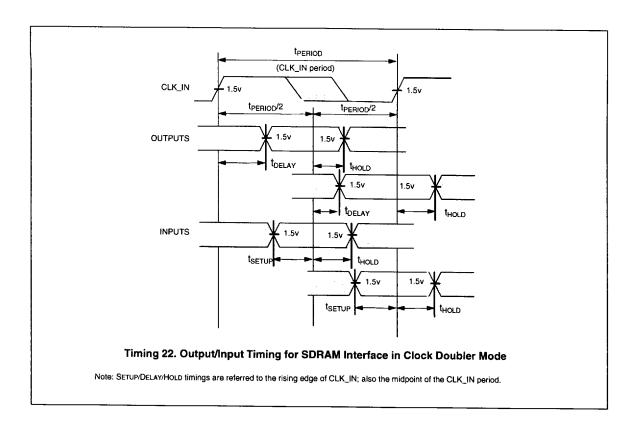

| CLK_IN (XTAL1)                | 1                         | <b>EXTERNAL OSCILLATOR:</b> The frequency of the CLK_IN input determines the frequency of operation of the bus. The internal frequency of operation of the part is a function of the frequency of the CLK_IN signal and the -CLKDBL signal.                                                                                                                                                                                                                                                                           |  |

| XTAL2,<br>CLKOUT1,<br>CLKOUT2 | 0                         | CLOCK OUTPUTS: These signals are used for chip testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

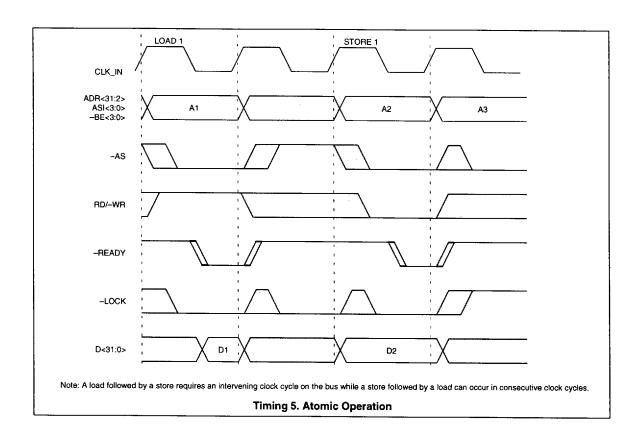

| -LOCK                         | O<br>S(L)<br>G(Z)<br>I(1) | BUS LOCK: This is a control signal asserted by the processor to indicate to the syste that the current bus transaction requires more than one transfer on the bus. The Atom Load Store instruction for example requires contiguous bus transactions which cau the assertion of the bus lock signal. The bus may not be granted to another bus owner long as –LOCK is active. –LOCK is asserted with the assertion of AS as remains actiuntil –READY is asserted at the end of the locked transaction.                 |  |

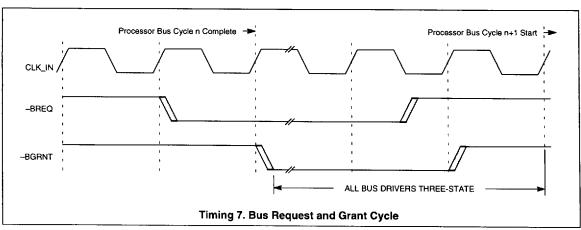

| -BREQ                         | I<br>S(L)                 | BUS REQUEST: Asserted by another device on the bus to indicate that it wants ownership of the bus. The request must be answered with a bus grant (-BGRNT) from the MB86934 before the device can proceed by driving the bus. Once the bus has been granted, the device has ownership of the bus until it de-asserts -BREQ. The user should ensure that devices on the bus cannot monopolize the bus to the exclusion of the CPU. Inputs to -BREQ while -RESET is active are valid and cause Bus Grant to be asserted. |  |

| -BGRNT                        | O<br>S(L)<br>G(0)<br>I(Q) | BUS GRANT: Asserted by the CPU in response to a request from a device wanting ownership of the bus. The CPU grants the bus to other devices only after all transfers for the current transaction are completed. All bus drivers are three-stated with the assertion of the bus grant signal.                                                                                                                                                                                                                          |  |

| -ERROR                        | O<br>S(L)<br>G(Q)<br>I(Q) | ERROR SIGNAL: Asserted by the CPU to indicate that it has halted in an error state as a result of encountering a synchronous trap while traps are disabled. In this situation the CPU saves the PC and nPC registers, sets the the tt value in the TBR, enters into an error state and asserts the –ERROR signal. The system can monitor the –ERROR pin and initiate a reset under the error condition. This pin is high on reset.                                                                                    |  |

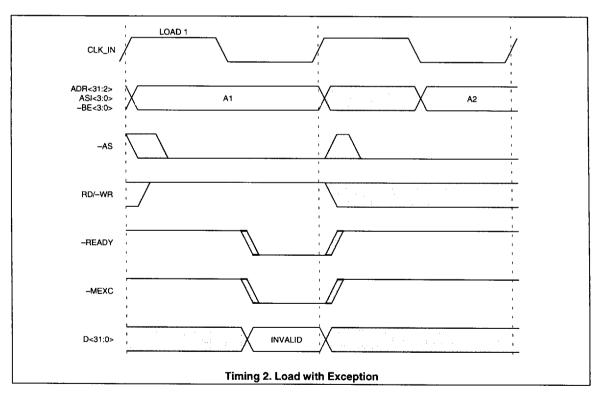

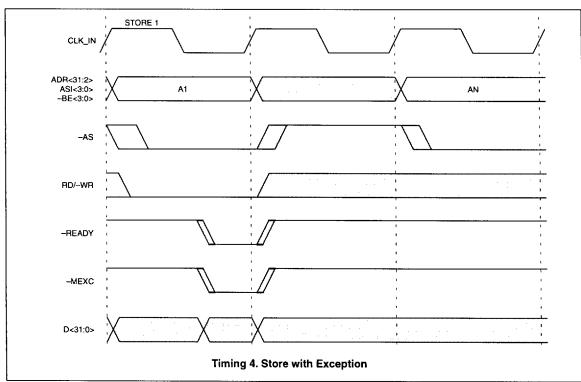

| -MEXC                         | S(L)                      | <b>MEMORY EXCEPTION:</b> Asserted by the memory system to indicate a memory error on either a data or instruction access. Assertion of this signal initiates wither a data or instruction access exception trap in the IU. The current bus access is invalidated by asserting the –MEXC in the same cycle as the –READY signal. The IU ignores the contents of the data bus in cycles where –MEXC is asserted.                                                                                                        |  |

| IRL <3:0>                     | A(L)                      | INTERRUPT REQUEST BUS: The value on these pins defines the external interrupt level. IRL <3:0>=1111 forces a non-maskable interrupt. IRL value of 0000 indicates no pending interrupts. All other values indicate maskable interrupts as enabled in the PIL field of the processor status register (PSR). Interrupts should be latched and prioritized by external logic and should be held pending until acknowledged by the processor.                                                                              |  |

| SYMBOL                             | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -TIMER_OVF                         | O<br>S(L)<br>G(Q)<br>I(Q)   | <b>TIMER UNDERFLOW:</b> Asserted by the processor to indicate that the internal 16-bit timer has underflowed. This signal can be used to initiate a DRAM refresh cycle of a one cycle periodic waveform. On reset, the timer is turned off and -TIMER_OVF is high.                                                                                                                                                                                                                                                                                                                     |  |  |

| -SAME_PAGE                         | O<br>S(L)<br>G(1)<br>I(1)   | SAME-PAGE DETECT: The —SAME_PAGE signal is used to take advantage of fast consecutive accesses within the same page for Fast Page Mode DRAMs. This signal is an output which is asserted when the current access in the region defined by chip select 4 is in the same page as the previous access to chip select 4. The page size is specified by writing it the SAME_PAGE MASK register.                                                                                                                                                                                             |  |  |

| -CS0, -CS1,<br>-CS2, -CS3,<br>-CS4 | O<br>S(L)<br>G(1)<br>I(1)   | CHIP SELECTS: These outputs are asserted when the value on the bus matches the address range in one of the corresponding ADDRESS RANGE registers. The signals are used to decode the current address into one of five address ranges. Address ranges should not overlap. Each address range has a corresponding wait specifier which is used to automatically assert internal ready after a user defined number of bus clock cycles. This allows a variety of memory and I/O devices with different access times to be connected to the MB86934 without the need for additional logic. |  |  |

| ADR <31:2>                         | I/O<br>S(L)<br>G(Z)<br>I(1) | ADDRESS BUS: The 30-bit ADDRESS BUS (A31-A2) is an output which identifies the data or instruction address of a 32-bit word. Reads are always one word in size while byte, half—word, or word transaction sizes for writes is identified by separate byte-enable signals (–BE0-3). The address bus is valid for the duration of the bus transaction. ADR<15:2> are shared by the SDRAM interface.                                                                                                                                                                                      |  |  |

| ASI <3:0>                          | I/O<br>S(L)<br>G(Z)<br>I(1) | ADDRESS SPACE IDENTIFIERS: The ADDRESS SPACE IDENTIFIERS are outputs which indicate to which of 256 available spaces the current ADDRESS BUS value corresponds. ASI values are defined as follows:    ASI                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                    |                             | instructions such as Load Alternate and Store Alternate. The ASI value is available in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| SYMBOL   | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

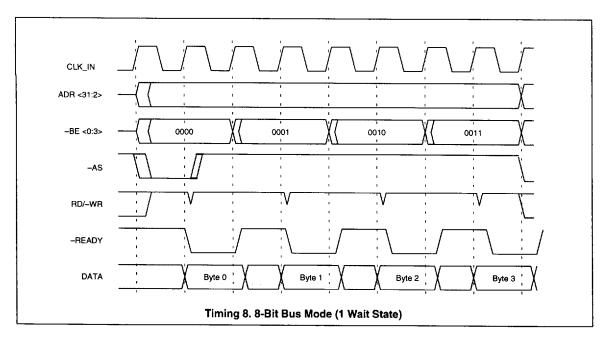

| -BMODE8  | S(L)                        | 8-BIT BOOT MODE: This signal is sampled during reset and causes read accesses, memory mapped to –CS0, to assume 8-bit memory. The MB86934 generates four sequential fetches to assemble a complete instruction or data word before continuing. Bytes are fetched in sequence (0,1,2,3) as encoded by –BE[2] and –BE[3] (00, 01, 10, 11). Writes to –CS0 are unaffected by boot mode selection and if left unconnected, a weak pull-up on this pin (and –BMODE16 pin) causes the processor to default to 32-bit mode.  Note: BMODE8 and BMODE16 should not be asserted at the same time.                                                                                                                                                                                                                                                                                                                                                      |  |  |

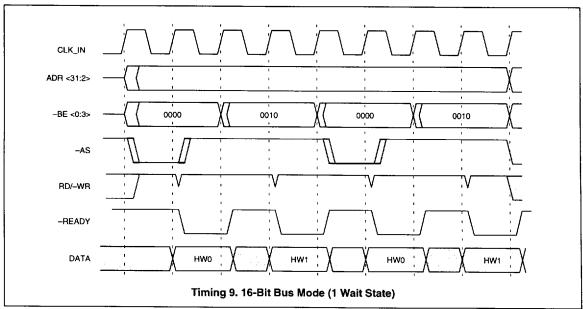

| -BMODE16 | I<br>S(L)                   | 16-BIT BOOT MODE: This signal is sampled during reset and causes read accesses, memory mapped to -CS0, to assume 16-bit memory. The MB86934 generates two sequential fetches to assemble a complete instruction or data word before continuing. Half words are fetched in sequence (0,1) as encoded by -BE[2]. Writes to -CS0 are unaffected by boot mode selection. If left unconnected, a weak pull-up on this pin (and -BMODE8 pin) causes the processor to default to 32-bit mode.  Note: BMODE8 and BMODE16 should not be asserted at the same time.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| -BE3-0   | O<br>S(L)<br>G(Z)<br>I(O)   | BYTES ENABLES: These pins indicate whether the current store transaction is a byte, half-word or word transaction. —BE0-3 signals are available in the same cycle in which the corresponding address value is asserted on the address bus and is valid for the duration of the bus transaction. This bus should be used only to qualify store transactions. For load transactions all sub-word requests are read (and replaced in the cache) as words and then the appropriate byte or half-word is extracted by the integer unit  Possible values for —BE3-0 are a follows:  Byte Writes Half-Word Writes Word Writes Word Writes Word Writes  BE<2:3> are also used in 8 and 16-bit ROM accesses as follows:  Bus Mode Byte BE<2:3> B-bit 0 0 00 1 01 2 10 3 11 16-bit 0&1 2 10 3 11 16-bit 0&1 283 10                                                                                                                                     |  |  |

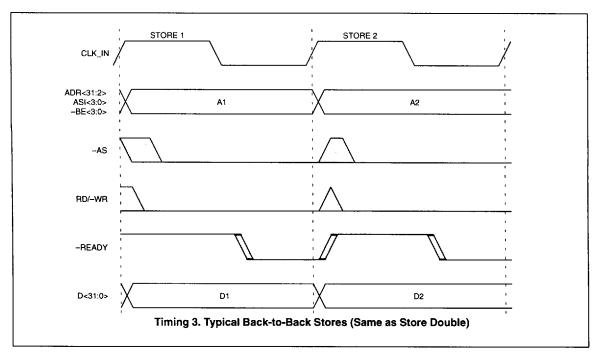

| D <63:0> | I/O<br>S(L)<br>G(Z)<br>I(1) | DATA BUS: The bus interface has 32 bi-directional data pins D<31:> to transfer data in thirty-two bit quantities. D(31) corresponds to the most significant bit if the least significant byte of the 32-byte word.  In write bus cycles, the point at which data is driven onto the bus depends on the type of the preceding cycle. If the preceding cycle was a write, data is driven in the cycle immediately following the cycle in which—READY was asserted. If the preceding cycle was a read, data is driven one cycle after the cycle in which—READY was asserted to minimize bus contention between the processor and the system.  Pins D<7:0> are used when the 8-bit boot mode is enabled and D<15:0> are used when16-bit mode is enabled.  the SDRAM interface has 64 bidirectional pins D<63:0>. D<63:32> are used exclusively by the SDRAM interface. D<31:0> are shared by the SDRAM interface with the MB8693x bus interface. |  |  |

7

| SYMBOL   | TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

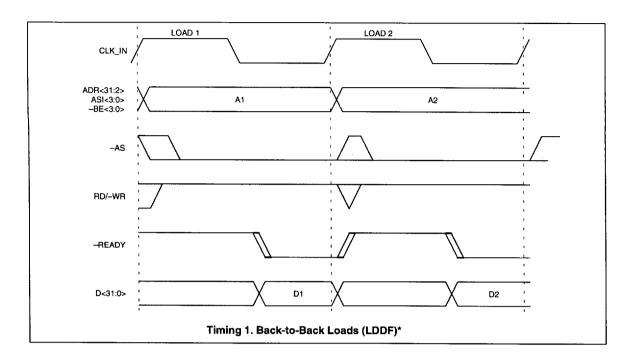

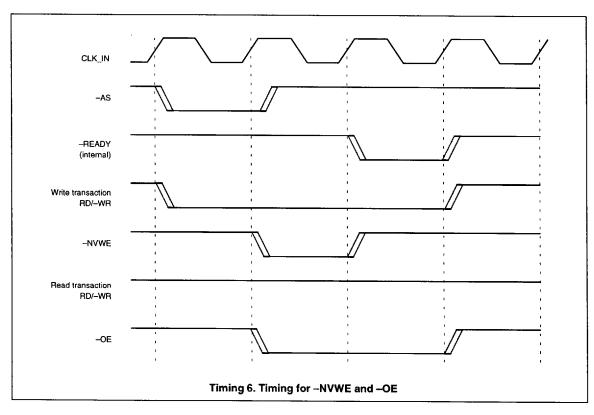

| -AS      | I/O<br>S(L)<br>G(Z)<br>I(1) | ADDRESS STROBE: A control signal asserted by the MB86934 or other bus master to indicate the start of a new bus transaction. A bus transaction begins with the assertion of —AS and ends with the assertion of —READY. —AS remains asserted for 1 clock cycle. During cycles in which neither the processor nor another bus master is driving the bus the bus is idle, and —AS remains de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| RD/WR    | I/O<br>S(L)<br>G(Z)<br>I(1) | <b>READ/WRITE TRANSACTION:</b> This signal specifies whether the current but ransaction is a read or a write operation. When –AS is asserted and RD/–WR is low then the current transaction is a write. With –AS asserted and RD/–WR high, the curre transaction is a read, RD/–WR remains active for the duration of the bus transaction aris de-asserted with the assertion of –READY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| -READY   | I<br>S(L)                   | READY: This is a control signal asserted by the external memory system to indicate that the current bus transaction is being completed and that it is ready to start with the next bus transaction in the following cycle. In case of a fetch from memory, the processor will strobe the value on the data bus at the rising edge CLK_IN following the assertion of —READY. For the case of a write, the memory system will assert —READY when the appropriate access time has been met. In most cases, no additional logic is required to generate the —READY signal. On-chip circuitry can be programmed to assert —READY internally based on the address of the current transaction. The external system can override the internal ready generator to terminate the current bus cycle early. Up to 6 address ranges each with different transaction times can be programmed. |  |  |

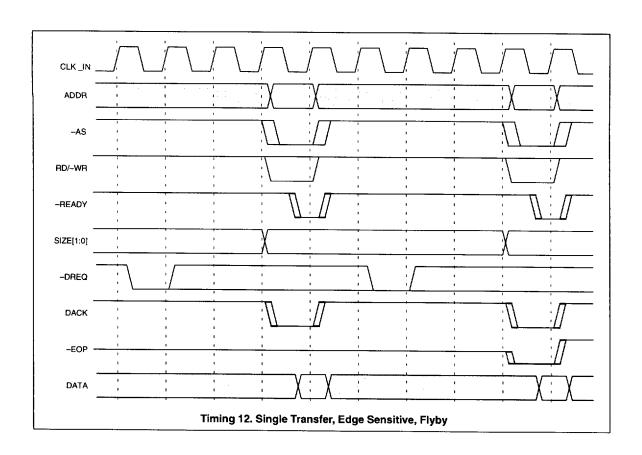

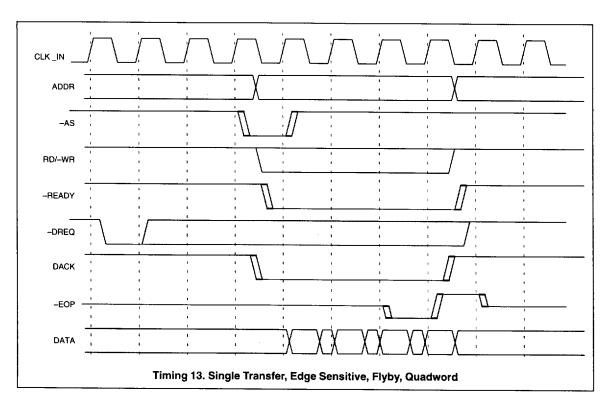

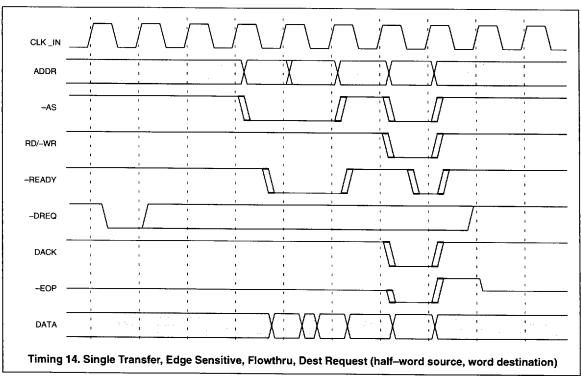

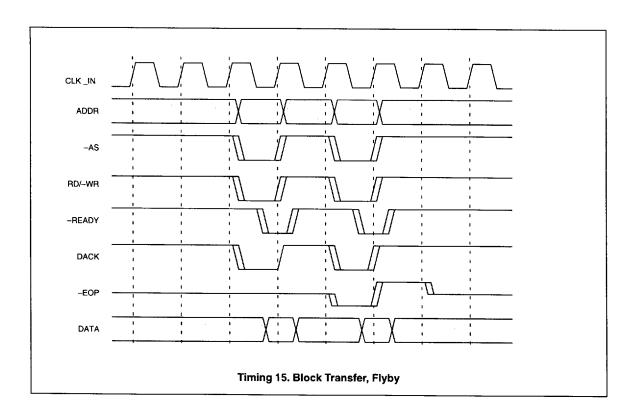

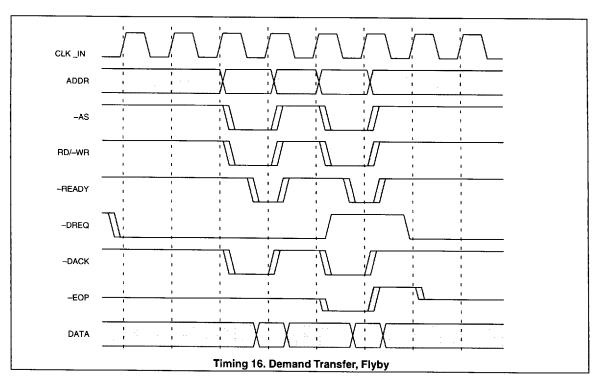

| -DREQ0-1 | A(L)                        | DMA REQUEST: Indicates that an external device is requesting a DMA transfer. This signal is edge sensitive for single transfers and level sensitive for demand transfer.  -DREQ0 corresponds to DMA channel 0, while -DREQ1 corresponds to DMA channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| -DACK0-1 | O<br>S(L)                   | DMA ACKNOWLEDGE: This is asserted when an external device asserts –DREQ and the processor accesses the external device. –DACK1 corresponds to DMA channel 0, while –DACK1 corresponds to DMA channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| –EOP0-1  | I/O<br>S(L)                 | END OF PROCESS: The signal is asserted by the external device when it wants to terminate a DMA transfer. Alternately, the processor drives this signal when the byte count reaches zero.—EOP0 corresponds to DMA channel 0, while—EOP1 corresponds to DMA channel 1. A pull-up holds—EOP0-1 high when it is not being driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| -PBREQ   | O<br>S(L)                   | PROCESSOR BUS REQUEST: This signal is asserted by the processor to indicate to an external bus arbiter that it needs to regain control of the bus. This provides a hand shake between the arbiter and the processor to allow the bus to be allocated based on demand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

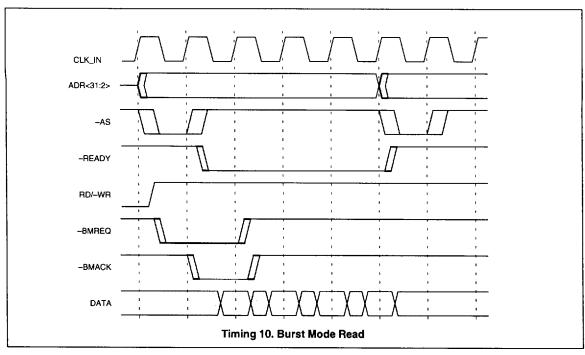

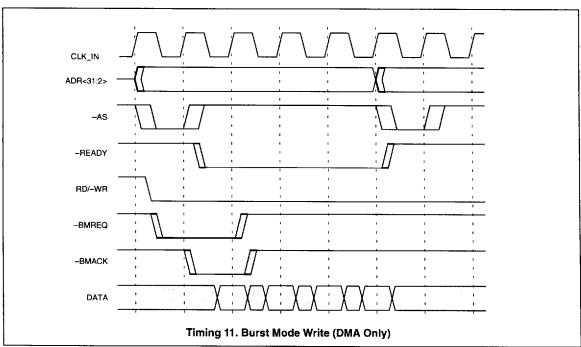

| -BMREQ   | O<br>S(L)                   | BURST MODE REQUEST: This signal is asserted by the processor to indicate to an external system that the processor's burst mode is enabled and the current transaction can be a burst. If the external system supports burst mode, it asserts –BMACK concurrently with –RDY to begin the burst mode transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| -BMACK   | S(L)                        | BURST MODE ACKNOWLEDGE: This signal is asserted by the system to indicate that it can support burst mode for the address currently on the bus. The system asserts –BMACK in response to the processor asserting –BMREQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CLK_ECB  | 1                           | <b>EXTERNAL CLOCK BYPASS:</b> This signal is used for chip testing and should be tied low during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| -CLKDBL  | ı                           | CLOCK DOUBLER: Tying this signal low causes the internal logic to run at twice the frequency of the clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SYMBOL       | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                      |  |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PARITY <3:0> | I/O<br>S(L) | PARITY*: When enabled this signal provides even or odd parity checking for the data bus. NOTE: PARITY3 is for Byte 0 / Half–Word 0. (See Table below *)                                                                                                                          |  |

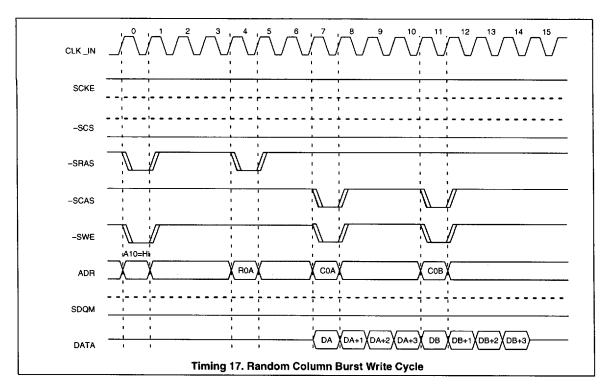

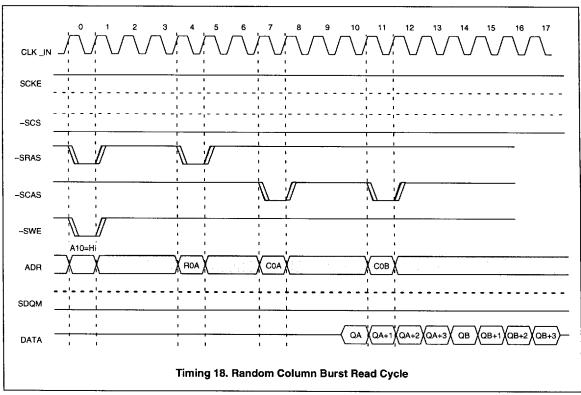

| -SWE         | OS(L)       | SDRAM Write Enable: This signal should be tied to the -WE input of SDRAM.                                                                                                                                                                                                        |  |

| -SRAS        | OS(L)       | SDRAM Row Address Strobe: This signal should be tied to the -RAS input of SDRAM.                                                                                                                                                                                                 |  |

| -SCAS        | OS(L)       | SDRAM Column Address Strobe: This signal should be tied to the -CAS input of SDRAM.                                                                                                                                                                                              |  |

| -SCS <3:0>   | OS(L)       | SDRAM Chip Select: Enables all command inputs, -RAS, -CAS, and -WE to SDRAM.                                                                                                                                                                                                     |  |

| SCKE         | OS(L)       | SDRAM Clock Enable: This is an active high clock enable signal for SDRAM.                                                                                                                                                                                                        |  |

| SDQM <1:0>   | OS(L)       | SDRAM INPUT MASK/OUTPUT ENABLE: SDQM<0> and SDQM<1> correspond to D<63:32>and <31:0> respectively.                                                                                                                                                                               |  |

| -NVWE        | OS(L)       | WRITE ENABLE FOR NON-VOLATILE MEMORY: This signal is asserted one cycle after –AS and stays asserted till one cycle before the end of the transaction for a write operation. The signal is generated only when internal wait state generation is enabled for the current access. |  |

| -OE          | O<br>S(L)   | OUTPUT ENABLE: This signal is asserted one cycle after –AS and stays asserte the last cycle of a read operation. This signal is generated when internal wait s generation is enabled for the current access.                                                                     |  |

| -READYOUT    | OS(L)       | Ready Out for external Bus Masters using Internal Ready Generation.                                                                                                                                                                                                              |  |

| -PDRESET     | S(L)        | Power Down Reset is asserted by the external system to get the part out of powerdow mode.                                                                                                                                                                                        |  |

| BIUCLOCK     | I           | This signal is reserved for future use and should be tied high.                                                                                                                                                                                                                  |  |

| EMU_SD <3:0> | I/O         | EMULATOR STATUS/DATA BITS: Bi-directional pins used by a hardware emulator to control and monitor MB86934 execution. These pins should be left unconnected.                                                                                                                      |  |

| EMU_D <3:0>  | 1/0         | <b>EMULATOR DATA BITS:</b> Bi-directional pins used by a hardware emulator to control and monitor MB86934 execution. These pins should be left unconnected.                                                                                                                      |  |

| -EMU_BRK     | I           | <b>EMULATOR BREAK REQUEST LINE:</b> Input used by a hardware emulator to request a trap when emulation is enabled. This pin should be unconnected.                                                                                                                               |  |

| -EMU_ENB     | I/O         | <b>EMULATOR ENABLE:</b> Tied low while the MB86934 is being reset to enable hardware emulator mode on the chip. This pin should be left unconnected.                                                                                                                             |  |

| TCK          | ī           | TEST CLOCK: JTAG compatible test clock input.                                                                                                                                                                                                                                    |  |

| TMS          | 1           | TEST MODE: JTAG compatible test mode select pin. Test is enabled when-TMS is low.                                                                                                                                                                                                |  |

| TDI          | 1           | TEST DATA IN: JTAG compatible test data input.                                                                                                                                                                                                                                   |  |

| TDO          | 0           | TEST DATA OUT: JTAG compatible test data output.                                                                                                                                                                                                                                 |  |

| -TRST        | 1           | TEST RESET: Asynchronous rest for JTAG logic. If not using JTAG, this signal must be pulled low.                                                                                                                                                                                 |  |

| *     | PARITY3    | PARITY2    | PARITY1    | PARITY0   |

|-------|------------|------------|------------|-----------|

| BIU   | D<31: 24>  | D<23:16>   | D<15: 8>   | D<7: 0>   |

| SDRAM | D <63: 48> | D <47: 32> | D <31: 16> | D <15: 0> |

1. In the following description, signal names preceded by a minus sign (-) indicate an active low state. Dual function pins have two names separated by a slash (/).

- I =Input Only Pin

O =Output Only Pin

I/O =Either Input or Output Pin

- A(L) = Synchronous: Inputs may be asynchronous: Inputs may be asynchronous: Inputs must meet setup and hold times relative to CLK\_IN

A(L) = Synchronous: Inputs must meet setup and hold times relative to CLK\_IN Outputs are Synchronous to CLK\_IN

- G(...)=While the bus is granted to another bus master (-BGRNT=asserted), the pin is G(1) is driven to V<sub>C</sub>C

- G(0) is driven to V<sub>SS</sub>

G(Z) floats

G(Q) is a valid output

- I (...) =While the bus is between bus cycles (or being reset) and is not granted to I (Q) is a valid output

#### **OVERVIEW**

The Fujitsu MB86934 is a high performance, 32-bit RISC processor which executes at 50 MIPS peak and 46 MIPs sustained performance with 50 MHz clock frequency. It has a floating point Unit that performs single precision multiply and single precision adds at the rate of 1 per cycle. Like its predecessors, the MB86934 is based on the SPARC architecture and is upward code compatible with previous implementations. The MB86934 has been developed specifically with the needs of embedded applications in mind and offers high performance and high integration for these applications.

The MB86934 instruction set is streamlined and hardwired for fast execution with most instructions executing in a single cycle. The Integer Unit (IU) features a 5-stage pipeline which has been designed to handle data interlocks, has an optimized branch handler for efficient control transfers, and a bus interface to handle single cycle bus accesses to on-chip memory.

An internal register file consisting of 136 registers organized into eight overlapping windows speeds interrupt response time and context switches. The register file minimizes accesses to memory during procedure linkages and facilitates passing of parameters and assignment of variables.

On-chip 8 Kbyte instruction and 2 Kbyte data caches have been added to decouple the processor from external memory. These caches have been designed with maximum flexibility in mind and allow entries to be locked to improve overall system performance.

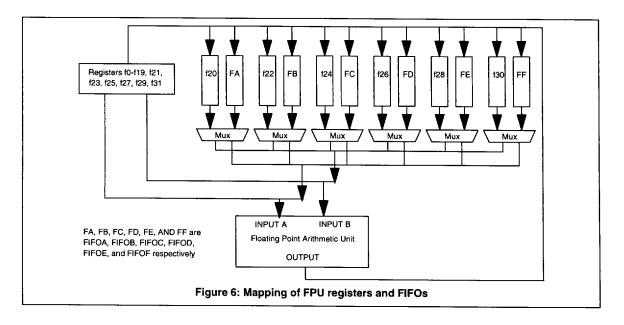

The FPU gets data from a 32 word register file for all standard FPU instructions. The enhanced FPU instructions may get their data from the FIFOs or some of the FPU registers as described later. The FIFOs decouple the FPU from external memory latency.

The SDRAM interface provides a mechanism to easily interface to SDRAMs. These DRAMs are capable of providing data at a peak rate of 400 Mbytes/sec. The DMA and FIFOs coupled with the SDRAM interface provide a cost effective way of providing data to the FPU at very high rates.

Separate 32-bit on-chip instruction and data paths provide a high bandwidth interface between the IU and on-chip cache. These buses support single cycle instruction execution as well as single cycle data transfers with the cache.

The internal data path between the data cache and the FPU is 64-bits wide. This allows the loading of a double precision operand from the cache to the FPU register file in one cycle.

The MB86934 also includes hardware for integer multiply and divide. The hardware support significantly

improves the performance of these operations with 32-bit integer multiplies executing in 5 clock cycles, 16-bit integer multiplies in 3 cycles, 8-bit integer multiplies in 2 cycles, and a multiply by zero can complete in a single cycle.

#### **KEY FEATURES**

Fast Integer Unit Instruction Execution: Simple functions make up the bulk of instructions in most programs so that execution speed can be greatly improved by designing these instructions to execute in as short a time as possible. The majority of instructions execute in one cycle with only a few of the more complex, such as integer multiply, taking additional cycles.

Fast Floating Point Unit: The high performance FPU implemented on the MB86934 executes all Single/Double precision operations. The FPU has a three stage pipeline. All single precision operations, except the Divide and Square Root are executed at the rate of one per cycle. Double Precision Add and Subtract are also executed at the rate of one per cycle.

On-chip FIFOs to assist in vector operation: The FPU instructions get their operands from a 32-bit register file. Enhanced FPU instructions get their operands from either the FPU register file or from the 6 FIFOs on-chip. Data can be loaded into the FIFOs or from the FIFOs into memory by the DMA controller. For operations on large arrays of data, the FIFOs and the DMA controller relieve the application program of the task of address generation and moving data to and from memory. This provides a significant improvement in performance for vector operations.

Large Register Set: The large register set for the IU reduces the number of required accesses to data memory. The registers are organized in overlapping groups called register windows which allows registers to be reserved for high priority tasks, such as interrupts, or for recurring requirements such as operating system working registers. The overlapping windows also simplify parameter passing during procedure linkage and reduce code in most programs.

**On-Chip Caches:** To decouple the speed of the processor from the memory sub-system, data and instructions caches have been added. The caches are organized as two-way set-associative for improved hit rates. In addition, the set-associative caches organization allows entries to be locked, while the rest of the cache performs normally.

Cache Locking: Both data and instruction entries can be locked into their respective caches to ensure deterministic response and highest performance for critical or frequently recurring routines. Maximum flexibility has been designed into the cache to allow all or selected portions to be locked.

**Bus Interface:** The requirement for glue logic between the MB86934 and the system is minimized by providing

programmable chip selects, programmable wait state circuitry, and support for connection to fast page-mode DRAM. Multiple bus masters are supported through a simple handshake protocol. The MB86934 can boot from either 8, 16 or 32-bit wide memory. For high frequency operation, the bus is capable of running at half the speed of the core.

SDRAM Interface: The Bus interface also provides

support to directly connect to high performance SDRAM. The SDRAM interface will support up to four banks of memory. A bank can be 32 or 64 bits wide. The SDRAM controller is designed to interface to 4M (x8), 16M (x4 and x8) and 64M (x8) SDRAMs. The smallest memory size that can be supported is 2Mbytes and the largest memory size can be 512Mbytes.

Table 1. MB86934 Instruction Set

| LOGICAL                                                                                        | ARITHMETIC/SHIFT                                                                                                                                                                 | DATA MOVEMENT                                                                                                                                                | FPU INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONDITION CODES UNCHANGED AND OR XOR AND NOT OR NOT XNOR                                       | CONDITION CODES UNCHANGED ADD SUBTRACT MULTIPLY(SIGNEO/UNSIGNED) SCAN SCAN SETH SHIFT LOGICAL SHIFT RIGHT LOGICAL SHIFT RIGHT ARITHMETIC                                         | TO USER/SUPERVISOR SPACE SIGNED LOAD BYTE LOAD BYTE LOAD WORD LOAD WORD LOAD DOUBLE WORD STORE BYTE STORE HALF-WORD STORE HORD STORE WORD STORE DOUBLE WORD  | CONVERSION CONVERT INTEGER TO SINGLE CONVERT INTEGER TO DOUBLE CONVERT SINGLE TO INTEGER CONVERT SINGLE TO INTEGER CONVERT SINGLE TO SINGLE CONVERT SINGLE TO SINGLE MOVE MOVE NEGATE                                                                                                                                                                                                                                                              |

| CONDITION CODES SET AND OR XOR AND NOT OR NOT XNOR                                             | CONDITION CODES SET ADD SUBTRACT MULTIPLY(SIGNED/UNSIGNED) MULTIPLY STEP DIVIDE STEP  EXTENDED AND CONDITION CODES UNCHANGED ADD SUBTRACT                                        | TO USER SPACE UNSIGNED LOAD BYTE LOAD HALF-WORD  TO ALTERNATE SPACE SIGNED LOAD BYTE LOAD HALF-WORD LOAD WORD LOAD DOUBLE WORD STORE BYTE STORE HALF-WORD    | ABSOLUTE VALUE  SQUARE ROOT SQUARE ROOT SINGLE SQUARE ROOT DOUBLE  ADD/SUBTRACT ADD SINGLE ADD DOUBLE SUBTRACT SINGLE SUBTRACT DOUBLE                                                                                                                                                                                                                                                                                                              |

| CONTROL TRANSFER                                                                               | EXTENDED AND CONDITION                                                                                                                                                           | STORE MALF-WORD STORE DOUBLEWORD                                                                                                                             | MULTIPLY/DIVIDE MULTIPLY SINGLE MULTIPLY DOUBLE                                                                                                                                                                                                                                                                                                                                                                                                    |

| CONDITIONAL BRANCH<br>CONDITIONAL TRAP<br>CALL<br>RETURN<br>SAVE<br>RESTORE<br>JUMP AND LINK   | CODES SET ADD SUBTRACT  TAGGED AND CONDITION CODES SET (WITH AND WITHOUT TRAP ON OVERFLOW) ADD SUBTRACT                                                                          | TO ALTERNATE SPACE UNSIGNED LOAD BYTE LOAD HALF-WORD  ATOMIC OPERATION IN USER SPACE SWAP WORD LOAD/STORE UNSIGNED BYTE  ATOMIC OPERATION IN ALTERNATE SPACE | MULTIFLY SINGLE TO DOUBLE DIVIDE SINGLE DIVIDE DOUBLE  FLOATING-POINT COMPARE INSTRUCTIONS COMPARE SINGLE COMPARE DOUBLE COMPARE SINGLE AND EXCEPTION IF UNORDERED COMPARE DOUBLE AND EXCEPTION IF UNORDERED UNORDERED UNORDERED UNORDERED                                                                                                                                                                                                         |

|                                                                                                | ONTROL REGISTER                                                                                                                                                                  | SWAP WORD                                                                                                                                                    | BRANCH ON FLOATING-POINT<br>CONDITION CODES                                                                                                                                                                                                                                                                                                                                                                                                        |

| WRITE PSR WE<br>READ TBR F                                                                     | AD WIM RDASR<br>RITE WIM WRASR<br>READ Y                                                                                                                                         | ENHANCED FPU INSTRUCTIONS                                                                                                                                    | BRANCH ALWAYS                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LOAD/STORE  LOAD FLOATING-I LOAD FLOATING-I STORE FLOATING-I STORE FLOATING-I STORE FLOATING-I | G-POINT REGISTER ATING-POINT REGISTER ATING-POINT REGISTER OINT STATE REGISTER OATING-POINT E-FLOATING-POINT POINT STATE REGISTER POINT STATE REGISTER POINT DEFERRED TRAP QUEUE | ALL THE FPU INSTRUCTIONS HAVE<br>CORRESPONDING ENHANCED FPU<br>INSTRUCTIONS                                                                                  | BRANCH NEVER BRANCH ON UNORDERED BRANCH ON UNORDERED BRANCH ON UNORDERED OR GREATER BRANCH ON UNORDERED OR GREATER BRANCH ON UNORDERED OR LESS BRANCH ON LOSS OR GREATER BRANCH ON LESS OR GREATER BRANCH ON LOSS OR GREATER BRANCH ON HOT EQUAL BRANCH ON UNORDERED OR EQUAL BRANCH ON UNORDERED OR GREATER OR EQUAL BRANCH ON UNORDERED OR GREATER OR EQUAL BRANCH ON UNORDERED OR LESS OR EQUAL BRANCH ON LESS OR EQUAL BRANCH ON LESS OR EQUAL |

11

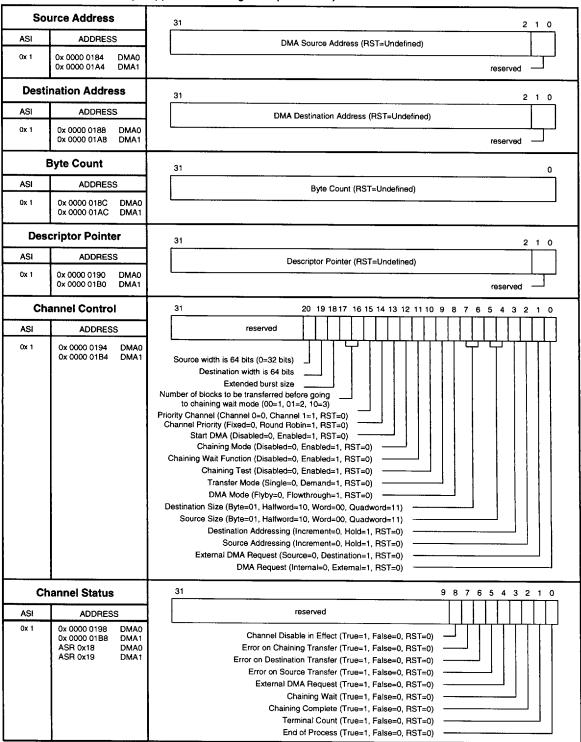

On-Chip DMA: Two DMA channels support contiguous block and chained block transfers. Byte, half-word, word, and quad-word data types are supported. Either fly-by or flow through addressing modes can be selected.

The DMA controller is also capable of transferring data to and from the FIFOs in the fly-by mode.

Enhanced Instruction Set: The MB86934 incorporates Enhanced Floating-Point instructions which provide a significant improvement in performance for vector operations. It also includes a fast integer multiply instruction which executes in a fast 5, 3 or 2 cycles for 32-bit, 16-bit or 8-bit multiplicands. An integer divide-step instruction cuts divide times by a factor of 10 over previous SPARC implementations. A scan instruction supports a single cycle search for the most significant 1 or 0 in a word.

#### **Power Down Modes**

The MB86934 supports multiple power down modes. It provides a mechanism to turn off the clock to various

functional units. These can be turned off by the application program if it is not using the particular functional unit.

Test and Debug Interface: The MB86934 supports production test through industry standard JTAG boundary scan. Hardware emulation is supported with on-chip breakpoint and single step logic. A dedicated emulator bus provides a means to trace transactions between the integer unit and on-chip cache.

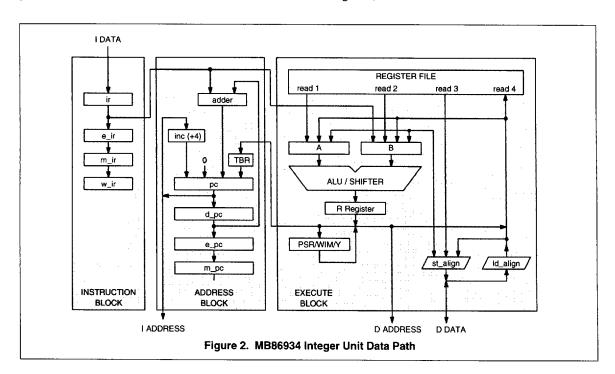

#### CPU

The MB86934 core is a high performance fully custom implementation of the SPARC architecture. The core is compact to leave room for peripheral integration and yet is designed in a way to allow the major blocks to be customized for varying application requirements. The core is made up of three functional units: the Instruction block, the Address block and the Execute block. (see Figure 2)

A five stage instruction pipeline is responsible for decoding all instructions and generating the control signals to the other blocks. The 5-stage pipeline consists of Fetch (F), Decode(D), Execute(E), Memory(M) and Writeback(W). Instruction memory is addressed and returns instructions in the (F) stage, the register file is addressed and returns operands in the (D) stage, the ALU computes results in the (E) stage, external memory is addressed in the (M) stage, and the register file is written back in the (W) stage.

#### **FPU**

The high performance FPU implemented on the MB86934 is compatible with the ANSI/IEEE-754-1985 standard. It is fully compatible with SPARC ver. 8 FPU.

The FPU is implemented as a 3 stage pipeline. The FPU executed all Single/Double precision floating point operations. Quad precision floating point operations are not executed by the FPU. All floating point load and stores and Branch on Floating point condition code instructions are executed by the integer unit.

The FPU also executes Enhanced Floating Point Operations. These operations can get their operands from the registers in the FPU register file or the FIFOs (as described in the section on FIFOs). All single and double precision Enhanced Floating Point operations are executed by the FPU. Enhanced Floating-point Load and store operations are not defined.

The performance of the FPU is summarized below:

| Floating Point<br>Operation     | Throughout (in cycles) | Latency<br>(in cycles) |

|---------------------------------|------------------------|------------------------|

| All comparisons and conversions | 1                      | 3                      |

| Single Precision<br>ADD/SUB/MUL | 1                      | 3                      |

| Single Precision<br>DIV/SQRT    | 13                     | 14                     |

| Double Precision<br>ADD/SUB     | 1                      | 3                      |

| Double Precision<br>MUL         | 4                      | 6                      |

| Double Precision<br>DIV/SQRT    | 28                     | 29                     |

Even though the Floating point queue is 3 deep, whenever a divide or square root enters the queue it is marked as full to prevent any other floating point instructions from entering the queue. This is done to prevent the interrupt latency from being long.

#### ADDRESS SPACE

The MB86934 offers a large addressing range and allows separate user and supervisor spaces to be defined. In addition to 32 address lines, 4 alternate address space identifiers (ASIs) distinguish between protected and unprotected space. Of the 256 possible ASI values, two define accesses to user data and user instruction space while the remaining ASI values define supervisor space.

Anytime a reset, synchronous trap or asynchronous trap occurs, the processor is placed into the supervisor mode. In this mode, the processor executes instructions and moves data out of supervisor space. While in supervisor mode, the processor also has access to the remaining ASI values. Except for those mentioned and those reserved for control register space, the remaining ASI values can be used to access other alternate data spaces defined by the application.

The distinction of user versus supervisor space allows the hardware to protect against accidental or un-authorized access to system resources. For real time operating system (RTOS) development for example, the separate spaces provide a mechanism for effectively partitioning RTOS space from user space.

#### **REGISTERS**

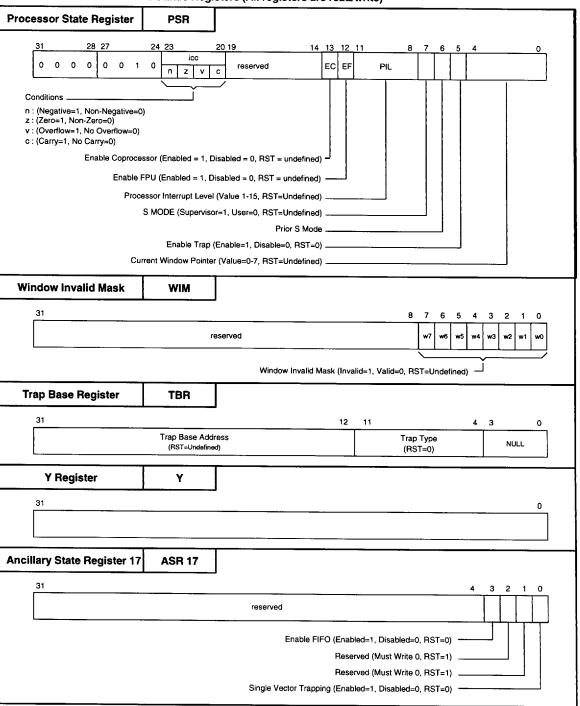

The MB86934 integer unit register set is divided into those used for general purpose functions and those used for control and status.

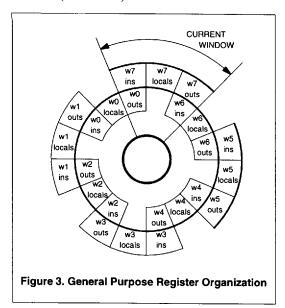

The 136 general purpose registers are divided into 8 global registers and 8 overlapping blocks or "windows". Each window contains 24 registers. Of these, 8 are local to the window, 8 "out" registers overlap with the next window and 8 "in" registers overlap with the previous window (see Figure 2).

This organization makes it easy to pass parameters to subroutines. Parameters that are to be passed along are written to the "out" registers and the subsequent procedure call decrements the window pointer to make a new set of registers available. The passed parameters are now available to the subroutine in the current window's "in" registers.

Register windows improve performance in embedded applications because they function as local variable caches which retain either interrupt, subroutine, context or operating system variables with no additional overhead. In addition, code can be reduced by exploiting the efficient execution of procedure linkage by preventing in-lining compiler optimizations.

The registers that make up the register file each have three read-only and one write-only port. The use of a four port register file allows even store instructions, which may require that three operands be read out of the register file, to proceed at one instruction per cycle.

The control and status registers include those defined by the SPARC architecture ( See Table 2 ) and those

mapped into alternate address space to control peripheral functions (See Table 3).

#### **INSTRUCTION SET**

The MB86934 is upward code compatible with other SPARC processors. Additional instructions, previously not directly supported, have been added to improve performance in embedded applications. Enhanced Floating-point instructions, integer multiply, integer divide step, and scan for first changed bit have been added to the already powerful SPARC instruction set. See Table 1 for a list of supported instructions.

#### **INTERRUPTS**

A key measure of a processor's suitability for use in embedded application is in its ability to handle interrupts with a minimum of delay and in a deterministic fashion. The MB86934 implementation has been tailored to insure not only low average latency but low maximum latency as well.

Interrupt response time is made up of the sum of the times it takes the processor to finish its current task after recognizing an interrupt, and the time it takes to begin executing interrupt service routine instructions. The MB86934 implements numerous features to minimize both factors.

To minimize the time it takes to finish the current task, the MB86934 is designed so that tasks can either be interrupted or completed in a minimum of cycles. Implementation details that accomplish this aim include cache line misses that can be filled one word at a time through a pre-fetch buffer, integer divide that is interruptible through the use of a divide step instruction,

fast multiply and a 1 word write buffer to limit pending bus transactions.

To minimize the time required to start executing the interrupt service routine the processor switches to a new register window when an interrupt is detected. This feature allows the service routine to be executed without first requiring that the current registers be saved. The user can also elect to lock the service routine into the cache. This makes the routine available for immediate access. The on-chip data cache can also serve the service routine as a fast local stack for minimum delay in accessing routine variables.

The MB86934 provides for up to 15 different interrupt levels. The highest interrupt level is non-maskable.

#### CACHE

The MB86934 has separate on-chip data and instruction caches. This allows the user to build a high performance system without incurring the cost of requiring fast external memory and the associated control logic. The caches are physically mapped.

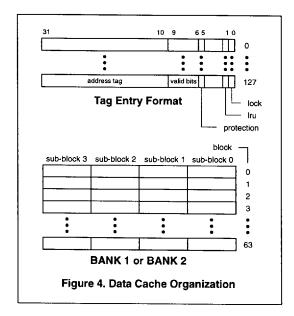

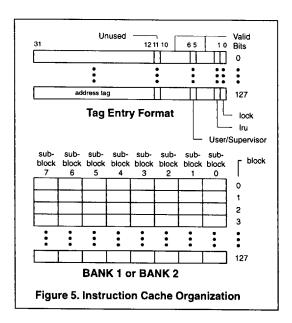

The instruction cache is organized as two banks of one hundred twenty-eight 32-byte lines (See Figure 5). The data cache is organized as two banks of sixty-four 16-byte lines (See Figure 4).

The lines are organized as two-way set-associative for good performance even when cache locking is in effect. Lines are divided into sub-blocks each four bytes wide. On a cache miss, the caches are updated either 1 word (4 bytes) at a time, or 4 words at a time using the processor's burst mode feature. Single word updates minimize interrupt latency associated with long cache line replacements, while 4 word burst refills maximize the use of available bus bandwidth. An instruction pre-fetch buffer fetches the next sequential instruction anticipating that it will be needed to fill the next instruction cache miss.

The caches can be used in either normal or one of two lock modes. In normal mode, the caches use an LRU (least recently used) algorithm to replace one of the two appropriate entries. Alternately, the two locking modes allow the entire cache or just selected entries to be locked. The lock modes allow time critical routines to be locked in cache.

Global locking allows the entire content of either the instruction or data cache to be frozen. Two control bits in the cache control register enable or disable locking for either cache. With the entire cache locked, no valid entry can be replaced. To insure best possible performance however, invalid entries will be updated if they are accessed. This is done automatically and incurs no time penalty.

Local cache locking makes it possible to dynamically lock selected instructions or data entries into the appropriate cache. This feature gives the flexibility, for

example, to assure deterministic response for certain critical interrupt routines by locking the routine's code into the cache. Entries can also be locked where it is desirable to give performance priority to certain often used routines which might otherwise be removed from cache. The 2-way set-associativity allows the cache to perform effectively even with some locked entries.

In local lock mode, each entry can either be locked individually by software or automatically with hardware assist. For individual locking, software writes the lock bit in the appropriate cache tag line. For automatic locking, a bit in each cache control register enables or disables the feature. The enable bit is set at the beginning of a routine for which the entries are to be locked. This causes the location of any cache access occurring while the bit is enabled to be locked into the cache. In addition to requiring just one initial cycle to enable, automatic entry locking incurs no overhead while in effect. Locked locations can be cleared with a single write to a control register.

In unlocked operation, the data cache uses a writethrough update policy and allocates a cache entry only on a load. Writes are buffered so that the processor can continue executing while data is written back to memory. In contrast, writes to locked data cache locations are not written through to main memory. Besides reducing external bus activity, this design supports configuring a portion of data cache as on-chip RAM which does not map to external memory.

The data and instruction caches are designed to be accessed independently over separate data and instruction buses to allow data to be loaded from and stored to cache at peak rates of 1 CPI.

#### **FIFOs**

The MB86934 provides 6 buffers which are configured as FIFOs. Each of the FIFOs are 64-words deep. The registers for the Enhanced Floating Point instruction set are partially mapped to the FIFOs as follows:

| f0-f19, f21, f23, f25,<br>f27, f29, and f31 | 32-bit register     |  |

|---------------------------------------------|---------------------|--|

| f20                                         | 64-word FIFO A (FA) |  |

| f22                                         | 64-word FIFO B (FB) |  |

| f24                                         | 64-word FIFO C (FC) |  |

| f26                                         | 64-word FIFO D (FD) |  |

| f28                                         | 64-word FIFO E (FE) |  |

| f30                                         | 64-word FIFO F (FF) |  |

Each FIFO has a pointer and a depth register associated with it. Any access to the FIFO accesses the location pointed to by the pointer and increments the pointer. When the pointer reaches the value in the depth register, on the next access the pointer rolls over to 0. The FIFOs are also mapped to registers in ASI 0x1 address space. These registers are used by the DMA controller to recognize transfers to and from the FIFOs. These cannot be accessed by LDA/STA instructions.

Any enhanced floating point operation accessing registers f20, f22, f24, f26, f28 and f30 access the head of the corresponding FIFO rather than the corresponding registers. Other Floating Point instructions access the corresponding registers in the floating point register file.

#### **BUS INTERFACE**

The SDRAM bus interface is integrated on-chip. This allows the MB86934 to interface to very high performance SDRAMS.