# SIEMENS

Preliminary

# SAB 8256A, SAB 8256A-2 Programmable Multifunction UART (MUART)

- SAB 8256A is compatible with processors up to 3 MHz system clock (e. g. SAB 8085A, SAB 8048, SAB 8051).

- SAB 8256A-2 is compatible with processors up to 8 MHz system clock (e.g. SAB 8085A-2, SAB 8086 minimum mode, SAB 80186).

- Full-duplex asynchronous serial interface with programmable 5–8 data bits, 0.75–2 stop bits, parity generation and checking.

- Internal baud rate generator programmable for 50-19, 200 Baud; 0-1 Megabaud possible with external baud rate clock.

- Interrupt controller with 8 priority levels; each level independently maskable, programmable for normal and fully nested operation with SAB 8085 and SAB 8086 processor families.

- Five programmable 8-bit counter/timers, internal or external clock, four are cascadable to two 16-bit counter/timers.

- Two 8-bit I/O ports, bit programmable for input/output, handshake mode supported.

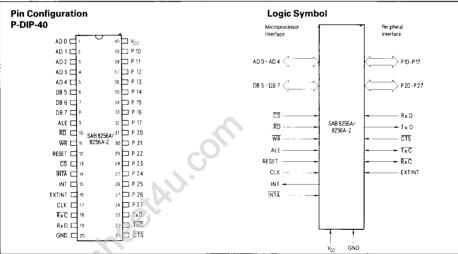

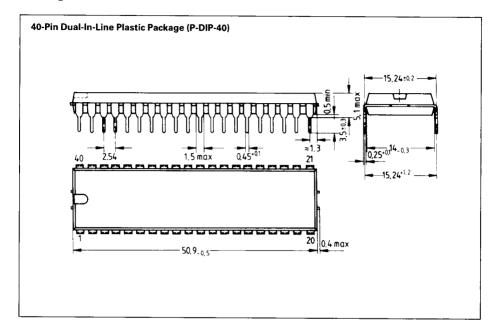

- 40-pin dual-in-line plastic package (P-DIP-40)

SAB 8256A integrates four of the most often used peripheral functions in a microcomputer system into a 40-pin dual-in-line plastic package (P-DIP-40): serial interface, parallel interface, timer/counter and interrupt controller. It is primarily suited for systems like SAB 8048, SAB 8051, SAB 8085, SAB 8086,

SAB 8088, SAB 80186 and SAB 80188 which have a multiplexed bus. With some additional circuitry, the SAB 8256A can also be used with other processors. All the functions of SAB 8256A are programmable by software, leading to a great flexibility in system design.

DataSheet4U.col

# **Pin Description and Functions**

| Symbol              | Pin                                                                                                                      | Input (I)<br>Output (O) | Functions                                                                                                                                                                                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD4,<br>DB5-DB7 | 1-5<br>6-8                                                                                                               | I/O                     | Interface to Multiplexed Address/Data Bus Bidirectional lines to 8 data bits and 5 least significant address bits which are latched internally on the falling edge of ALE.                                                                                                                        |

| ALE                 | 9                                                                                                                        | 1                       | Adress Latch Enable The five least significant address bits and CS are latched on the falling edge of ALE into an internal register.                                                                                                                                                              |

| RD                  | 10                                                                                                                       | 1                       | Read Control The microprocessor reads data from the chip when this signal is low.                                                                                                                                                                                                                 |

| WR                  | 11                                                                                                                       | 1                       | Write Control The microprocessor writes data into the chip with a low on this pin.                                                                                                                                                                                                                |

| RESET               | 12                                                                                                                       | l                       | Reset A high on this pin forces the chip to its initial state. The chip remains in this state until control information is written into the chip.                                                                                                                                                 |

| CS                  | 13                                                                                                                       | I                       | Chip Select A low on this pin during ALE enables the bus interface of the chip. Neither read nor write operations are possible without this enable. The signal has no effect on the internal operation of the chip.                                                                               |

| INTA                | 14                                                                                                                       | 1                       | Interrupt Acknowledge When this signal is low, the microprocessor informs the chip that an interrupt request is being serviced.                                                                                                                                                                   |

| INT                 | 15                                                                                                                       | 0                       | Interrupt Request The chip demands interrupt service from the microprocessor with a high on this output.                                                                                                                                                                                          |

| EXTINT              | 16                                                                                                                       |                         | External Interrupt An external source can request interrupt service through this input. The source can be either a peripheral or another SAB 8256A with its INT pin as the signal source. The input is level sensitive (high). The request must be held high until the processor acknowledges it. |

| CLK                 | System Clock Clock on this input is the reference clock for the timers, baud rate generator and various other functions. |                         |                                                                                                                                                                                                                                                                                                   |

| Symbol | Pin                                                                                                                                         | Input (I)<br>Output (O) | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

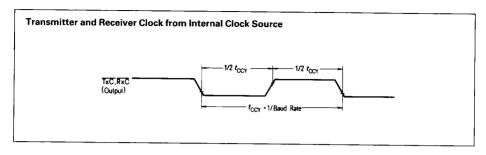

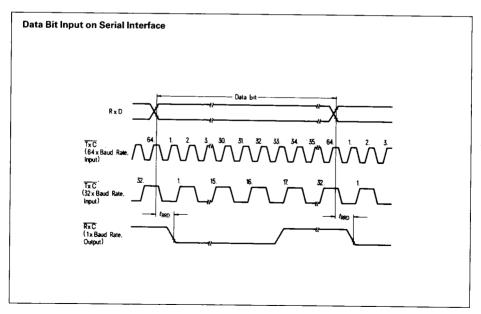

| R×C    | 18                                                                                                                                          | I/O                     | Receive Clock  If this pin is programmed as an output, it provides a low-to-high transition at the sampling point of each received data bit (excluding the framing bits). When programmed as an input, an externally generated receive clock must be connected to this pin. At DC, its frequency can range up to 1.024 MHz matching the receiver baud rate.  The internal baud rate generator is disabled if this pin is used as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R×D    | 19                                                                                                                                          | I                       | Receive Data Input for serial data, which is converted to parallel format while discarding the framing bits and then is made available for the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

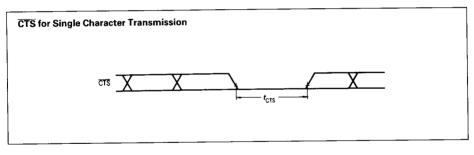

| CTS    | 21 I Clea This are sany be transtran transtran first If it of the tregists is in occurrence of the transtranstranstranstranstranstranstrans |                         | Clear to Send This input enables the serial transmitter. If 1, 1.5 or 2 stop bits are selected, CTS is level sensitive. As long as CTS is low, any character loaded into the transmitter buffer register will be transmitted serially. For continuous transmission, this input must be tied to low. A single negative going pulse causes the transmission of a single character previously loaded into the transmitter buffer register. If the transmitter buffer is empty, this pulse will be ignored. If this pulse occurs during the transmission of a character up to the time where 0.5 of the first (or the only) stop bit is sent out, it will be ignored. If it occurs afterwards, but before the end of the stop bits the next character will be transmitted immediately following the current one. If CTS is still high when the transmitter register is sending the last stop bit, the transmitter will enter its idle state until the next high-to-low transition on CTS occurs.  If 0.75 stop bits is chosen, CTS input is edge sensitive. A negative edge on CTS results in the immediate transmission of the next character. The length of the stop bits is determined by the time interval between the beginning of the first stop bit and the next negative edge on CTS. A high-to-low transition has no effect if the transmitter buffer is empty or if the time interval between the beginning of the stop bit and next negative edge is less than 0.75 bit. A high or a low level or a low-to-high transition has no effect on the transmitter for the 0.75 stop bit mode. |

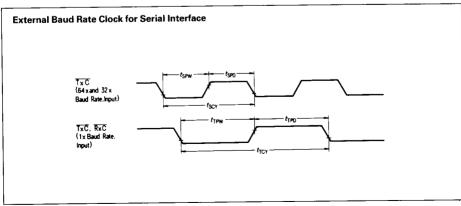

| T×C    | 22                                                                                                                                          | I/O                     | Transmit Clock The function of this pin can be programmed in 3 configurations As an output it delivers the transmit clock corresponding to the baud rate. If programmed as an input, an external clock of 32 or 64 times the baud rate that is common to transmitter and receiver, or a $1 \times$ clock matching the baud rate which is used for the transmitter only, can be tied to this pin. The maximum frequency is $1.024$ MHz. Thus, baud rates ranging from 0 to $16$ Kbaud $(64 \times)$ or from 0 to $32$ Kbaud $(32 \times)$ or from 0 to $1.024$ Mbaud $(1 \times)$ are possible. The internal baud rate generator is disabled if $\overline{1 \times C}$ is selected as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **SAB 8256A**

| Symbol                                                                                                                                                | Pin   | Input (I)<br>Output (O)                                                                                                                                                                                                                                                                                                     | Functions                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T×D                                                                                                                                                   | 23    | 0                                                                                                                                                                                                                                                                                                                           | Transmit Data Serial data output. The parallel data received from the processor and the framing bits added by the SAB 8256A are sent out serially over this output when the transmitter is enabled by the CTS signal.                                                                                                                                    |

| P27-P20                                                                                                                                               | 24-31 | 1/0                                                                                                                                                                                                                                                                                                                         | Parallel I/O Port 2 The eight general purpose I/O pins of parallel port 2 can be configured in sets of four pins (nibbles) as inputs or outputs or 8 bit I/O with handshake (control signals at port 1). In the nibble mode the output signals are latched whereas the input signals are not. In the handshake mode both inputs and outputs are latched. |

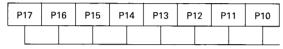

| P17-P10  32-39  I/O  Parallel I/O Port 1  Each one of these 8 pins ca Alternatively these pins ca extends considerably the The pins are assigned to s |       | Parallel I/O Port 1 Each one of these 8 pins can be programmed as input or output. Alternatively these pins can serve as control pins which extends considerably the functional spectrum of the chip. The pins are assigned to special functions implicitly by programming. All outputs are latched whereas inputs are not. |                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>cc</sub>                                                                                                                                       | 40    | _                                                                                                                                                                                                                                                                                                                           | Power Supply (+5 V)                                                                                                                                                                                                                                                                                                                                      |

| GND                                                                                                                                                   | 20    | _                                                                                                                                                                                                                                                                                                                           | Ground (0 V)                                                                                                                                                                                                                                                                                                                                             |

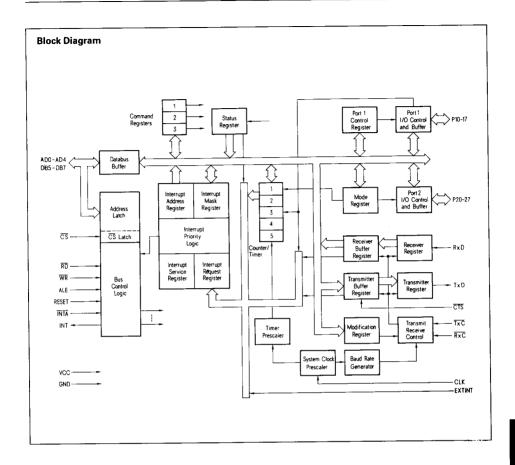

## **Functional Description**

#### **Bus Interface**

The bus interface unit, consisting of bus drivers, address latches and bus control logic, interfaces the SAB 8256A to the data, address and control buses of a microcomputer system. The chip is selected by the  $\overline{CS}$  signal, which is latched into the chip along with address lines AD0—AD4 by the ALE signal.  $\overline{WR}$  and  $\overline{RD}$  signals are used to write data into and read data from SAB 8256A.

Signals INT und INTA are used to handle interrupt protocol with the processor.

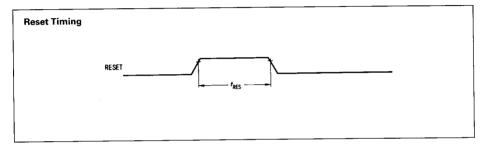

RESET signal resets the chip to its initial state.

#### Counter/Timers

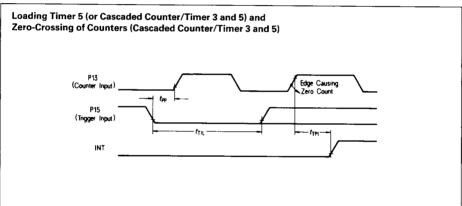

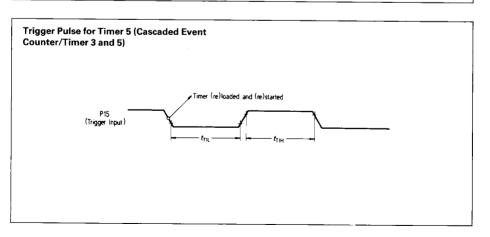

Five programmable counter/timers can be used in several modes. Each can be used as an 8-bit timer while two can alternatively serve as counters. Counter/timer 2 and timer 4 as well as counter/timers and timer 5 can be cascaded to 16-bit counter/timers. All counter/timers function as binary down-counters with a programmable initial value and generate an interrupt request on their 1 to 0 transition. An internal register is provided for the initial count of timer 5 and with an external trigger pulse it is possible to reload the initial value into timer 5 (also for cascaded counter/timer 3 and timer 5).

A common clock source with a frequency of either 1 KHz or 16 KHz is available for the timers. In addition, for counters, 2, 3 and the cascaded counters, an external clock source can be provided through two pins of part 1.

#### **Asynchronous Serial Interface**

For double buffered full-duplex operations both transmitter and receiver have two registers. The received data (5 to 8 data bits, programmable) is assembled to parallel format in the receiver register, the framing bits (Start, Stop, and Parity) are stripped off and stored into the receiver buffer register. The data to be transmitted is first loaded into the transmitter buffer register and then sent out through the transmitter register.

Controlling the CTS signal, single characters on character strings can be transmitted. Baud rate clock (50 to 19,200 Baud) is generated on the chip which is common to both the receiver and the transmitter. It is also possible to provide an external baud rate clock (common or separate for receiver and transmitter) to provide baud rates from 0 to 1.024 Mbaud.

#### Parallel Interface

The parallel interface consists of two 8-bit ports programmable as inputs or outputs. Each pin of port 1 can be programmed separately as an input or an output. They can also be used as control pins. Port 2 can be programmed as input or output in two 4-bit groups. Port 2 can also be used as an 8-bit input or output port with handshake signals.

#### **Assignment of Control Signals to Port 1**

| Pins<br>Port 1      | P17                            | P16                         | P15                                                                       | P14                                                                      | P13                                | P12                                | P11                   | P10 |

|---------------------|--------------------------------|-----------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------|------------------------------------|-----------------------|-----|

| Control<br>Function | External<br>interrupt<br>input | Break-In<br>detect<br>input | Trigger<br>input for<br>timer 5<br>(cascaded<br>counter/<br>timer<br>3+5) | Output<br>of the<br>clock of<br>the<br>internal<br>baudrate<br>generator | Clock<br>input for<br>counter<br>3 | Clock<br>input for<br>counter<br>2 | Handsha<br>Signals fo |     |

#### Interrupt Controller

The interrupt controller manages 12 interrupt sources (10 internal and 2 external) on 8 priority levels. Normal (every interrupt request immediately recognized) and "fully nested" (recognition based on priority) mode are supported.

The interrupt controller supports various methods of connecting SAB 8256A to the processor. Firstly, the true interrupt mode (using INT and INTA signals for interrupt protocol), secondly, a combination of polling and interrupt (using INT and interrupt address registers). The interrupt protocols of SAB 8048, SAB 8085A, SAB 8086, SAB 8088, SAB 80186 and SAB 80188 are directly supported.

# **Programming the SAB 8256A**

The functional characteristics of SAB 8256A can be programmed by writing appropriate control information into it. It is specially designed for ease of programming. Thus, it is possible to alter individual bits in certain registers like e.g. the Interrupt Mask Register and Command Register 3. All functions of SAB 8256A can be easily used because each unit (e.g. counter/timer, serial interface) has specially assigned registers which can be directly read or written.

# Re

| legi            | ster Se                                  | lect |                    |     |                    |      |                    |      |               |     |                         |     |                             |

|-----------------|------------------------------------------|------|--------------------|-----|--------------------|------|--------------------|------|---------------|-----|-------------------------|-----|-----------------------------|

|                 |                                          | FRQ  |                    | B0  |                    | 0    |                    | P2C0 |               | P10 |                         | Lo  |                             |

|                 |                                          | 8086 |                    | B1  |                    | ТВВК |                    | P2C1 |               | P11 |                         | 7   |                             |

|                 |                                          | ВІТІ | 1.1                | B2  | ır 2               | SBRK | 8                  | P2C2 |               | P12 | ster                    | 1.2 | ister                       |

| gisters         |                                          | BRKI | Registe            | B3  | Registe            | 0    | Registe            | СТ2  | legister      | P13 | rol Regi                | ឌ   | ask Reg                     |

| Read Registers  |                                          | SO   | Command Register 1 | С0  | Command Register 2 | NE   | Command Register 3 | стз  | Mode Register | P14 | Port 1 Control Register | L4  | Interrupt Mask Register     |

|                 |                                          | S1   | Co                 | C1  | လ                  | IAE  | ပိ                 | T5C  |               | P15 | Por                     | L5  | Inte                        |

|                 |                                          | CL0  |                    | EP  |                    | R×E  |                    | T24  |               | P16 |                         | 97  |                             |

|                 |                                          | CL1  |                    | PEN |                    | 0    |                    | T35  |               | P17 |                         | 77  |                             |

|                 | AD0<br>AD1                               | 0    |                    | _   |                    | 0    |                    | _    | •             | 0   |                         |     |                             |

| ess             | AD1<br>AD2                               | 0    |                    | 0   |                    | 1    |                    | -    |               | 0   |                         | 0   |                             |

| Address         | AD2<br>AD3                               | 0    |                    | 0   |                    | 0    |                    | 0    |               | -   |                         | -   |                             |

|                 |                                          | 0    |                    | 0   |                    | 0    |                    | 0    |               | 0   |                         | 0   |                             |

|                 | SAB 8085 Mode: AD3<br>SAB 8086 Mode: AD4 | FRQ  |                    | BO  |                    | SRES |                    | P2C0 |               | P10 |                         | LO  |                             |

|                 | 4B 8085<br>4B 8086                       | 9808 |                    | B1  |                    | TBRK |                    | P2C1 |               | P11 |                         | L1  |                             |

|                 | ώώ                                       | HIB  | _                  | B2  | 5                  | SBRK | ا<br>ا س           | P2C2 |               | P12 | Þ                       | L2  | Word                        |

| gisters         |                                          | BRKI | d Word             | B3  | d Word             | END  | d Word             | CT2  | Word          | P13 | trol Wo                 | F]  | l Enable                    |

| Write Registers |                                          | SO   | Command Word 1     | 8   | Command Word 2     | NE   | Command Word 3     | стз  | Mode Word     | P14 | Port 1 Control Word     | L4  | Interrupt-Level Enable Word |

|                 |                                          | S1   | Ö                  | 5   | Ŏ                  | IAE  | Ö                  | TEC  |               | P15 | Po                      | L5  | Interru                     |

|                 |                                          | CLO  |                    | EP  |                    | R×E  |                    | T24  |               | P16 |                         | 97  |                             |

|                 |                                          | CL1  |                    | PEN |                    | SET  |                    | T35  |               | P17 |                         | 17  |                             |

|                 |                                          | 8   |                              | D0 |                    | 00 |              | 8  |              | 8  | ;             | 8  |                       |

|-----------------|------------------------------------------|-----|------------------------------|----|--------------------|----|--------------|----|--------------|----|---------------|----|-----------------------|

|                 |                                          | 10  |                              | 10 | ,                  | 10 |              | D1 |              | 10 |               | 10 |                       |

|                 |                                          | D2  | ister                        | D2 |                    | D2 |              | D2 |              | D2 |               | D2 | r 2                   |

| gisters         |                                          | D3  | ess Reg                      | D3 | Buffer             | D3 | ort 1        | D3 | ort 2        | D3 | mer 1         | 23 | 'Counte               |

| Read Registers  |                                          | D4  | Interrupt Address Register   | 72 | Receiver Buffer    | D4 | Read Port 1  | D4 | Read Port 2  | 40 | Read Timer 1  | D4 | Read Timer/Counter 2  |

| ш               |                                          | DS  | Interru                      | 52 | a.                 | D5 |              | D2 |              | D5 |               | DS | Rea                   |

|                 |                                          | 9G  |                              | 90 |                    | 9Q |              | 90 |              | De |               | De |                       |

|                 |                                          | D2  |                              | 70 |                    | 70 |              | 70 |              | 7Q |               | 7Q |                       |

|                 | AD0<br>AD1                               | 0   | ı                            | _  |                    | 0  | ı            |    |              | 0  |               | _  |                       |

| ess.            | AD2 AD1<br>AD3 AD2                       | -   |                              | -  |                    | 0  |              | 0  |              | -  |               | -  |                       |

| Address         | AD2<br>AD3                               | -   |                              | -  |                    | 0  |              | 0  |              | 0  |               | 0  |                       |

|                 | AD3<br>AD4                               | 0   |                              | 0  |                    | _  |              | -  |              | _  |               | _  |                       |

|                 | SAB 8085 Mode: AD3<br>SAB 8086 Mode: AD4 | 07  |                              | 00 |                    | 8  |              | 00 |              | 8  |               | 8  |                       |

|                 | AB 8085<br>AB 8086                       | 2   |                              | 10 |                    | 2  |              | 10 |              | 2  |               | 5  |                       |

|                 | တ တ                                      | [2] | Word                         | D2 | <u>_</u>           | D2 |              | D2 |              | D2 |               | D2 | er 2                  |

| gisters         |                                          | L3  | Disable                      | 23 | er Buffe           | D3 | Port 1       | 23 | Write Port 2 | D3 | imer 1        | D3 | r/Count               |

| Write Registers |                                          | 7   | Interrupt-Level Disable Word | 72 | Transmitter Buffer | P4 | Write Port 1 | 8  | Write        | 2  | Write Timer 1 | 74 | Write Timer/Counter 2 |

|                 |                                          | L5  | Interru                      | 25 | <del> -</del>      | DS |              | D2 |              | DS |               | DS | Wri                   |

|                 |                                          | 97  |                              | 90 |                    | 9Q |              | 90 |              | De |               | 9Q |                       |

|                 |                                          | 17  |                              | D7 |                    | D7 |              | D7 |              | D7 |               | D7 |                       |

|                 |                                          |     |                              |    |                    |    |              |    |              |    |               |    |                       |

|                                                                             |    | _                     |              |               |          | _             |     |                   |

|-----------------------------------------------------------------------------|----|-----------------------|--------------|---------------|----------|---------------|-----|-------------------|

|                                                                             | 00 |                       | 00           |               | 8        |               | 出   |                   |

|                                                                             | 10 |                       | 10           |               | 10       |               | OE  |                   |

|                                                                             | D2 | 3r 3                  | D2           |               | D2       |               | H   | ]<br>  .          |

| Read Registers                                                              | 23 | /Counte               | D3           | imer 4        | D3       | imer 5        | BD  | legister          |

| Read Re                                                                     | 2  | Read Timer/Counter 3  | 72           | Read Timer 4  | 72       | Read Timer 5  | TRE | Status Register   |

|                                                                             | 50 | Rea                   | DS           |               | D5       |               | TBE |                   |

|                                                                             | 90 |                       | 9Q           |               | 90       |               | RBF |                   |

|                                                                             | 70 |                       | D7           |               | 10       |               | Z   |                   |

| AD0<br>AD1                                                                  | 0  | •                     | -            | '             | 0        | •             | _   |                   |

| Address<br>AD2 AD1<br>AD3 AD2                                               | 0  |                       | 0            |               | <b>—</b> |               | -   |                   |

| Add<br>AD2<br>AD3                                                           | -  |                       | -            |               | -        |               | -   |                   |

| AD3<br>AD4                                                                  | -  |                       | <del>-</del> |               | -        |               | -   |                   |

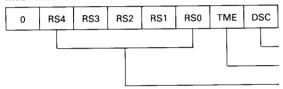

| Address<br>SAB 8085 Mode: AD3 AD2 AD1 AD0<br>SAB 8086 Mode: AD4 AD3 AD2 AD1 | 8  |                       | D0           |               | D0       |               | DSC |                   |

| AB 8085<br>AB 8086                                                          | 10 |                       | D1           |               | D1       |               | TME |                   |

|                                                                             | D2 | er 3                  | D2           |               | D2       | ;             | RSO | 70                |

| egisters                                                                    | D3 | r/Count               | D3           | imer 4        | D3       | imer 5        | RS1 | ion Wor           |

| Write Registers                                                             | D4 | Write Timer/Counter 3 | 72           | Write Timer 4 | D4       | Write Timer 5 | RS2 | Modification Word |

|                                                                             | DS | Wri                   | DS           |               | DS       |               | RS3 | Σ                 |

|                                                                             | 9G |                       | 90           |               | D6       |               | RS4 |                   |

|                                                                             | D7 |                       | D7           |               | D7       |               | 0   |                   |

# **Programming**

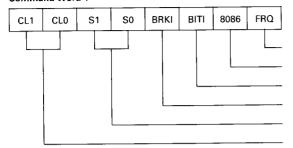

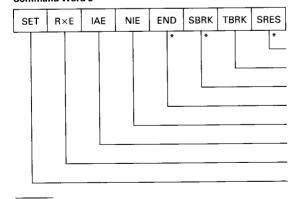

#### Command Word 1

Timer Input Frequency

Processor Type Select

Source for Interrupt Level 1

Break-In Detect Enable

Stop Bit Length

Character Length

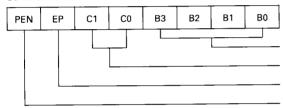

#### Command Word 2

Baud Rate Select

System Clock Prescaler

Odd/Even Parity

Parity Enable

#### **Command Word 3**

Software Reset

Transmit Continuous BREAK

Transmit Single Character BREAK

End of Interrupt

Nested Interrupt Enable

Interrupt Acknowledge Enable

Receive Enable

Bit Set/Reset in Register 3

<sup>\*)</sup> These bits can only be set, they are reset at the end of the operation.

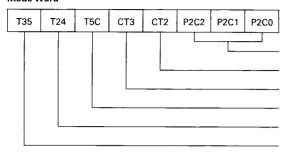

#### Mode Word

Port 2 Control

Timer/Counter 2 Mode

Timer/Counter 3 Mode

Timer 5 Mode

Cascade Counter/Timer 2 and Timer 4

Cascade Counter/Timer 3 and Timer 5

#### Port 1 Control World

Input/Output Mode of Ports 1 Pins

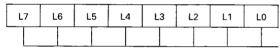

#### Interrupt-Level Enable Word

**Enable Interrupt Levels**

#### Interrupt-Level Disable Word

Disable Interrupt Levels

#### **Determination of Interrupt Level**

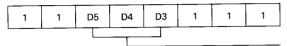

#### Reading the Interrupt Address Register

Interrupt Level

#### Response to INTA

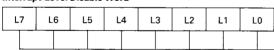

#### SAB 8085-Mode (RST-instruction in response to INTA)

Interrupt Level

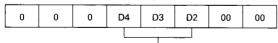

# SAB 8086-Mode (Interrupt Vector in response to second INTA)

Interrupt Level

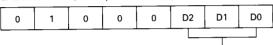

#### Modification Word

Disable Start Bit Check

Transmission Mode Enable

Receiver Sampling Point

#### Status Register

Framing Error/Transmission Mode Indication

Overrun Error

Parity Error

Break Detect or Break-in Detect

Transmitter Register Empty

Transmitter Buffer Empty

Receiver Buffer Full

Interrupt Pending

# **Absolute Maximum Ratings**

Ambient temperature under bias

0 to 70°C

Storage temperature

-65 to +150°C

Voltage on any pin with respect to ground

-0.5 to +7 V

Power dissipation

1 W

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

$T_{\rm A}=0$  to 70°C,  $V_{\rm CC}=5$  V  $\pm$  5%,  $V_{\rm SS}=0$  V (if not otherwise specified)

| Parameter                      | Symbol          | Limi | t values             | 4.1  | Table and Material                              |  |

|--------------------------------|-----------------|------|----------------------|------|-------------------------------------------------|--|

|                                | Symbol          | min. | max.                 | Unit | Test conditions                                 |  |

| Input low voltage              | $V_{\rm IL}$    | -0.5 | 0.8                  | v    | _                                               |  |

| Input high voltage             | $V_{IH}$        | 2.0  | V <sub>CC</sub> +0.5 | V    | _                                               |  |

| Output low voltage             | V <sub>OL</sub> | _    | 0.45                 | V    | $I_{OL} = 2.5  \text{mA}$                       |  |

| Output high voltage            | V <sub>OH</sub> | 2.4  | _                    | V    | $I_{\text{OH}} = -400  \mu \text{A}$            |  |

| Input leakage                  | I <sub>IL</sub> | _    | ±10                  | μА   | $V_{\rm IN} = 0  \rm V  to  V_{\rm CC}$         |  |

| Output leakage current         | $I_{LO}$        | _    | ±10                  | μΑ   | $V_{\text{OUT}} = 0 \text{ V to } V_{\text{C}}$ |  |

| V <sub>cc</sub> supply current | $I_{\rm CC}$    | _    | 190                  | mA   | _                                               |  |

# Capacitance 1)

| Parameter         | Symbol           | Limit value<br>(max.) | Unit | Test conditions                 |

|-------------------|------------------|-----------------------|------|---------------------------------|

| Input capacitance | C <sub>IN</sub>  | 10                    | pF   | $f_{\rm C} = 1  {\rm MHz}$      |

| I/O capacitance   | C <sub>I/O</sub> | 20                    | pF   | Unmeasured pins returned to GND |

<sup>1)</sup> This parameter is periodically sampled and not 100% tested.

## **AC Characteristics**

$T_{\rm A}=0$  to 70°C;  $V_{\rm CC}=+5\,{

m V}\pm5\%$ ;  $V_{\rm SS}=0\,{

m V}$

#### **Test Conditions**

Capacitive load  $C_L = 150 \text{ pF}$

The timings are with respect to the following levels:

H-level: 2.0 V L-level: 0.8 V

Rise and fall times: 20 ns

The timings are valid for an internal clock of 1.024 MHz.

|                                                   |                  |                  | Limi                | t values         |                     |         |                    |

|---------------------------------------------------|------------------|------------------|---------------------|------------------|---------------------|---------|--------------------|

| Parameter                                         | Symbol           | SAB 82           | 256A                | SAB 82           | 256A-2              | Unit    | Test<br>conditions |

|                                                   |                  | min.             | max.                | min.             | max.                | <u></u> |                    |

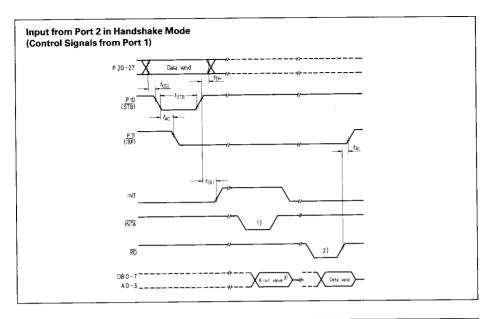

| STB ↓ to IBF ↓                                    | t <sub>AC</sub>  | _                | 300                 |                  | 300                 | ns      | -                  |

| ACK pulse width                                   | t <sub>ACK</sub> | t <sub>ADP</sub> | _                   | t <sub>ADP</sub> | _                   |         | -                  |

| Address stable to data valid                      | t <sub>AD</sub>  | _                | 400                 | -                | 230                 | ns      |                    |

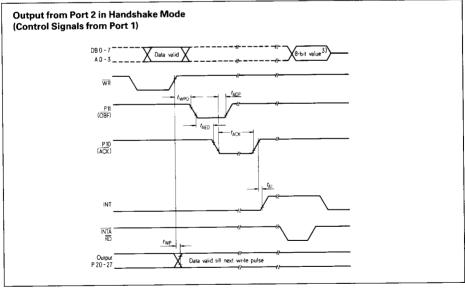

| ACK ↑ to OBF ↓                                    | t <sub>ADP</sub> |                  | 300                 |                  | 300                 | ns      |                    |

| OBF ↓ to ACK ↓                                    | t <sub>AED</sub> | 0                | _                   | 0                | -                   | ns      | -                  |

| ACK ↑ to INT ↑                                    | t <sub>Al</sub>  | -                | 1.5 t <sub>CY</sub> | _                | 1.5 t <sub>CY</sub> | -       | _                  |

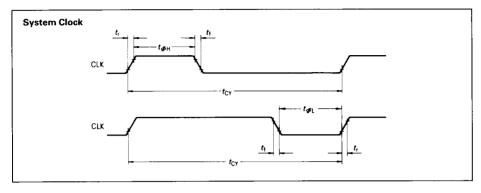

| Address stable to ALE ↓                           | t <sub>AL</sub>  | 50               |                     | 30               | -                   | ns      |                    |

| RD and WR pulse widths                            | $t_{\rm CC}$     | 300              | _                   | 200              | _                   | ns      |                    |

| RD↑ or WR↑ to next ALE↑                           | t <sub>CL</sub>  | 50               | -                   | 25               | _                   | ns      |                    |

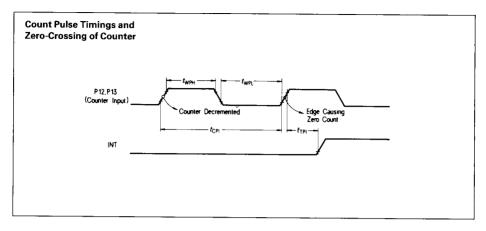

| Counter input cycle time (P12, P13,)              | t <sub>CPI</sub> | 2.2              | -                   | 2.2              | -                   | μs      | _                  |

| CS stable to ALE ↓                                | t <sub>CSL</sub> | 60               | _                   | 10               | -                   | ns      | _                  |

| CTS pulse width for single character transmission | t <sub>CTS</sub> | 1)               | _                   | 1)               | -                   | -       | _                  |

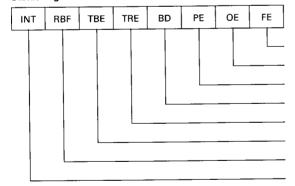

| System clock period                               | t <sub>CY</sub>  | 300              | -                   | 195              | _                   | ns      |                    |

| STB ↑ to INT ↑                                    | t <sub>DEI</sub> | I                | 1.5 t <sub>CY</sub> | -                | 1.5 t <sub>CY</sub> | -       |                    |

| EXTINT ↑ to INT ↑                                 | $t_{DEX}$        | _                | 200                 | -                | 200                 | ns      | _                  |

| STB ↑ to P2 data stable                           | $t_{DH}$         | 10               | _                   | 10               | _                   | ns      | _                  |

| Interrupt request on P17 to INT ↑                 | t <sub>DPI</sub> | _                | 1.5 t <sub>CY</sub> | -                | 1.5 t <sub>CY</sub> | -       |                    |

| P2 data stable before STB ↓                       | t <sub>DSI</sub> | 10               | _                   | 10               | -                   | ns      | _                  |

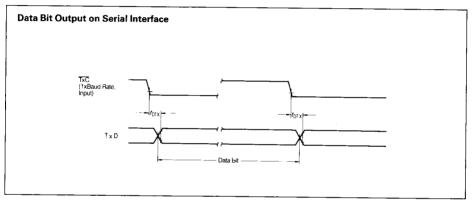

| T×C ↓ to T×D data valid                           | $t_{DTX}$        | _                | 300                 |                  | 300                 | ns      | _                  |

| Data valid before WR↑                             | $t_{\sf DW}$     | 250              | _                   | 150              | _                   | ns      | _                  |

| EXTINT ↓ after INTA ↑ or RD ↑                     | t <sub>HEA</sub> | 30               | _                   | 30               | -                   | ns      | -                  |

| INT ↓ after INTA ↑ or RD ↑                        | t <sub>HIA</sub> | _                | 300                 | _                | 300                 | ns      | -                  |

| CS and address valid after ALE ↓                  | t <sub>LA</sub>  | 50               | -                   | 20               | _                   | ns      | _                  |

| ALE ↓ to RD ↓ or WR ↓                             | t <sub>LC</sub>  | 60               | -                   | 20               | _                   | ns      | <u> </u>           |

| ALE pulse width                                   | $t_{\rm LL}$     | 100              | _                   | 50               | _                   | ns      | <u> </u>           |

Notes see next page.

|                                                        |                      |                 | Lim  | it values       |          |      |                    |

|--------------------------------------------------------|----------------------|-----------------|------|-----------------|----------|------|--------------------|

| Parameter                                              | Symbol               | SAB 8           | 256A | SAB 82          | 256A-2   | Unit | Test<br>conditions |

|                                                        |                      | min.            | max. | min.            | max.     |      | Conditions         |

| Pulse width of interrupt request on P17                | t <sub>Pl</sub>      | 1.1             | -    | 1.1             | -        | μs   | -                  |

| Counter 5 load (P15↓) before next clock pulse on P13 ↑ | t <sub>PP</sub>      | 1.1             | -    | 1.1             | _        | μs   | -                  |

| P1, P2 data stable before RD ↓                         | $t_{PR}$             | 300             | _    | 300             | -        | ns   | _                  |

| Data valid after RD ↓                                  | t <sub>RD</sub>      | _               | 200  | -               | 150      | ns   | -                  |

| RD ↓ to data drivers active                            | t <sub>RDE</sub>     | 10              | 100  | 10              | 50       | ns   | -                  |

| Data bus float after RD ↑                              | $t_{RDF}$            | 10              | 100  | 10              | 50       | ns   | -                  |

| RESET pulse width                                      | t <sub>RES</sub>     | 300             | -    | 300             | -        | ns   | <b> </b> -         |

| RD ↑ to IBF ↑                                          | $t_{\rm RI}$         | -               | 300  | -               | 300      | ns   | 1-                 |

| P1, P2 data hold after RD↑                             | t <sub>RP</sub>      | 50              | _    | 50              | -        | ns   | -                  |

| Data bit start to R×C↓                                 | t <sub>RRD</sub>     | 300             | 2)   | 150             | 2)       | ns   | 3)                 |

| RD ↑ or WR ↑ to next<br>RD ↓ or WR ↓                   | t <sub>RV</sub>      | 300             | -    | 150             | -        | ns   | ĈS=low             |

| Serial clock period (32×, 64×)                         | t <sub>SCY</sub>     | 975             | 1-   | 975             | _        | ns   | -                  |

| Serial clock high (32×, 64×)                           | t <sub>SPD</sub>     | 350             | _    | 350             | T        | ns   | <del> </del> -     |

| Serial clock low (32×, 64×)                            | t <sub>SPW</sub>     | 350             | -    | 350             |          | ns   | 1-                 |

| Strobe pulse width                                     | t <sub>STB</sub>     | t <sub>AC</sub> | -    | t <sub>AC</sub> | 1-       | _    | -                  |

| Serial clock period (1×)                               | t <sub>TCY</sub>     | 975             | -    | 975             | _        | ns   | _                  |

| Serial clock high (1×)                                 | $t_{TPD}$            | 350             | -    | 350             | <u> </u> | ns   | -                  |

| Load pulse for counter 5 (P15)-high                    | t <sub>TIH</sub>     | 1.1             | -    | 1.1             | _        | μs   | -                  |

| Load pulse for counter 5 (P15)-low                     | t <sub>TIL</sub>     | 1.1             | _    | 1.1             | -        | μs   | -                  |

| Counter input ↑ (P12, P13) to INT ↑ at terminal count  | $t_{\text{TPI}}$     | -               | 2.5  | -               | 2.5      | μs   | -                  |

| Serial clock low (1)                                   | t <sub>TPW</sub>     | 350             | _    | 350             | _        | ns   | _                  |

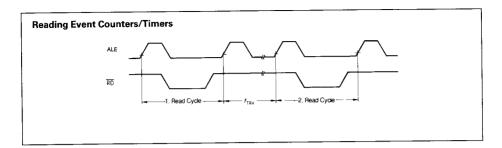

| Time between 2 read cycles onto the same counter/timer | t <sub>TRV</sub>     | 1.1             | -    | 1.1             | -        | μs   | -                  |

| Data hold after WR ↑                                   | $t_{\rm WD}$         | 40              | 1-   | 30              | 1-       | ns   |                    |

| P1, P2 data valid after WR ↑                           | t <sub>WP</sub>      | 1-              | 300  | <b>-</b>        | 300      | ns   | _                  |

| Count clock (P12, P13) high                            | t <sub>WPH</sub>     | 1.1             | 1_   | 1.1             | _        | μS   | 1_                 |

| Count clock (P12, P13) low                             | t <sub>WPL</sub>     | 1.1             | T-   | 1.1             | T        | μs   | _                  |

| OBF ↑ after WR ↓                                       | t <sub>WPO</sub>     | _               | 300  | 1_              | 300      | ns   | 1_                 |

| Clock fall time                                        | t <sub>f</sub>       | _               | 30   | 1_              | 30       | ns   | 1_                 |

| Clock high                                             | $t_{\Phi 	extsf{H}}$ | 105             |      | 65              | -        | ns   | -                  |

| Clock low                                              | $t_{\Phi L}$         | 105             | -    | 65              | 1-       | ns   | 1_                 |

| Clock rise time                                        | t,                   | _               | 30   | _               | 30       | ns   | <del> </del>       |

<sup>1) 1/32</sup> bit length with transmitter clock with a baud rate factor of 32 or 64. 100 ns when baud rate factor = 1

<sup>2) 300</sup> ns + (1/32 bit length)

<sup>3)</sup> Sampling time at bit center

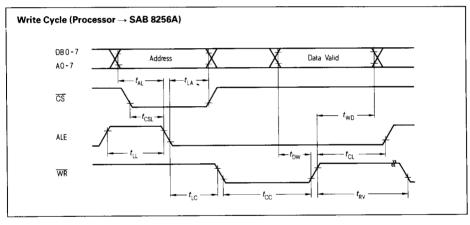

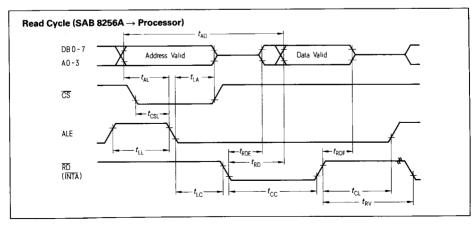

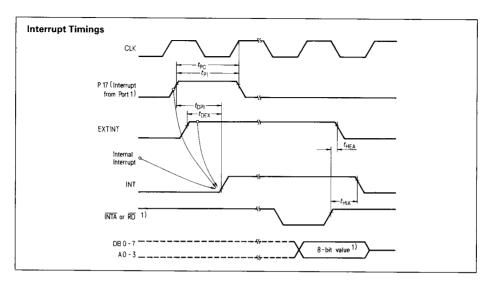

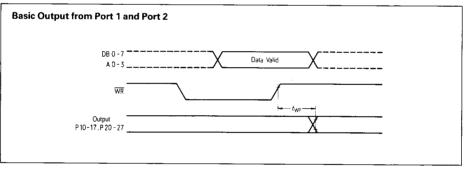

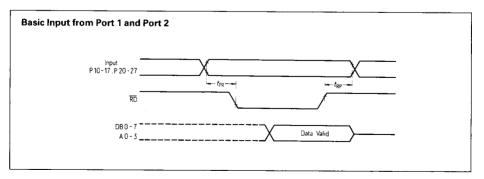

# Waveforms

If INTA is enabled, RST instruction is output on INTA (SAB 8085 mode) or interrupt vector is output on second INTA (SAB 8086 mode) otherwise, interrupt address is output on a read address register operation.

- 1) Instead of INTA, RD can serve as interrupt acknowledge (reading the interrupt address register).

- 2) Read from channel 2.

- 3) If INTA is enabled, RST instruction is output on INTA (SAB 8085 mode) or interrupt vector is output on second INTA (8086 mode). Otherwise, interrupt address is output on a read address register operation.

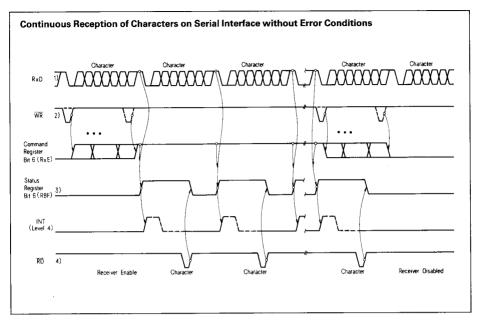

- 1) Character format for this example: 6 data bits with parity bit and one stop bit.

- 2) Set or reset bit 6 of command register 3 (enable receiver)

- 3) Receiver buffer loaded

- 4) Read receiver buffer register

- 5) Receiver is active even though no data is sent or status bit set.

No status bits are altered when RD is active.

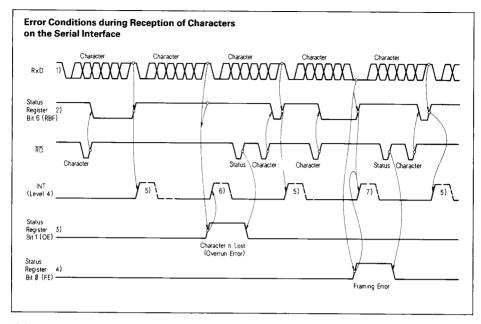

- 1) Character format for this example: 6 data bits without parity and one stop bit

- 2) Receiver buffer register loaded

- 3) Overrun error

- 4) Framing error

- 5) Interrupt from receiver buffer register loading

- 6) Interrupt from overrun error

- 7) Interrupt from framing error and loading receiver buffer register

No status bits are altered when RD is active.

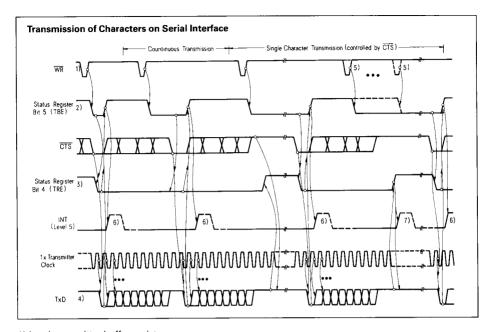

- 1) Load transmitter buffer register

- 2) Transmitter buffer register is empty

- 3) Transmitter register is empty

- 4) Character format for this example: 7 data bits with parity bit and 2 stop bits

- 5) Loading of transmitter buffer register must be completed before CTS goes low

- 6) Interrupt due to transmitter buffer register empty

- 7) Interrupt due to transmitter register empty

No status bits are altered when  $\overline{RD}$  is active.

# **Package Outlines**

# **Ordering Information**

| Туре          | Ordering code | Description                             |

|---------------|---------------|-----------------------------------------|

|               |               | Programmable Multifunction UART (MUART) |

| SAB 8256A-P   | Q 67120-Y43   | 3 MHz system clock (plastic package)    |

| SAB 8256A-2-P | Q 67120-Y59   | 5 MHz system clock (plastic package)    |