# $\mu$ PD9601AD/9602AD CMOS PCM CODEC-FILTER COMBINATION

February 1988

## **Description**

The  $\mu$ PD9601AD and  $\mu$ PD9602AD are PCM codec-filter combo chips, A-law and  $\mu$ -law compatible, respectively. These monolithic CMOS LSIs include phase-locked loops (PLL) that derive internal signal processing clocks from the transmit and receive frame sync clock inputs.

#### **Features**

- ☐ Transmit input operational amplifier

- ☐ Transmit active lowpass filter and switched-capacitor bandpass filter

- ☐ Autozero circuit

- $\square$  Receive unbalanced 600- $\Omega$  output power amplifier

- ☐ Receive switched-capacitor lowpass filter

- ☐ Digital serial I/O interface circuit

- $\square$  A-law (9601AD) and  $\mu$ -law (9602AD) companding

- ☐ Precision reference voltage circuit

- ☐ Synchronous or asynchronous operation

- ☐ Data rate, 64 kb/s to 2.048 Mb/s

- ☐ Low power dissipation

- 50 mW normal mode

- 5 mW power-down or standby mode

- ☐ 16-pin ceramic DIP

#### **Ordering Information**

| Part No.  | Companding | Package Type                 |

|-----------|------------|------------------------------|

| μPD9601AD | A-law      | 16-pin ceramic DIP (300 mil) |

| μPD9602AD | μ-law      |                              |

## **Pin Configuration**

#### 16-Pin Ceramic DIP (300 mil)

| A et 7                |                       |  |

|-----------------------|-----------------------|--|

| Ain + ☐ 1<br>An = ☐ 2 | 15 Dx                 |  |

| GS <sub>X</sub> □ 3   | 14 PDN/BS             |  |

| AGND 4                | 13 DGND               |  |

| Ао∪т □ 5              | 12 🗖 FS <sub>X</sub>  |  |

| <u> </u>              | 11 🗇 FS <sub>R</sub>  |  |

| V <sub>DD</sub> □ 7   | 10 ☐ CLK <sub>X</sub> |  |

| D <sub>R</sub> □ 8    | 9 ☐ CLK <sub>R</sub>  |  |

#### Pin Identification

| Pin No. | Symbol            | Function                                                                                                                                                                                                                                                                             |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | A <sub>IN+</sub>  | Transmit analog input; noninverting input to opamp.                                                                                                                                                                                                                                  |

| 2       | A <sub>IN</sub> — | Transmit analog input; inverting input to opamp.                                                                                                                                                                                                                                     |

| 3       | GSX               | Transmit opamp external gain setting resistor.                                                                                                                                                                                                                                       |

| 4       | AGND              | Analog ground; no internal connection to digital ground.                                                                                                                                                                                                                             |

| 5       | A <sub>0UT</sub>  | Receive analog output from power amplifier; unbalanced 600 $\Omega_{\rm c}$                                                                                                                                                                                                          |

| 6       | LOOP              | Input control for analog loopback test. TTL level; internal pullup. An open or connection to V <sub>SS</sub> disables loopback.                                                                                                                                                      |

| 7       | V <sub>DD</sub>   | Positive 5-volt power supply (+5 $\pm 0.25$ ).                                                                                                                                                                                                                                       |

| 8       | DR                | Receive PCM data input; TTL level.                                                                                                                                                                                                                                                   |

| 9       | CLK <sub>R</sub>  | Receive data clock input, 64 kHz to 2.048 MHz; TTL level. For $CLK_X$ , either synchronous or asynchronous operation can be used; however, for $FS_R$ , only synchronous operation can be used.                                                                                      |

| 10      | CLK <sub>X</sub>  | Transmit data clock input, 64 kHz to 2.048 MHz; TTL level. For $CLK_R$ , either synchronous or asynchronous operation can be used; however, for $FS_\chi$ , only synchronous operation can be used.                                                                                  |

| 11      | FS <sub>R</sub>   | Receive frame sync clock input. TTL level; internal pullup.                                                                                                                                                                                                                          |

| 12      | FSχ               | Transmit frame sync clock input. TTL level; internal pullup.                                                                                                                                                                                                                         |

| 13      | DGND              | Digital ground; no internal connection to analog ground.                                                                                                                                                                                                                             |

| 14      | PDN/BS            | Control input for power-down (9601AD, 9602AD) and bit steal (9602AD); TTL level. On 9601AD, a low level initiates power-down. On 9602AD, the low level must be maintained for more than seven frames; a low-to-high or high-to-low transition within six frames activates bit steal. |

| 15      | D <sub>X</sub>    | Transmit PCM data output (open drain).                                                                                                                                                                                                                                               |

| 16      | V <sub>SS</sub>   | Negative 5-volt power supply ( $-5 \pm 0.25$ ).                                                                                                                                                                                                                                      |

|         |                   | Negative 5-volt power supply (-5 ±0.25).                                                                                                                                                                                                                                             |

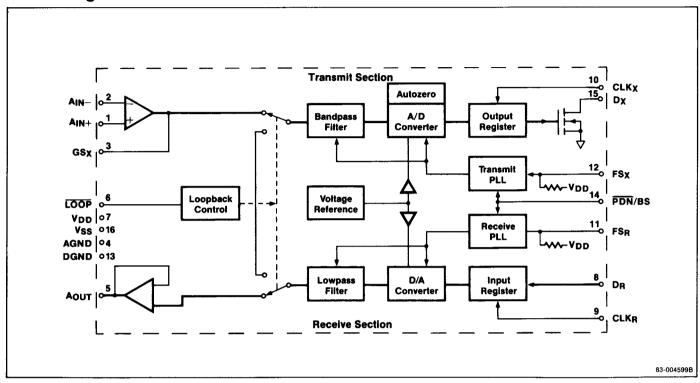

#### **Block Diagram**

#### **Operational Description**

#### Power-Up

The  $\mu$ PD9601AD and  $\mu$ PD9602AD have internal reset circuits that protect other devices on the PCM highway during the power-up sequence. For about 5 ms after power is applied, digital output D<sub>X</sub> is held in a high-impedance state. Analog circuits such as filters, sample-and-hold, and D/A converters begin functioning after a 15-ms settling period.

#### **Power-Down Mode**

Setting the  $\overline{PDN}/BS$  pin to TTL low level initiates the power-down mode. Digital output  $D_X$  goes to high-impedance state and all circuits are disabled except the power-down controller, data clocks, frame sync buffers, and PLLs.

A TTL high level on the PDN/BS pin restores normal operation after the same delays as in power-up, but without the PLL lock-in time.

#### Standby Mode

In standby mode, each section is powered down independently by an open circuit or a TTL low level on  $FS_X$  (transmit section) or  $FS_R$  (receive section).

#### **PCM Data Transmission**

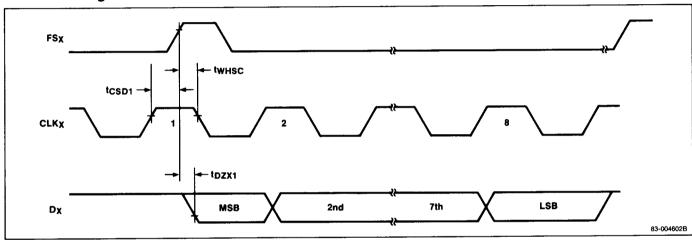

As shown in the transmit 1 timing waveform, if  $FS_X$  is high at the rising edge of  $CLK_X$ , the MSB of the channel PCM word is output at the  $D_X$  pin. Similarly, bits 2 through 8 are output at the next seven rising edges of  $CLK_X$ , after which the  $D_X$  pin is restored to the high-impedance state.

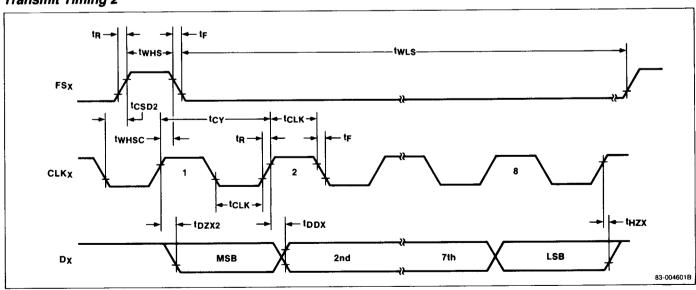

The transmit 2 timing waveform shows the condition in which  $CLK_X$  leads  $FS_X$ . In either transmit 1 or transmit 2, the overlapping high-level width of the two clocks is at least 100 ns.

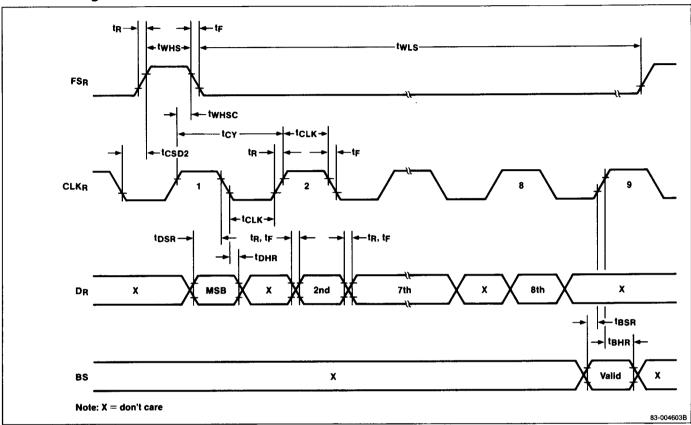

The receive timing waveforms are similar to the transmit timing waveforms except data is clocked in and latched on the falling edge of CLK<sub>B</sub>.

#### Bit Stealing, µPD9602AD Only

Over a I2-frame interval, in frames 1-5 and 7-11, the receive section decodes the vf information in the 8-bit channel pcm words. In signaling frames 6 and 12, the LSB (bit 8) is assigned to convey the channel signaling state. (Bit 8 is "stolen," leaving just 7 bits for vf information.) Although the  $\mu$ PD9602AD does not have a channel signaling interface, it performs 7-bit vf decoding in signaling frames 6 and 12. Design of the D/A converter minimizes the deterioration of gain tracking and signal-to-distortion characteristics resulting from 7-bit vf transmission in one frame out of every six.

To activate bit stealing, the associated digital equipment applies a control signal to the PDN/BS pin. As shown in the receive timing waveforms, the BS signal is low and high in alternate signaling frames. In the next time slot after bit 8 of each channel pcm word in signaling frames, a pulse in the BS signal tells the decoder to ignore bit 8 and decode bits 1-7.

If the signal on the  $\overline{PDN}/BS$  pin is a low level for more than seven frames, the  $\mu PD9602AD$  goes into the power-down mode.

#### **Analog Loopback Test**

Setting the  $\overline{LOOP}$  pin to TTL low level establishes the analog loopback test mode in which vf receive is looped to vf transmit internally. A 0-dBm0 digital tone input at  $D_R$  should emerge as a 0-dBm0 digital tone output at  $D_X$ .

The  $\overline{\text{LOOP}}$  pin, which is pulled up internally, should be left open or connected to  $V_{SS}$  when the channel is not in this test mode.

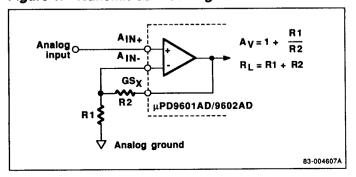

#### **Transmit Gain**

Figure 1 shows the transmit opamp connected in the noninverting mode and gives formulas for voltage gain  $A_V$  and load resistance  $R_L.$  By selecting the values of resistors R1 and R2, voltage gain can be set between 0 and 15 dB. Load resistance should be 10 k $\Omega$  to 20 k $\Omega$ , and load capacitance  $C_L$  should be less than 100 pF.

Figure 1. Transmit Gain Setting

#### Ground

In the board layout, the AGND and DGND pins should be connected together and tied to the analog ground bus beneath the chip at the midpoint between the two pins.

#### **Power-Up Sequence**

In the power-up process, the two power pins and two ground pins should be activated in one of the five sequences listed below.

- V<sub>SS</sub>, AGND, DGND, V<sub>DD</sub>

- V<sub>SS</sub>, AGND-DGND, V<sub>DD</sub>

- V<sub>SS</sub>, V<sub>DD</sub>, AGND-DGND

- V<sub>DD</sub>, V<sub>SS</sub>, AGND-DGND

- AGND-DGND, V<sub>SS</sub>, V<sub>DD</sub>

#### **Absolute Maximum Ratings**

$T_{\Delta} = +25 \,^{\circ}\text{C}; V_{DG} = V_{AG} = 0$

| Parameter                                                  | Symbol            | Rating                             | Conditions                                                                         |  |

|------------------------------------------------------------|-------------------|------------------------------------|------------------------------------------------------------------------------------|--|

| Supply voltage                                             | V <sub>DD</sub>   | −0.3 to +7.0 V                     |                                                                                    |  |

|                                                            | V <sub>SS</sub>   | −7.0 to +0.3 V                     |                                                                                    |  |

| Analog input<br>voltage                                    | V <sub>AIN</sub>  | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ V | Pins A <sub>IN+</sub> ,<br>A <sub>IN</sub> -, GS <sub>X</sub> ,<br>GS <sub>R</sub> |  |

| Digital input<br>voltage                                   | V <sub>DIN</sub>  | $-0.3$ to $V_{DD} + 0.3 V$         |                                                                                    |  |

| Voltage applied<br>to digital output<br>pin D <sub>X</sub> | V <sub>DOUT</sub> | $-0.3$ to $V_{DD} + 0.3$ V         |                                                                                    |  |

| Power<br>dissipation                                       | P <sub>T</sub>    | 500 mW                             |                                                                                    |  |

| Operating<br>temperature                                   | T <sub>OPT</sub>  | 0 to +70°C                         |                                                                                    |  |

| Storage<br>temperature                                     | T <sub>STG</sub>  | 65 to +150°C                       |                                                                                    |  |

| Soldering<br>temperature                                   | T <sub>SOLD</sub> | +260°C                             | Less than 10 seconds                                                               |  |

# $\mu$ PD9601AD/9602AD

**Recommended Operating Conditions**  $T_A = 0 \text{ to } +70 \,^{\circ}\text{C}; \ V_{DD} = +5.0 \text{ V} \pm 0.25 \text{ V}; \ V_{SS} = -5.0 \text{ V} \pm 0.25 \text{ V}; \ V_{DG} = V_{AG} = 0 \text{ (Note 1)}$

|                                                               |                                       |       | •     | Test     |      |                                                   |

|---------------------------------------------------------------|---------------------------------------|-------|-------|----------|------|---------------------------------------------------|

| Parameter                                                     | Symbol                                | Min   | Тур   | Max      | Unit | Conditions                                        |

| Power                                                         |                                       |       |       |          |      |                                                   |

| Supply voltage                                                | V <sub>DD</sub>                       | +4.75 | +5.00 | +5.25    | ٧    |                                                   |

|                                                               | V <sub>SS</sub>                       | -5.25 | -5.00 | -4.75    | ٧    |                                                   |

| Analog                                                        |                                       |       |       | •        |      |                                                   |

| Transmit amplifier                                            |                                       |       |       |          |      |                                                   |

| Input analog voltage                                          | $V_{AX}$                              | -3.0  |       | 3.0      | ٧    | Pin A <sub>IN+</sub>                              |

| Gain setting range                                            | GR <sub>AX</sub>                      | 0     |       | 15       | dB   |                                                   |

| Load resistance                                               | RL <sub>AX</sub>                      | 10    |       |          | kΩ   | Pins GS <sub>X</sub> , A <sub>IN</sub> — (Note 2) |

| Load capacitance                                              | CL <sub>AX</sub>                      |       |       | 100      | pF   |                                                   |

| Receive amplifier                                             |                                       |       |       |          |      |                                                   |

| Load resistance                                               | RLAR                                  | 600   | 160   |          | Ω    |                                                   |

| Load capacitance                                              | CL <sub>AR</sub>                      |       |       | 100      | pF   |                                                   |

| Digital                                                       |                                       |       |       |          |      |                                                   |

| nput at digital pins                                          |                                       |       |       |          |      |                                                   |

| Low voltage                                                   | V <sub>IL</sub>                       | 0     |       | 0.8      | ٧    |                                                   |

| High voltage                                                  | V <sub>IH</sub>                       | 2.0   |       | $V_{DD}$ | ٧    |                                                   |

| Clock                                                         |                                       |       |       |          |      |                                                   |

| Data clock frequency                                          | f <sub>CLK</sub> (1/t <sub>CY</sub> ) | 64    |       | 2048     | kHz  |                                                   |

| Data clock width                                              | tclk                                  | 200   |       |          | ns   |                                                   |

| Frame synchronous clock<br>Frequency                          | f <sub>S</sub>                        |       | 8.0   |          | kHz  |                                                   |

| High-level width                                              | twns                                  | 200   |       |          | ns   |                                                   |

| Low-level width                                               | twls                                  | 8     |       |          | μS   |                                                   |

| Frame sync clock and data clock, overlapping high-level width | twhsc                                 | 100   |       |          | ns   |                                                   |

| Clock rise time                                               | t <sub>R</sub>                        |       |       | 50       | ns   |                                                   |

| Clock fall time                                               | t <sub>F</sub>                        |       |       | 50       | ns   |                                                   |

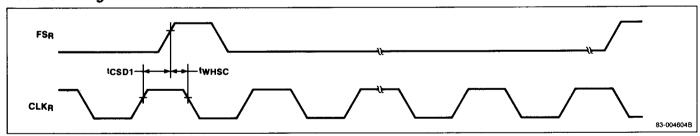

| Synchronous timing margin                                     | t <sub>CSD1</sub>                     |       |       | 100      | ns   |                                                   |

|                                                               | t <sub>CSD2</sub>                     | 40    |       | -        | ns   |                                                   |

| O <sub>R</sub> setup time                                     | t <sub>DSR</sub>                      | 65    |       |          | ns   | Note 3                                            |

| D <sub>R</sub> hold time                                      | t <sub>DHR</sub>                      | 120   |       |          | ns   |                                                   |

| BS setup time                                                 | t <sub>BSR</sub>                      | 200   |       |          | ns   |                                                   |

| BS hold time                                                  | t <sub>BHR</sub>                      | 200   |       |          | ms   |                                                   |

#### Notes:

- (1) Pins AGND and DGND should be connected together close to the device's analog ground pin.

- (2) Pins  $GS_X$  and  $A_{IN-should}$  be connected together if the input gain is 0 dB.

- (3) The rise/fall time of the digital input and clock signals used in timing tests is about 5 ns.

### **DC Characteristics**

$T_A=0$  to  $+70\,^{\circ}\text{C}$ ;  $V_{DD}=+5.0$  V  $\pm0.25$  V;  $V_{SS}=-5.0$  V  $\pm0.25$  V;  $V_{DG}=V_{AG}=0$ ;  $f_{CLKR}=f_{CLKX}=2048$  kHz All outputs are unloaded unless otherwise specified.

|                                |                    |                | Limits   |      |      | Test Conditions                                                                |

|--------------------------------|--------------------|----------------|----------|------|------|--------------------------------------------------------------------------------|

| Parameter                      | Symbol             | Min            | Тур      | Max  | Unit |                                                                                |

| Power                          |                    |                |          |      |      |                                                                                |

| Normal operating current       | I <sub>DD</sub>    |                | 5.0      | 10.0 | mA   |                                                                                |

|                                | IIssI              |                | 5.0      | 10.0 | mA   |                                                                                |

| Power-down current             | I <sub>DDPD1</sub> |                |          | 1.0  | mA   | 100 ms after PDN is set to low                                                 |

|                                | SSPD1              |                |          | 0.2  | mA   |                                                                                |

| Standby current                | I <sub>DDPD2</sub> |                |          | 1.0  | mA   | 100 ms after $FS_X$ and $FS_R$ are set to low                                  |

|                                | IISSPD21           |                |          | 0.2  | mA   |                                                                                |

| Digital Interface              | ,                  |                |          |      |      |                                                                                |

| Digital input current          | l <sub>ID</sub>    | -10            |          | 10   | μΑ   | Pins $\overline{PDN}/BS$ , $D_R$ , $CLK_X$ , $CLK_R$ ; $V_{DIN}=0$ to $V_{DD}$ |

| Pullup current                 | I <sub>IL</sub>    | -100           | -4       | -0.5 | μΑ   | Pins $FS_X$ , $FS_R$ , $\overline{LOOP}$ ; $V_{DIN} = 0 V$                     |

| Digital output leakage current | ال                 | -10            |          | 10   | μΑ   | Pin $D_X$ ; $V_{DIN} = 0$ to $V_{DD}$                                          |

| Output low voltage             | V <sub>OL</sub>    |                |          | 0.4  | ٧    | Pin D <sub>X</sub> ; R <sub>L</sub> = 500 $\Omega$ ; I <sub>OL</sub> = 0.8 mA  |

| Output high voltage            | V <sub>OH</sub>    | $V_{DD} - 0.3$ |          |      | ٧    | Pin D <sub>X</sub> ; I <sub>OH</sub> ≤ 150 <i>μ</i> A                          |

| Digital output capacitance     | C <sub>OD</sub>    |                |          | 15   | pF   | f = 1 MHz                                                                      |

| Digital input capacitance      | C <sub>ID</sub>    |                |          | 10   | pF   |                                                                                |

| Transmit Amplifier             |                    |                |          |      |      |                                                                                |

| Input leakage current          | IB                 | -10            | 0        | 10   | μΑ   | Pins $A_{IN+}$ , $A_{IN-}$ ; $V_{AIN} = -3.0$ to 3.0 V                         |

| Input resistance               | R <sub>IN</sub>    | 50             |          |      | kΩ   | f = 1 MHz                                                                      |

| Input offset voltage           | V <sub>10</sub>    | -500           |          | 500  | mV   | Pin A <sub>IN+</sub>                                                           |

| Output offset voltage          | V <sub>OG</sub>    | -50            |          | 50   | mV   | Pin $GS_X$ ; $R_L = 10 \text{ k}\Omega$                                        |

| Maximum output voltage         | V <sub>OM</sub>    | -3.0           |          | 3.0  | ٧    |                                                                                |

| Input capacitance              | CAIN               |                |          | 10   | pF   |                                                                                |

| Receive Power Amplifier        |                    |                |          |      |      |                                                                                |

| Output offset voltage          | V <sub>OA</sub>    | -50            |          | 50   | mV   | Pin A <sub>OUT</sub> ; D <sub>R</sub> = +0 code                                |

| Maximum output voltage         | V <sub>OM</sub>    | -2.5           | <u> </u> | 2.5  | ٧    | $R_L \ge 600 \Omega$                                                           |

| Output resistance              | R <sub>ORR</sub>   |                | 1        |      | Ω    |                                                                                |

## $\mu$ PD9601AD/9602AD

#### **AC Characteristics**

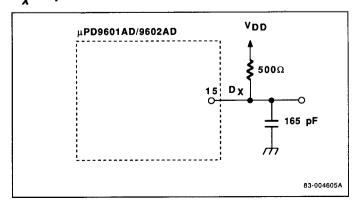

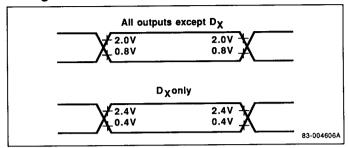

$T_A = 0$  to +70 °C;  $V_{DD} = +5.0$  V  $\pm 0.25$  V;  $V_{SS} = -5.0$  V  $\pm 0.25$  V;  $V_{DG} = V_{AG} = 0$ ;  $f_{CLKR} = f_{CLKX} = 2048$  kHz;  $R_L = 500$  Ω;  $C_L = 165$  pF;  $I_{OL} = 0.8$  mA;  $I_{OH} \le 150$  μA

|                    |                   |     | Limits |     |      |                                   |

|--------------------|-------------------|-----|--------|-----|------|-----------------------------------|

| Parameter          | Symbol            | Min | Тур    | Max | Unit | Test Conditions                   |

| Data enable time 1 | t <sub>DZX1</sub> |     |        | 170 | ns   | Pin $D_X$ ; from $FS_X$ to $D_X$  |

| Data enable time 2 | t <sub>DZX2</sub> |     |        | 170 | ns   | Pin $D_X$ ; from $CLK_X$ to $D_X$ |

| Data delay time    | t <sub>DDX</sub>  |     | ·      | 180 | ns   | Pin D <sub>X</sub>                |

| Data hold time     | t <sub>HZX</sub>  |     | 50     |     | ns   | Pin D <sub>X</sub>                |

Transmission Characteristics,  $\mu$ PD9601AD T<sub>A</sub> = +25 °C; V<sub>DD</sub> = +5.0 V ±0.25 V; V<sub>SS</sub> = -5.0 V ±0.25 V; V<sub>DG</sub> = V<sub>AG</sub> = 0 Analog input signal level V<sub>IN</sub> = 0 dBm0 (f = 820 Hz); analog input gain = 0 dB; digital input signal level = 0 dBm0 (f = 820 Hz)

|                                                            | · <del>- ·</del> · |      |       |      |      |                                                                               |

|------------------------------------------------------------|--------------------|------|-------|------|------|-------------------------------------------------------------------------------|

| Parameter                                                  | Symbol             | Min  | Тур   | Max  | Unit | Test Conditions                                                               |

| Zero Transmission Level                                    | Point              |      |       |      |      |                                                                               |

| Transmit                                                   | 0TLP <sub>X</sub>  |      | +4.02 |      | dBm  |                                                                               |

| Receive                                                    | 0TLP <sub>R</sub>  |      | +4.02 |      | dBm  |                                                                               |

| Gain                                                       |                    |      |       |      |      |                                                                               |

| Transmit gain tolerance                                    | G <sub>X</sub>     | -0.1 |       | +0.1 | dB   | Referenced to $0TLP_X$ ;<br>$V_{DD} = +5 V$ ; $V_{SS} = -5 V$                 |

| Receive gain tolerance                                     | GR                 | -0.1 |       | +0.1 | dB   | Referenced to $0TLP_R$ ;<br>$V_{DD} = +5 \text{ V}$ ; $V_{SS} = -5 \text{ V}$ |

| G <sub>X</sub> variation with temperature and power supply | ΔGχ                | -0.2 |       | +0.2 | dB   | $T_A = 0 \text{ to } +70 ^{\circ}\text{C}$                                    |

| G <sub>R</sub> variation with temperature and power supply | ΔG <sub>R</sub>    | -0.2 |       | +0.2 | dB   |                                                                               |

| <b>Gain Tracking</b><br>Variation of gain with input level |                    |      |       |      |      |                                                                               |

| Transmit gain tracking<br>CCITT G.714, Method 2            | GTX                | -0.2 |       | +0.2 | dΒ   | +3 to -40 dBm0                                                                |

|                                                            |                    | -0.4 |       | +0.4 | dB   | -40 to -50 dBm0                                                               |

|                                                            |                    | -0.8 |       | +0.8 | dB   | -50 to -55 dBm0                                                               |

| CCITT G.714, Method 1                                      | GTX                |      | 0.0   |      | dB   | -10 to -40 dBm0                                                               |

|                                                            |                    |      | 0.0   |      | dB   | -40 to -50 dBm0                                                               |

|                                                            |                    |      | 0.0   |      | dB   | -50 to -55 dBm0                                                               |

## D<sub>X</sub> Output Measurement

Transmission Characteristics,  $\mu$ PD9601AD (cont)

|                                                              |                   |             | Limits |         |       |                                                                                           |

|--------------------------------------------------------------|-------------------|-------------|--------|---------|-------|-------------------------------------------------------------------------------------------|

| Parameter                                                    | Symbol            | Min         | Тур    | Max     | Unit  | Test Conditions                                                                           |

| Gain Tracking (cont)                                         |                   |             |        |         |       |                                                                                           |

| Receive gain tracking                                        | ^ <del>-</del>    |             |        | 100     | 4D    | 1.2 to 40 dPm0                                                                            |

| CCITT G. 714, Method 2                                       | GT <sub>R</sub>   | -0.2        |        | +0.2    | dB    | +3 to -40 dBm0                                                                            |

|                                                              |                   |             |        | +0.4    | dB    | -40 to -50 dBm0                                                                           |

|                                                              |                   | -0.8        |        | +0.8    | dB    | -50 to -55 dBm0                                                                           |

| CCITT G.714, Method 1                                        | GT <sub>R</sub>   | <del></del> | 0.0    |         | dB    | -10 to -40 dBm0                                                                           |

|                                                              |                   |             | 0.0    |         | dB    | -40 to -50 dBm0                                                                           |

|                                                              |                   |             | 0.0    |         | dB    | -50 to -55 dBm0                                                                           |

| <b>Frequency Response</b><br>Gain relative to gain at 820 Hz |                   |             |        |         |       |                                                                                           |

| Transmit section                                             | G <sub>RX1</sub>  |             |        | -24     | dB    | 60 Hz                                                                                     |

|                                                              | G <sub>RX2</sub>  | -2.0        |        | 0       | dB    | 200 Hz                                                                                    |

|                                                              | G <sub>RX3</sub>  | -0.15       |        | +0.15   | dB    | 0.3 to 3.0 kHz                                                                            |

|                                                              | G <sub>RX4</sub>  | -0.65       |        | +0.15   | dB    | 3.2 kHz                                                                                   |

|                                                              | G <sub>RX5</sub>  | -0.8        |        | 0       | dB    | 3.4 kHz                                                                                   |

|                                                              | G <sub>RX6</sub>  |             |        | -6.5    | dB    | 3.78 kHz                                                                                  |

| Receive section                                              | G <sub>RR1</sub>  | -0.15       |        | +0.15   | dB    | 0 to 3.0 kHz                                                                              |

|                                                              | G <sub>RR2</sub>  | -0.65       |        | +0.15   | dB    | 3.2 kHz                                                                                   |

|                                                              | G <sub>RR3</sub>  | -0.8        |        | 0       | dB    | 3.4 kHz                                                                                   |

|                                                              | G <sub>RR4</sub>  |             |        | -6.5    | dB    | 3.78 kHz                                                                                  |

| Noise                                                        |                   |             |        | A - 4.5 |       |                                                                                           |

| Transmit section                                             | N <sub>XP</sub>   |             |        | -80     | dBm0p | A <sub>IN+</sub> is grounded to AGND; input amplifier gain = 0 dB                         |

| Receive section                                              | N <sub>RP</sub>   |             |        | -80     | dBm0p | D <sub>R</sub> = +0 code                                                                  |

| Single-frequency noise                                       | N <sub>SF</sub>   |             |        | -50     | dBm0  | End-to-end testing;<br>CCITT G.712 4.2                                                    |

| Crosstalk, transmit to receive                               | CT <sub>TR</sub>  |             |        | 65      | dB    | A <sub>IN+</sub> = 0 dBm0, 820 Hz; D <sub>R</sub> = lowest positive decode level          |

| Crosstalk, receive to transmit                               | CT <sub>RT</sub>  |             |        | 65      | dB    | A <sub>IN+</sub> is grounded to AGND;<br>D <sub>R</sub> = 0-dBm0, 820-Hz<br>digital input |

| Power supply rejection<br>f = 0.3 to 3 kHZ                   | PSRR <sub>1</sub> | 30          |        |         | dB    | ±100-mV zero-to-peak signal                                                               |

| f = 3 to 4 kHz                                               | PSRR <sub>2</sub> | 30          |        |         | dB    | on V <sub>DD</sub> or V <sub>SS</sub>                                                     |

| f = 4 to 50 kHz                                              | PSRR <sub>3</sub> | 30          |        |         | dB    |                                                                                           |

# $\mu \textbf{PD9601AD/9602AD}$

## Transmission Characteristics, $\mu$ PD9601AD (cont)

|                                                     |                  |     | Limits |            |      |                 |

|-----------------------------------------------------|------------------|-----|--------|------------|------|-----------------|

| Parameter                                           | Symbol           | Min | Тур    | Max        | Unit | Test Conditions |

| Distortion                                          |                  |     |        |            |      |                 |

| Transmit signal-to-<br>distortion ratio             |                  |     |        |            | -    |                 |

| CCITT G.714, Method 2                               | SD <sub>X</sub>  | 36  |        |            | dB   | 0 to -30 dBm0   |

|                                                     |                  | 31  |        |            | dB   | -30 to -40 dBm0 |

|                                                     |                  | 26  |        |            | dB   | -40 to -45 dBm0 |

| CCITT G.714, Method 1                               | SD <sub>X</sub>  |     | 37     |            | dB   | −6 to −27 dBm0  |

|                                                     |                  |     | 35     |            | dB   | -27 to -34 dBm0 |

|                                                     |                  |     | 30     |            | dB   | 34 to40 dBm0    |

|                                                     |                  |     | 15     |            | dB   | -40 to -55 dBm0 |

| Receive signal-to-<br>distortion ratio              |                  |     |        |            |      |                 |

| CCITT G.714, Method 2                               | SD <sub>R</sub>  | 36  |        |            | dB   | 0 to -30 dBm0   |

|                                                     |                  | 31  |        |            | dB   | -30 to -40 dBm0 |

|                                                     |                  | 26  |        |            | dB   | -40 to -45 dBm0 |

| CCITT G.714, Method 1                               | SDR              |     | 37     |            | dB   | -6 to −27 dBm0  |

|                                                     |                  |     | 35     |            | dB   | -27 to -34 dBm0 |

|                                                     |                  |     | 30     |            | dB   | -34 to -40 dBm0 |

|                                                     |                  | -   | 15     |            | dB   | -40 to -55 dBm0 |

| Intermodulation distortion,<br>end-to-end           |                  |     |        |            |      |                 |

| CCITT G.712 (7.1)                                   | IMD <sub>1</sub> |     |        | -38        | dB   |                 |

| CCITT G.712 (7.2)                                   | IMD <sub>2</sub> |     |        | <b>-52</b> | dBm0 |                 |

| Absolute delay, A <sub>IN</sub> to A <sub>OUT</sub> | D <sub>A</sub>   |     |        | 480        | μs   |                 |

| Group delay, A <sub>IN</sub> to A <sub>OUT</sub>    | D <sub>0</sub>   |     |        | 1.40       | ms   | 500 Hz          |

|                                                     |                  |     |        | 0.70       | ms   | 600 Hz          |

|                                                     |                  |     |        | 0.20       | ms   | 1000 Hz         |

|                                                     |                  |     |        | 0.20       | ms   | 2600 Hz         |

|                                                     |                  | **  |        | 1.40       | ms   | 2800 Hz         |

**Transmission Characteristics,**  $\mu$ **PD9602AD**  $T_A = +25$  °C;  $V_{DD} = +5.0$  V  $\pm 0.25$  V;  $V_{SS} = -5.0$  V  $\pm 0.25$  V;  $V_{DG} = V_{AG} = 0$ ; Analog input signal level  $V_{IN} = 0$  dBm0 (f = 1020 Hz); analog input gain = 0 dB; digital input signal level = 0 dBm0 (f = 1020 Hz)

|                                                               |                   | Limits |       |                 |      |                                                                            |  |

|---------------------------------------------------------------|-------------------|--------|-------|-----------------|------|----------------------------------------------------------------------------|--|

| Parameter                                                     | Symbol            | Min    | Тур   | Max             | Unit | Test Conditions                                                            |  |

| Zero Transmission Level                                       | Point             |        |       |                 |      |                                                                            |  |

| Transmit                                                      | 0TLP <sub>X</sub> |        | +3.99 |                 | dBm  |                                                                            |  |

| Receive                                                       | 0TLP <sub>R</sub> |        | +3.99 |                 | dBm  |                                                                            |  |

| Gain                                                          |                   |        |       |                 |      |                                                                            |  |

| Transmit gain tolerance                                       | GX                | -0.1   |       | +0.1            | dB   | Referenced to $0TLP_X$ ; $V_{DD} = +5 \text{ V}$ ; $V_{SS} = -5 \text{ V}$ |  |

| Receive gain tolerance                                        | GR                | -0.1   |       | +0.1            | dB   | Referenced to $OTLP_R$ ; $V_{DD} = +5 \text{ V}$ ; $V_{SS} = -5 \text{ V}$ |  |

| G <sub>X</sub> variation with temperature<br>and power supply | ΔGχ               | -0.2   |       | +0.2            | dB   | $T_A = 0 \text{ to } +70 \text{ °C}$                                       |  |

| G <sub>R</sub> variation with temperature and power supply    | ΔG <sub>R</sub>   | -0.2   |       | +0.2            | dB   |                                                                            |  |

| <b>Gain Tracking</b><br>Variation of gain with input lev      | /el               |        |       |                 |      |                                                                            |  |

| Transmit gain tracking                                        | GTX               | -0.2   |       | +0.2            | dB   | +3 to -40 dBm0                                                             |  |

|                                                               |                   | -0.4   |       | +0.4            | dB   | -40 to -50 dBm0                                                            |  |

|                                                               |                   | -0.8   |       | +0.8            | dB   | −50 to −55 dBm0                                                            |  |

| Receive gain tracking                                         | GTR               | -0.2   |       | +0.2            | dB   | +3 to -40 dBm0                                                             |  |

|                                                               |                   | -0.4   |       | +0.4            | dB   | -40 to -50 dBm0                                                            |  |

|                                                               |                   | -0.8   |       | +0.8            | dB   | -50 to -55 dBm0                                                            |  |

| Frequency Response Gain relative to gain at 1020 H            | lz                |        |       |                 |      |                                                                            |  |

| Transmit section                                              | G <sub>RX1</sub>  |        |       | -24             | dB   | 60 Hz                                                                      |  |

|                                                               | G <sub>RX2</sub>  | 2.0    |       | 0               | dB   | 200 Hz                                                                     |  |

|                                                               | G <sub>RX3</sub>  | -0.15  |       | +0.15           | dB   | 0.3 to 3.0 kHz                                                             |  |

|                                                               | G <sub>RX4</sub>  | -0.65  |       | +0.15           | dB   | 3.2 kHz                                                                    |  |

|                                                               | G <sub>RX5</sub>  | -0.8   |       | 0               | dB   | 3.4 kHz                                                                    |  |

|                                                               | G <sub>RX6</sub>  |        |       | <del></del> 6.5 | dB   | 3.78 kHz                                                                   |  |

| Receive section                                               | G <sub>RR1</sub>  | -0.15  |       | +0.15           | dB   | 0. to 3.0 kHz                                                              |  |

|                                                               | G <sub>RR2</sub>  | -0.65  |       | +0.15           | dB   | 3.2 kHz                                                                    |  |

|                                                               | G <sub>RR3</sub>  | -0.8   |       | 0               | dB   | 3.4 kHz                                                                    |  |

|                                                               | G <sub>RR4</sub>  |        |       | -6.5            | dB   | 3.78 kHz                                                                   |  |

## Transmission Characteristics, $\mu$ PD9602AD (cont)

|                                                     |                   |     | Limits |                 |        |                                                                       |  |

|-----------------------------------------------------|-------------------|-----|--------|-----------------|--------|-----------------------------------------------------------------------|--|

| Parameter                                           | Symbol            | Min | Тур    | Max             | Unit   | Test Conditions                                                       |  |

| Noise                                               |                   | ·   |        |                 |        |                                                                       |  |

| Transmit section                                    | N <sub>XC</sub>   |     |        | 16              | dBrnc0 | $A_{IN+}$ is grounded to AGND; input amplifier gain = 0 dE            |  |

| Receive section                                     | N <sub>RC</sub>   |     |        | 10              | dBrnc0 |                                                                       |  |

| Single-frequency noise                              | N <sub>SF</sub>   |     |        | -50             | dBm0   | End-to-end testing; CCITT G.712 4.2                                   |  |

| Crosstalk, transmit to receive                      | CT <sub>TR</sub>  |     |        | -65             | dB     | $A_{IN+}=0$ dBm0, 1020 Hz; $D_R=$ lowest positive decode level        |  |

| Crosstalk, receive to transmit                      | CT <sub>RT</sub>  |     |        | <del>-6</del> 5 | dB     | $A_{IN+}$ is grounded to AGND; $D_R = 0$ -dBm0, 1020-Hz digital input |  |

| Power supply rejection f = 0.3 to 3 kHz             | PSRR <sub>1</sub> | 30  |        |                 | dB     | ±100-mV zero-to-peak signal on V <sub>DD</sub> or V <sub>SS</sub>     |  |

| f = 3 to 4 kHz                                      | PSRR <sub>2</sub> | 20  |        |                 | dB     |                                                                       |  |

| f = 4 to 50 kHz                                     | PSRR <sub>3</sub> | 30  |        |                 | dB     |                                                                       |  |

| Distortion                                          |                   |     |        |                 |        |                                                                       |  |

| Transmit signal-to-                                 | SD <sub>X</sub>   | 36  |        |                 | dB     | 0 to -30 dBm0                                                         |  |

| distortion ratio,<br>CCITT, G.714, Method 2         |                   | 31  |        |                 | dB     | -30 to -40 dBm0                                                       |  |

|                                                     |                   | 26  |        |                 | dB     | -40 to -45 dBm0                                                       |  |

| Receive signal-to-                                  | SDR               | 36  |        |                 | dB     | 0 to -30 dBm0                                                         |  |

| distortion ratio<br>CCITT G.714, Method 2           |                   | 31  |        |                 | dB     | -30 to -40 dBm0                                                       |  |

|                                                     |                   | 26  |        |                 | dB     | -40 to -45 dBm0                                                       |  |

| Intermodulation distortion                          | IMD <sub>1</sub>  |     |        | -38             | dB     | End-to-end measurement; CCITT G.712 (7.1)                             |  |

|                                                     | IMD <sub>2</sub>  |     |        | <b>-52</b>      | dBm0   | End-to-end measurement; CCITT G.712 (7.2)                             |  |

| Absolute delay, A <sub>IN</sub> to A <sub>OUT</sub> | D <sub>A</sub>    | ·   |        | 480             | μS     |                                                                       |  |

| Group delay, A <sub>IN</sub> to A <sub>OUT</sub>    | D <sub>O</sub>    |     |        | 1.40            | ms     | 500 Hz                                                                |  |

|                                                     |                   |     |        | 0.70            | ms     | 600 Hz                                                                |  |

|                                                     |                   |     |        | 0.20            | ms     | 1000 Hz                                                               |  |

|                                                     |                   |     |        | 0.20            | ms     | 2600 Hz                                                               |  |

|                                                     |                   |     |        | 1.40            | ms     | 2800 Hz                                                               |  |

## **Timing Waveforms**

## **Timing Measurement Points**

## Transmit Timing 1

## Transmit Timing 2

## Timing Waveforms (cont)

## Receive Timing 1

## Receive Timing 2

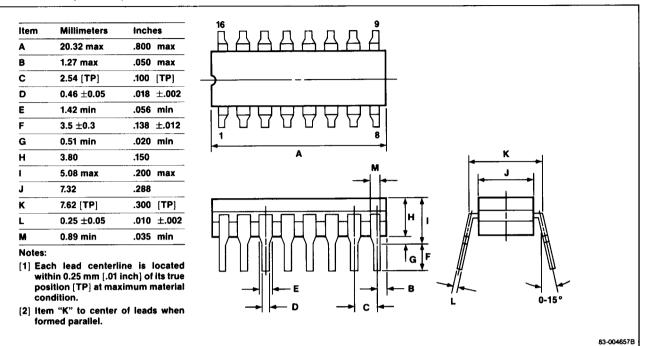

### **Package Drawing**

## 16-Pin Ceramic DIP (300 mil)

401 Ellis Street P.O. Box 7241 Mountain View, CA 94039

TEL 415-960-6000 TWX 910-379-6985

●1988 NEC Electronics Inc./Printed in U.S.A.

For Literature Call Toll Free: 1-800-632-3531

1-800-632-3532 (In California)

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

NECEL-001035 STOCK NO. 220208