# **PCI 9030 Data Book**

# **PCI 9030 Data Book**

Version 1.1

January 2001

Website: http://www.plxtech.com Email: apps@plxtech.com Phone: 408 774-9060

800 759-3735

**Fax**: 408 774-2169

| 2001 PLX T           | echnology, Inc. All rights reserved.                                                                                                                                                                                                                                                     |          |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| nave minor va        | ogy, Inc. retains the right to make changes to this product at any time, without notice. Product at any time, without notice. Product ariations to this publication, known as errata. PLX assumes no liability whatsoever, in any patent or copyright, for sale and use of PLX products. |          |

| PLX Technolog<br>nc. | egy and the PLX logo are registered trademarks and SMARTarget is a trademark of PLX Tec                                                                                                                                                                                                  | hnology, |

| Other brands a       | and names are the property of their respective owners.                                                                                                                                                                                                                                   |          |

| Order Number         | r: 9030-SIL-DB-P1-1.1                                                                                                                                                                                                                                                                    |          |

| Printed in the U     | USA, January 2001                                                                                                                                                                                                                                                                        |          |

### **Contents**

| Figures                                                          | ix          |

|------------------------------------------------------------------|-------------|

| Tables                                                           | . xi        |

| Registers                                                        | xiii        |

| Timing Diagrams                                                  | . XV        |

| Preface                                                          | xvii        |

| Revision History                                                 | (Viii       |

| 1. Introduction                                                  | . 1-1       |

| 1.1. Features                                                    | 1-1         |

| 1.2. Company and Product Background                              |             |

| 1.2.1. PCI 9030 SMARTarget I/O Accelerator                       |             |

| 1.2.2. SMARTarget Technology                                     |             |

| 1.2.3. PCI 9030 Applications                                     |             |

| 1.2.3.1. High-Performance PCI Target Interface                   |             |

| 1.2.3.2. High Performance CompactPCI Adapter Designs             |             |

| 1.2.3.2.1. Hot Swap Ready                                        |             |

| 1.2.3.3. PMC Adapter Cards                                       |             |

| 1.2.4. PCI 9030 SMARTarget Features                              |             |

| 1.2.4.1. Performance Features                                    |             |

| 1.2.4.2. Flexibility Features                                    |             |

| 1.2.4.3. Additional Features                                     |             |

| 1.2.5. PCI 9030 Data Assignment Convention                       |             |

|                                                                  |             |

| 1.2.6. PLX Chip Compatibility                                    |             |

| 1.2.6.1. Pin Compatibility                                       |             |

| 1.2.6.2. Register Compatibility                                  |             |

| 0 DOLand Land Dua                                                | 0 1         |

| 2. PCI and Local Bus                                             | <b>Z</b> -1 |

| 2.1. PCI Bus                                                     | 2-1         |

| 2.1.1. PCI Bus Interface and Bus Cycles.                         |             |

| 2.1.1.1. PCI Target Command Codes                                |             |

| 2.1.1.2. Wait States—PCI Bus                                     |             |

| 2.1.1.3. PCI Target Accesses to an 8- or 16-Bit Local Bus Device |             |

| 2.1.1.4. PCI Bus Little Endian Mode                              |             |

| 2.2. Local Bus                                                   |             |

| 2.2.1. Introduction                                              |             |

| 2.2.1.1 Transactions                                             |             |

| 2.2.1.2. Basic Bus States                                        |             |

| 2.2.1.2. Basic Bus States                                        |             |

| 2.2.3. Local Bus Signals                                         |             |

| 2.2.3.1. Clock                                                   |             |

| 2.2.3.1. Glock                                                   |             |

| 2.2.3.2. Aduress/Data                                            | . ∠-3       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-3                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.2.3.2.2. LD[31:0] (Non-Multiplexed Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 2.2.3.2.3. LA[27:2] (Non-Multiplexed Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 2.2.3.3. Control/Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 2.2.3.3.1. ADS#, ALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.2.3.3.2. LBE[3:0]#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 2.2.3.3.3. LW/R#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.3.3.4. READY#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 2.2.3.3.5. WAITo#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 2.2.3.3.6. LLOCKo#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 2.2.3.3.7. WR#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 2.2.3.3.8. RD#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 2.2.3.3.9. LREQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| 2.2.3.3.10. LGNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.4. Local Bus Interface and Bus Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 2.2.4.1. Local Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 2.2.4.2. Wait State Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 2.2.4.2.1. Wait States—Local Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.4.3. Burst Mode and Continuous Burst Mode (Bterm "Burst Terminate" Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| 2.2.4.3.1. Burst and Bterm Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.4.3.2. Burst-4 Lword Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| 2.2.4.3.2.1. Continuous Burst Mode (Bterm "Burst Terminate" Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 2.2.4.3.3. Partial Lword Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 2.2.4.4. Recovery States (Multiplexed Mode Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.4.5. Local Bus Read Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 2.2.4.6. Local Bus Write Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 2.2.5. Local Bus Big/Little Endian Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 2.2.5.1. 32-Bit Local Bus—Big Endian Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 2.2.5.2. 16-Bit Local Bus—Big Endian Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Serial EEPROM Reset and Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-1                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| 3.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-1                                                                              |

| 3.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-1<br>3-1                                                                       |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| 3.1. Overview. 3.2. Reset Operation . 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-1                                                         |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1<br>3-1<br>3-1<br>3-1<br>3-1                                                  |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input. 3.2.2. Software Reset. 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM. 3.4.1. Vendor ID and Device ID Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-1<br>3-1                                                  |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1                                           |

| 3.1. Overview. 3.2. Reset Operation . 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1<br>. 3-1<br>. 3-1<br>. 3-1<br>. 3-1<br>. 3-1<br>. 3-1                        |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-1<br>                                                                          |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access                                                                                                                                                                                                                                                                                                                                          | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3-3                           |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access                                                                                                                                                                                                                                                                                                                                          | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3-3                           |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support.                                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3<br>3-6<br>3-6               |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access 3.5.1. PCI Bus Access to Internal Registers                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3<br>3-6<br>3-6               |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support.                                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3<br>3-6<br>3-6<br>3-7<br>3-7 |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support 3.7. Serial EEPROM and Configuration Initialization Timing Diagrams.                                                                                                                                                | 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1                                          |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load. 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access. 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support. 3.7. Serial EEPROM and Configuration Initialization Timing Diagrams.  PCI Target (Direct Slave) Operation 4.1. Overview.                                                                                                                         | 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1                                          |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load. 3.4.2.1. Serial EEPROM Load. 3.4.2.2. Recommended Serial EEPROMs. 3.5. Internal Register Access. 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support. 3.7. Serial EEPROM and Configuration Initialization Timing Diagrams.  PCI Target (Direct Slave) Operation  4.1. Overview. 4.2. Direct Data Transfer Mode                                                          | 3-1                                                                              |

| 3.1. Overview. 3.2. Reset Operation 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load 3.4.2.2. Recommended Serial EEPROMs 3.5. Internal Register Access 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support. 3.7. Serial EEPROM and Configuration Initialization Timing Diagrams.  PCI Target (Direct Slave) Operation 4.1. Overview. 4.2. Direct Data Transfer Mode 4.2.1. PCI Target Operation (PCI Master-to-Local Bus Access) | 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1                                          |

| 3.1. Overview. 3.2. Reset Operation. 3.2.1. PCI Bus RST# Input 3.2.2. Software Reset 3.3. PCI 9030 Initialization. 3.4. Serial EEPROM 3.4.1. Vendor ID and Device ID Registers. 3.4.1.1. Serial EEPROM Initialization 3.4.2. Serial EEPROM Operation 3.4.2.1. Serial EEPROM Load. 3.4.2.1. Serial EEPROM Load. 3.4.2.2. Recommended Serial EEPROMs. 3.5. Internal Register Access. 3.5.1. PCI Bus Access to Internal Registers 3.6. New Capabilities Function Support. 3.7. Serial EEPROM and Configuration Initialization Timing Diagrams.  PCI Target (Direct Slave) Operation  4.1. Overview. 4.2. Direct Data Transfer Mode                                                          | 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1 3-1                                          |

|       | 4.2.1.4. PCI Target Delayed Write Mode                                      |      |

|-------|-----------------------------------------------------------------------------|------|

|       | 4.2.1.5. PCI Target Local Bus READY# Timeout Mode                           |      |

|       | 4.2.1.6. PCI Target Transfer                                                |      |

|       | 4.2.1.7.1. PCI Target Local Bus Initialization.                             |      |

|       | 4.2.1.7.2. PCI Target Initialization                                        |      |

|       | 4.2.1.7.3. PCI Target Byte Enables (Multiplexed Mode)                       |      |

|       | 4.2.1.7.4. PCI Target Example                                               |      |

|       | 4.2.1.7.5. PCI Target Byte Enables (Non-Multiplexed Mode)                   |      |

|       | 4.4. Timing Diagrams                                                        |      |

|       | 4.4.1. Serial EEPROM and Configuration Initialization Timing Diagrams       |      |

|       | 4.4.2. PCI Target, Multiplexed and Non-Multiplexed Modes                    | 4-11 |

|       | 4.4.2.1. PCI Target, Multiplexed Mode Only                                  |      |

|       | 4.4.2.2. PCI Target, Non-Multiplexed Mode Only                              | 4-27 |

|       |                                                                             |      |

| 5. Lo | ocal Chip Selects                                                           | 5-1  |

|       | 5.1. Overview                                                               | 5-1  |

|       | 5.2. Chip Select Base Address Registers                                     |      |

|       | 5.3. Procedure for Using Chip Select Base Address Registers                 | 5-2  |

|       |                                                                             |      |

| 6. PC | CI and Local Interrupts and General Purpose I/O                             | 6-1  |

|       | 6.1. Overview                                                               |      |

|       | 6.2. Interrupts                                                             |      |

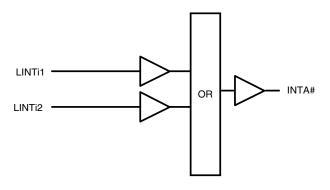

|       | 6.2.1. PCI Interrupts (INTA#)                                               |      |

|       | 6.2.2. Local Interrupt Input (LINTi[2:1])                                   |      |

|       | 6.2.4. Local Power Management Enumerator Set                                |      |

|       | 6.2.5. All Modes PCI SERR# (PCINMI)                                         |      |

|       | 6.3. General Purpose I/O                                                    | 6-2  |

|       |                                                                             |      |

| 7. PC | CI Power Management                                                         | 7-1  |

|       | 7.1. Overview                                                               |      |

|       | 7.2. PCI Power Management Functional Description                            |      |

|       | 7.2.1. Power Management Data_Select, Data_Scale, and Power Data Utilization |      |

|       | 7.3. System Changes Power Mode Example                                      |      |

|       | 7.4. Wake-Up Request Example                                                |      |

|       |                                                                             |      |

| 8. Cc | ompactPCI Hot Swap                                                          | 8-1  |

|       | 8.1. Overview                                                               | 8-1  |

|       | 8.2. Controlling Connection Processes                                       |      |

|       | 8.2.1. Connection Control                                                   |      |

|       | 8.2.1.1. Board Slot Control                                                 |      |

|       | 8.2.1.3. Platform Reset                                                     |      |

|       | 8.2.2. Software Connection Control                                          |      |

|       | 8.2.2.1. Ejector Switch and Blue LED                                        |      |

|       | 8.2.2.2. ENUM#                                                              |      |

|       | 8.2.2.3. Hot Swap Control/Status Register (HS_CSR)                          |      |

|       | 0.7.7.4. FIOL SWAD CADADIIDES BEDISTEL DI DEUDIIDO                          | X-2  |

| 9. PCI V  | ital Product Data (VPD)                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 9.1. Overview9-19.2. VPD Capabilities Register9-19.3. VPD Serial EEPROM Partitioning9-19.4. Sequential Read Only9-19.5. Random Access Read and Write9-2                                                                                                                                                                                                                                                                           |

| 10. Regi  | sters10-1                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | 10.1. New Register Definitions Summary (As Compared to the PCI 9050 and PCI 9052)10-110.2. Register Address Mapping10-210.3. PCI Configuration Registers10-410.4. Local Configuration Registers10-1510.5. Chip Select Registers10-2410.6. Runtime Registers10-25                                                                                                                                                                  |

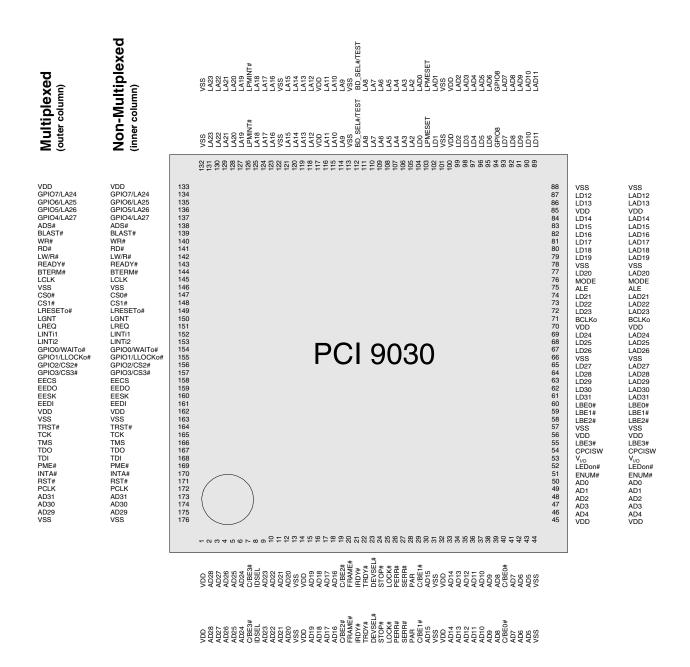

| 11. Pin l | Description11-1                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 11.1. Pin Summary       11-1         11.2. Pinout Common to All Bus Modes       11-2         11.3. Multiplexed Local Bus Mode Pinout       11-9         11.4. Non-Multiplexed Local Bus Mode Pinout       11-11         11.5. Debug Interface       11-13         11.5.1. IEEE 1149.1 Test Access Port (JTAG Debug Port)       11-13         11.5.2. JTAG Instructions       11-13         11.5.3. JTAG Boundary Scan       11-13 |

| 12. Elec  | trical Specifications                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 12.1. General Electrical Specifications12-112.2. Local Inputs12-312.3. Local Outputs12-4                                                                                                                                                                                                                                                                                                                                          |

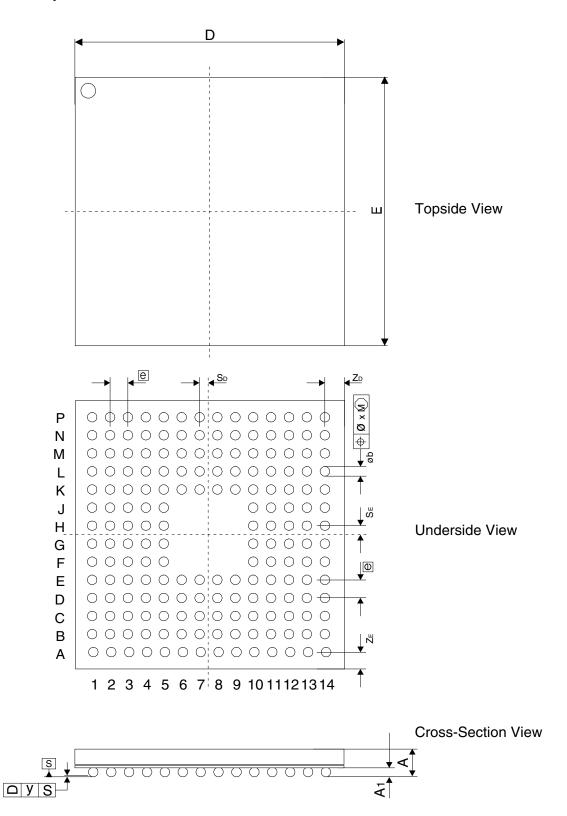

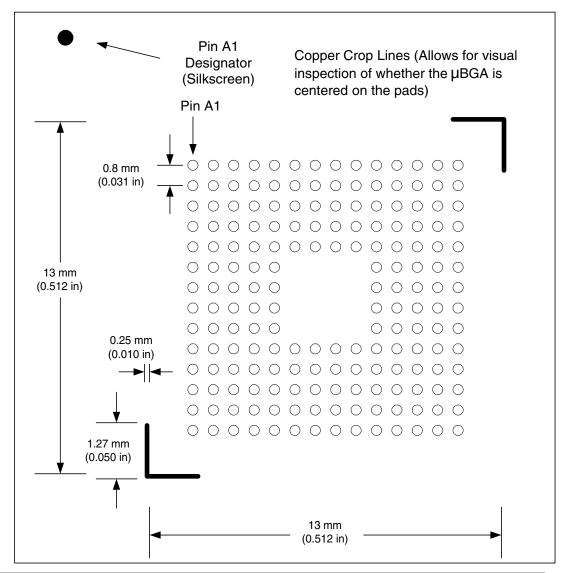

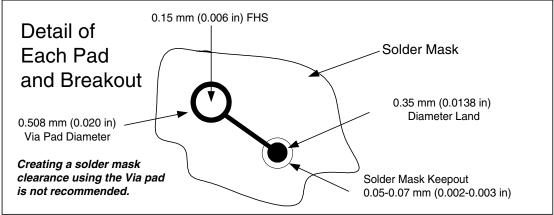

| 13. Phys  | sical Specifications                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | 13.1. 176-Pin PQFP. 13-1<br>13.2. 180-Pin μBGA. 13-4                                                                                                                                                                                                                                                                                                                                                                              |

| A. Gene   | ral Information                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | A.1. Ordering Instructions                                                                                                                                                                                                                                                                                                                                                                                                        |

| Index     | Indox 1                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **Figures**

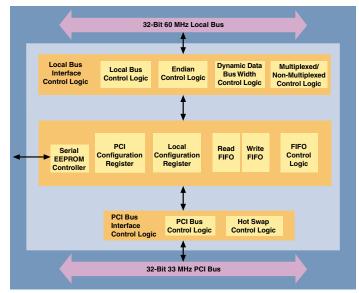

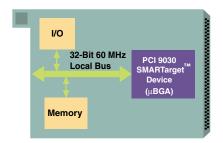

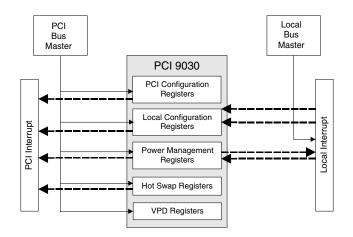

| 1-1 PCI 9030 Internal Block Diagram                                                              | 1-1   |

|--------------------------------------------------------------------------------------------------|-------|

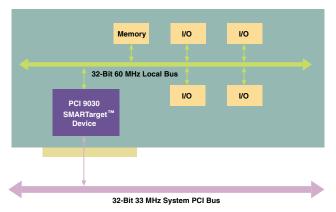

| 1-2 Typical PCI Target Adapter Card                                                              | 1-3   |

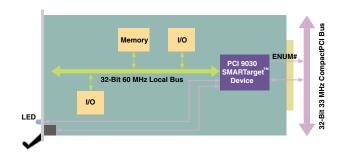

| 1-3 High-Performance CompactPCI Adapter Card                                                     | 1-3   |

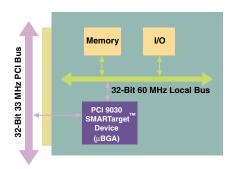

| 1-4 Typical PMC Adapter Card                                                                     | 1-4   |

| 1-5 Typical PCMCIA PC Card                                                                       | 1-4   |

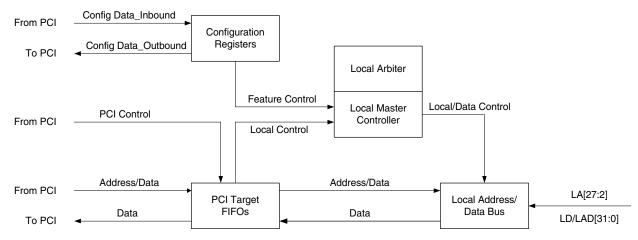

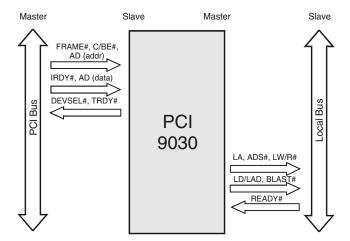

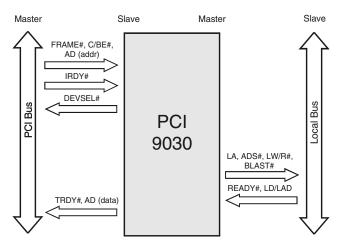

| 2-1 Local Bus Block Diagram                                                                      | 2-2   |

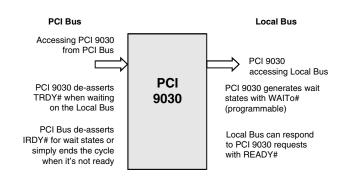

| 2-2 Wait States                                                                                  | 2-4   |

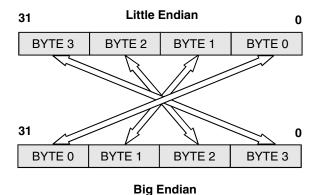

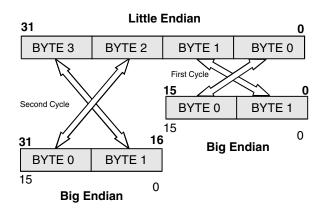

| 2-3 Big/Little Endian—32-Bit Local Bus                                                           | 2-7   |

| 2-4 Big/Little Endian—16-Bit Local Bus                                                           | 2-8   |

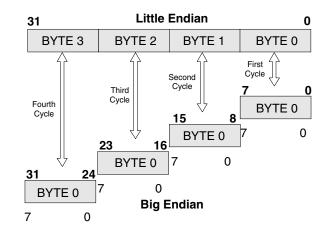

| 2-5 Big/Little Endian—8-Bit Local Bus                                                            | 2-8   |

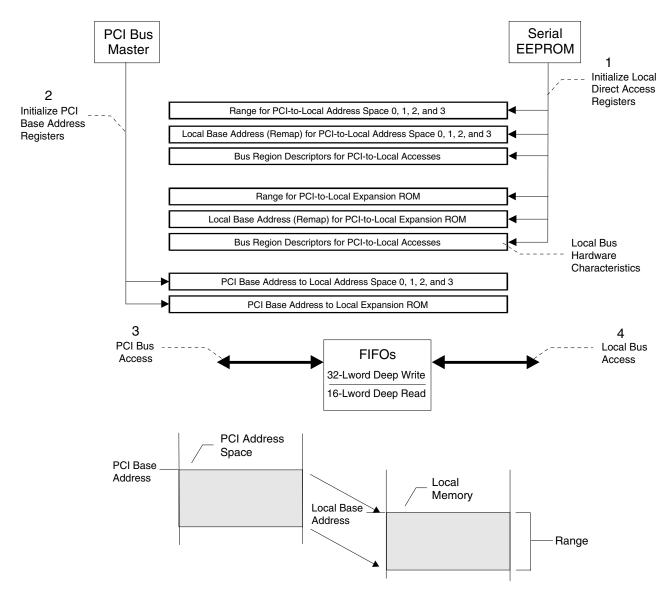

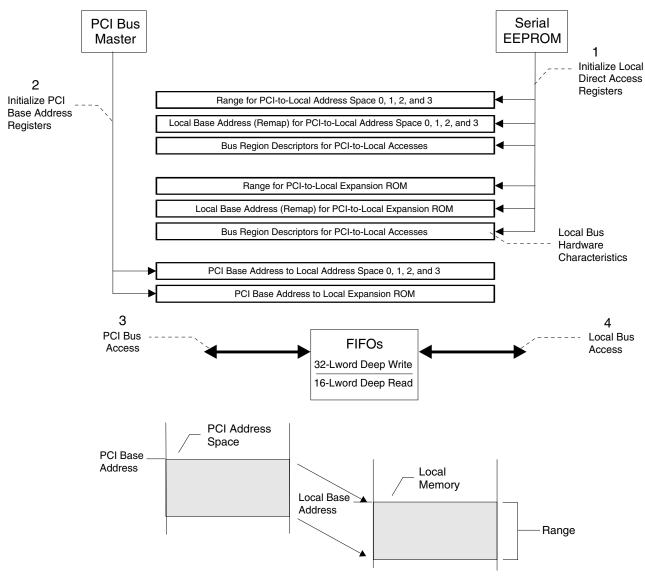

| 3-1 Local Bus PCI Target Access                                                                  | 3-2   |

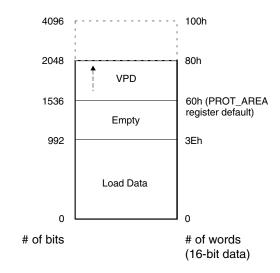

| 3-2 Serial EEPROM Memory Map                                                                     | 3-6   |

| 3-3 PCI 9030 Internal Register Access                                                            | 3-6   |

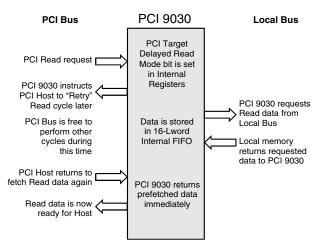

| 4-1 PCI Target Delayed Reads                                                                     | 4-2   |

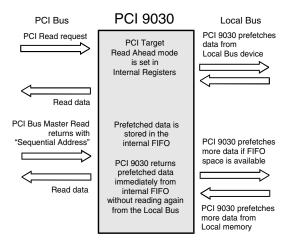

| 4-2 PCI Target Read Ahead Mode                                                                   | 4-2   |

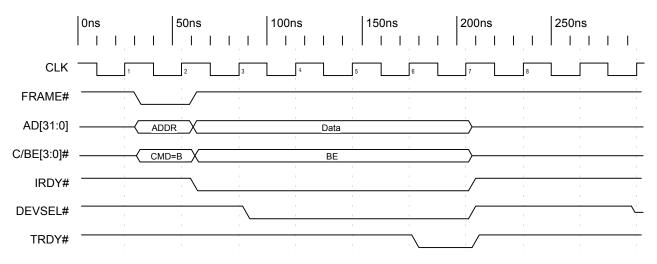

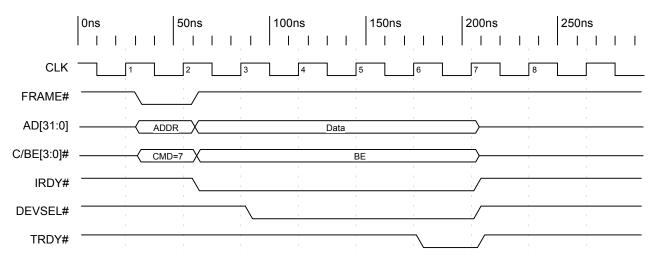

| 4-3 PCI Target Write                                                                             |       |

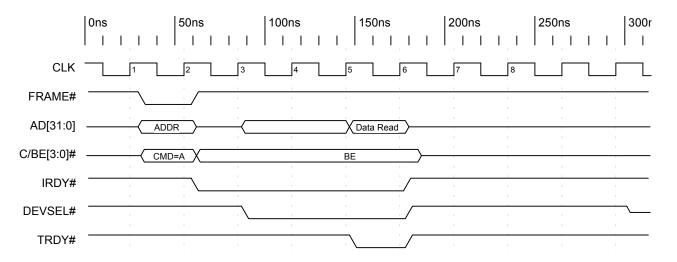

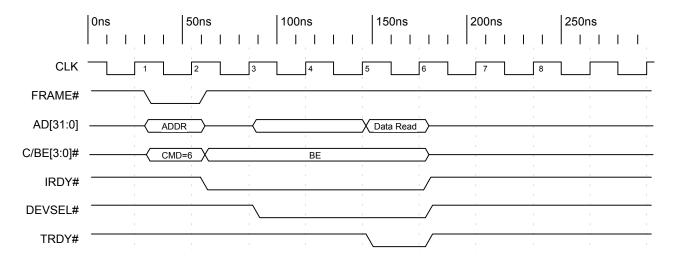

| 4-4 PCI Target Read                                                                              |       |

| 4-5 Local Bus PCI Target Access                                                                  | 4-4   |

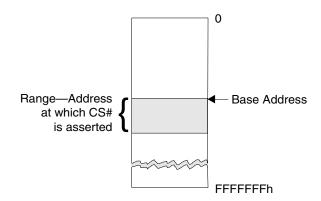

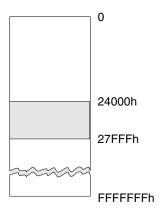

| 5-1 Chip Select Base Address and Range                                                           |       |

| 5-2 Memory Map Example                                                                           |       |

| 6-1 Interrupt and Error Sources                                                                  | 6-1   |

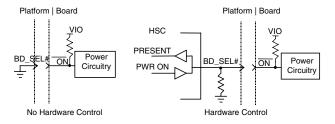

| 8-1 Redirection of BD_SEL#                                                                       | 8-2   |

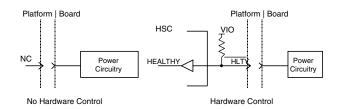

| 8-2 Board Healthy                                                                                | 8-2   |

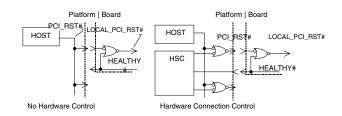

| 8-3 PCI Reset                                                                                    | 8-2   |

| 8-4 Hot Swap Capabilities Register Bit Definition                                                | 8-4   |

| 9-1 VPD Capabilities Register Bit Definition                                                     | 9-1   |

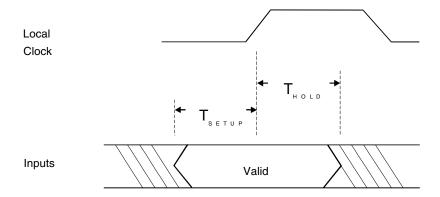

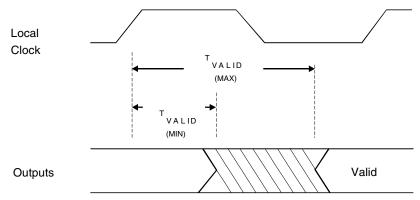

| 12-1 PCI 9030 Local Input Setup and Hold Waveform                                                | 12-3  |

| 12-2 PCI 9030 Local Output Delay                                                                 | 12-4  |

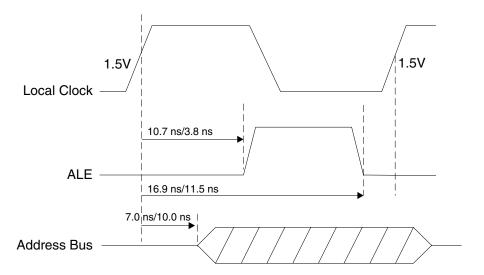

| 12-3 PCI 9030 ALE Output Delay (Min/Max) to the Local Clock at 60 MHz                            |       |

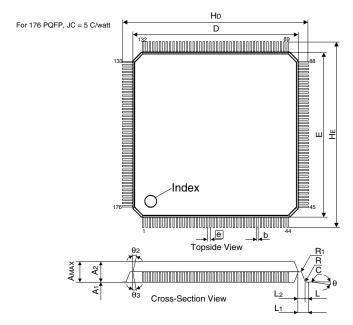

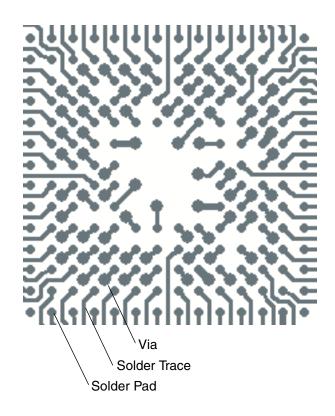

| 13-1 176-Pin PQFP Package Mechanical Dimensions—Topside and Cross-Section Views                  | 13-1  |

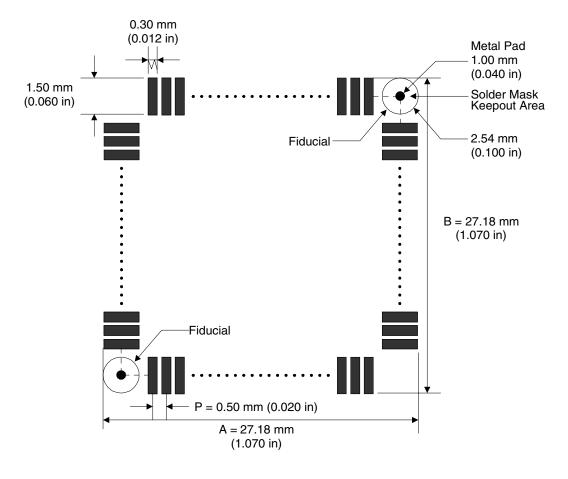

| 13-2 176-Pin PQFP PCB Layout Suggested Land Pattern                                              |       |

| 13-3 176-Pin PQFP Signal and Pinout                                                              |       |

| 13-4 180-Pin $\mu$ BGA Package Mechanical Dimensions—Topside, Underside, and Cross-Section Views | 13-4  |

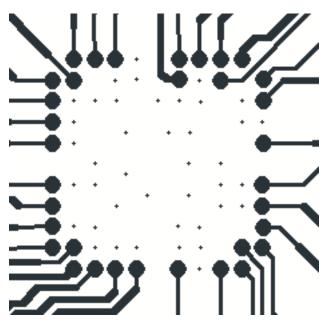

| 13-5 180-Pin µBGA PCB Layout Suggested Land Pattern                                              | 13-6  |

| 13-6 180-Pin μBGA Package Layout—Underside View                                                  | 13-7  |

| 13-7 180-Pin $\mu$ BGA Six-Layer Board Routing Example (Four Routing Layers)—Component Side      | 13-10 |

| 13-8 180-Pin $\mu$ BGA Six-Layer Board Routing Example (Four Routing Layers)—First Inside Layer  | 13-10 |

| 13-9 180-Pin $\mu$ BGA Six-Layer Board Routing Example (Four Routing Layers)—Second Inside Layer | 13-10 |

| 13-10 180-Pin µBGA Six-Layer Board Routing Example (Four Routing Layers)—Solder Side             | 13-10 |

### **Tables**

| 1-1 FIFO Depth                                                                            | 1-5  |

|-------------------------------------------------------------------------------------------|------|

| 1-2 PCI 9030 Data Assignment Convention                                                   | 1-5  |

| 1-3 PCI 9030, PCI 9050, and PCI 9052 Comparison                                           | 1-6  |

| 2-1 PCI Target Command Codes                                                              | 2-1  |

| 2-2 PCI Bus Little Endian Byte Lanes                                                      | 2-1  |

| 2-3 READY Data Transfers                                                                  | 2-3  |

| 2-4 Local Bus Types                                                                       | 2-4  |

| 2-5 Burst and Bterm on the Local Bus                                                      | 2-5  |

| 2-6 Burst-4 Lword Mode                                                                    |      |

| 2-7 PCI Target Single and Burst Reads                                                     | 2-6  |

| 2-8 Byte Number and Lane Cross-Reference—Multiplexed Mode                                 | 2-7  |

| 2-9 Byte Number and Lane Cross-Reference—Non-Multiplexed Mode                             | 2-7  |

| 2-10 Cycle Reference Table                                                                |      |

| 2-11 Upper Lword Lane Transfer—32-Bit Local Bus                                           | 2-7  |

| 2-12 Upper Word Lane Transfer—16-Bit Local Bus                                            | 2-8  |

| 2-13 Lower Word Lane Transfer—16-Bit Local Bus                                            | 2-8  |

| 2-14 Upper Byte Lane Transfer— 8-Bit Local Bus                                            | 2-8  |

| 2-15 Lower Byte Lane Transfer— 8-Bit Local Bus                                            | 2-8  |

| 3-1 Serial EEPROM Guidelines                                                              |      |

| 3-2 Serial EEPROM Register Load Sequence                                                  | 3-4  |

| 3-3 New Capabilities Function Support Features                                            | 3-7  |

| 4-1 Response to FIFO Full or Empty                                                        |      |

| 5-1 Chip Select Base Address Register Signal Programming                                  | 5-1  |

| 8-1 Hot Swap Control                                                                      |      |

| 10-1 New Registers Definitions Summary (As Compared to the PCI 9050 and PCI 9052) $\dots$ |      |

| 10-2 PCI Configuration Register Address Mapping                                           |      |

| 10-3 Local Configuration Register Address Mapping                                         |      |

| 10-4 Chip Select Register Address Mapping                                                 |      |

| 10-5 Runtime Register Address Mapping                                                     |      |

| 11-1 Pin Type Abbreviations                                                               |      |

| 11-2 Power and Ground Pins (176-Pin PQFP)                                                 |      |

| 11-3 Power and Ground Pins (180-Pin µBGA)                                                 |      |

| 11-4 Serial EEPROM Interface Pins                                                         |      |

| 11-5 Test and Debug Pins                                                                  |      |

| 11-6 PCI System Bus Interface Pins                                                        |      |

| 11-7 Local Bus Mode Independent Interface Pins                                            |      |

| 11-8 Multiplexed Bus Mode Interface Pins                                                  |      |

| 11-9 Non-Multiplexed Bus Mode Interface Pins                                              |      |

| 11-10 JTAG Instructions                                                                   |      |

| 11-11 JTAG Infrared Outputs                                                               |      |

| 12-1 Absolute Maximum Ratings                                                             |      |

| 12-2 Operating Ranges.                                                                    |      |

| 12-3 Capacitance (Sample Tested Only)                                                     |      |

| 12-4 Package Thermal Resistance                                                           |      |

| 12-5 Electrical Characteristics over Operating Range                                      |      |

| 12-6 AC Electrical Characteristics (Local Inputs) over Operating Range                    |      |

| 12-7 AC Electrical Characteristics (Local Outputs) over Operating Range                   | 12-4 |

#### **Tables**

| 13-1 176-Pin PQFP Package Mechanical Dimensions (Legend for Figure 13-1)                  | 13-1 |

|-------------------------------------------------------------------------------------------|------|

| 13-2 180-Pin µBGA Package Mechanical Dimensions (Legend for Figure 13-4)                  | 13-5 |

| 13-3 180-Pin µBGA PCI 9030 Pinout                                                         | 13-8 |

| 13-4 180-Pin µBGA Six-Layer Board Routing Example (Four Routing Layers)—Sample Parameters | 13-9 |

| A-1 Available Packages                                                                    | A-1  |

### Registers

| 10-1 (PCIIDR; PCI:00h) PCI Configuration ID                                                       | 10-4  |

|---------------------------------------------------------------------------------------------------|-------|

| 10-2 (PCICR; PCI:04h) PCI Command                                                                 | 10-4  |

| 10-3 (PCISR; PCI:06h) PCI Status                                                                  | 10-5  |

| 10-4 (PCIREV; PCI:08h) PCI Revision ID                                                            | 10-5  |

| 10-5 (PCICCR; PCI:09-0Bh) PCI Class Code                                                          | 10-5  |

| 10-6 (PCICLSR; PCI:0Ch) PCI Cache Line Size                                                       | 10-6  |

| 10-7 (PCILTR; PCI:0Dh) PCI Bus Latency Timer                                                      | 10-6  |

| 10-8 (PCIHTR; PCI:0Eh) PCI Header Type                                                            | 10-6  |

| 10-9 (PCIBISTR; PCI:0Fh) PCI Built-In Self Test (BIST)                                            | 10-6  |

| 10-10 (PCIBAR0; PCI:10h) PCI Base Address Register for Memory Accesses to Local Registers         | 10-6  |

| 10-11 (PCIBAR1; PCI:14h) PCI Base Address Register for I/O Accesses to Local Registers            | 10-7  |

| 10-12 (PCIBAR2; PCI:18h) PCI Base Address Register for Memory Accesses to Local Address Space 0   | 10-7  |

| 10-13 (PCIBAR3; PCI:1Ch) PCI Base Address Register for Memory Accesses to Local Address Space 1.  | 10-8  |

| 10-14 (PCIBAR4; PCI:20h) PCI Base Address Register for Memory Accesses to Local Address Space 2   | 10-8  |

| 10-15 (PCIBAR5; PCI:24h) PCI Base Address Register for Memory Accesses to Local Address Space 3 . | 10-9  |

| 10-16 (PCICIS; PCI:28h) PCI Cardbus CIS Pointer                                                   | 10-9  |

| 10-17 (PCISVID; PCI:2Ch) PCI Subsystem Vendor ID                                                  | 10-9  |

| 10-18 (PCISID; PCI:2Eh) PCI Subsystem ID                                                          | 10-9  |

| 10-19 (PCIERBAR; PCI:30h) PCI Expansion ROM Base                                                  | 10-10 |

| 10-20 (CAP_PTR; PCI:34h) New Capability Pointer                                                   | 10-10 |

| 10-21 (PCIILR; PCI:3Ch) PCI Interrupt Line                                                        | 10-10 |

| 10-22 (PCIIPR; PCI:3Dh) PCI Interrupt Pin                                                         | 10-10 |

| 10-23 (PCIMGR; PCI:3Eh) PCI Min_Gnt                                                               | 10-10 |

| 10-24 (PCIMLR; PCI:3Fh) PCI Max_Lat                                                               | 10-11 |

| 10-25 (PMCAPID; PCI:40h) Power Management Capability ID                                           | 10-11 |

| 10-26 (PMNEXT; PCI:41h) Power Management Next Capability Pointer                                  | 10-11 |

| 10-27 (PMC; PCI:42h) Power Management Capabilities                                                | 10-11 |

| 10-28 (PMCSR; PCI:44h) Power Management Control/Status                                            | 10-12 |

| 10-29 (PMCSR_BSE; PCI:46h) PMCSR Bridge Support Extensions                                        | 10-12 |

| 10-30 (PMDATA; PCI:47h) Power Management Data                                                     | 10-13 |

| 10-31 (HS_CNTL; PCI:48h) Hot Swap Control                                                         | 10-13 |

| 10-32 (HS_NEXT; PCI:49h) Hot Swap Next Capability Pointer                                         | 10-13 |

| 10-33 (HS_CSR; PCI:4Ah) Hot Swap Control/Status                                                   | 10-13 |

| 10-34 (PVPDCNTL; PCI:4Ch) PCI Vital Product Data Control                                          | 10-14 |

| 10-35 (PVPD_NEXT; PCI:4Dh) PCI Vital Product Data Next Capability Pointer                         | 10-14 |

| 10-36 (PVPDAD; PCI:4Eh) PCI Vital Product Data Address                                            | 10-14 |

| 10-37 (PVPDATA; PCI:50h) PCI VPD Data                                                             | 10-14 |

| 10-38 (LAS0RR; 00h) Local Address Space 0 Range Register for PCI-to-Local Bus                     | 10-15 |

| 10-39 (LAS1RR; 04h) Local Address Space 1 Range Register for PCI-to-Local Bus                     | 10-15 |

| 10-40 (LAS2RR; 08h) Local Address Space 2 Range Register for PCI-to-Local Bus                     | 10-16 |

| 10-41 (LAS3RR; 0Ch) Local Address Space 3 Range Register for PCI-to-Local Bus                     | 10-16 |

| 10-42 (EROMRR; 10h) Expansion ROM Range                                                           | 10-17 |

| 10-43 (LAS0BA; 14h) Local Address Space 0 Local Base Address (Remap)                              | 10-17 |

| 10-44 (LAS1BA; 18h) Local Address Space 1 Local Base Address (Remap)                              | 10-17 |

#### Registers

| 10-45 (LAS2BA; 1Ch) Local Address Space 2 Local Base Address (Remap)              | 10-18 |

|-----------------------------------------------------------------------------------|-------|

| 10-46 (LAS3BA; 20h) Local Address Space 3 Local Base Address (Remap)              | 10-18 |

| 10-47 (EROMBA; 24h) Expansion ROM Local Base Address (Remap)                      | 10-18 |

| 10-48 (LAS0BRD; 28h) Local Address Space 0 Bus Region Descriptor                  | 10-19 |

| 10-49 (LAS1BRD; 2Ch) Local Address Space 1 Bus Region Descriptor                  | 10-20 |

| 10-50 (LAS2BRD; 30h) Local Address Space 2 Bus Region Descriptor                  | 10-21 |

| 10-51 (LAS3BRD; 34h) Local Address Space 3 Bus Region Descriptor                  | 10-22 |

| 10-52 (EROMBRD; 38h) Expansion ROM Bus Region Descriptor                          | 10-23 |

| 10-53 (CS0BASE; 3Ch) Chip Select 0 Base Address                                   | 10-24 |

| 10-54 (CS1BASE; 40h) Chip Select 1 Base Address                                   | 10-24 |

| 10-55 (CS2BASE; 44h) Chip Select 2 Base Address                                   | 10-24 |

| 10-56 (CS3BASE; 48h) Chip Select 3 Base Address                                   |       |

| 10-57 (INTCSR; 4Ch) Interrupt Control/Status                                      | 10-25 |

| 10-58 (PROT_AREA; 4Eh) Serial EEPROM Write-Protected Address Boundary             | 10-25 |

| 10-59 (CNTRL; 50h) PCI Target Response, Serial EEPROM, and Initialization Control | 10-26 |

| 10-60 (GPIOC; 54h) General Purpose I/O Control                                    | 10-27 |

| 10-61 (PMDATASEL; 70h) Hidden 1 Power Management Data Select                      | 10-29 |

| 10-62 (PMDATASCALE: 74h) Hidden 2 Power Management Data Scale                     | 10-20 |

### **Timing Diagrams**

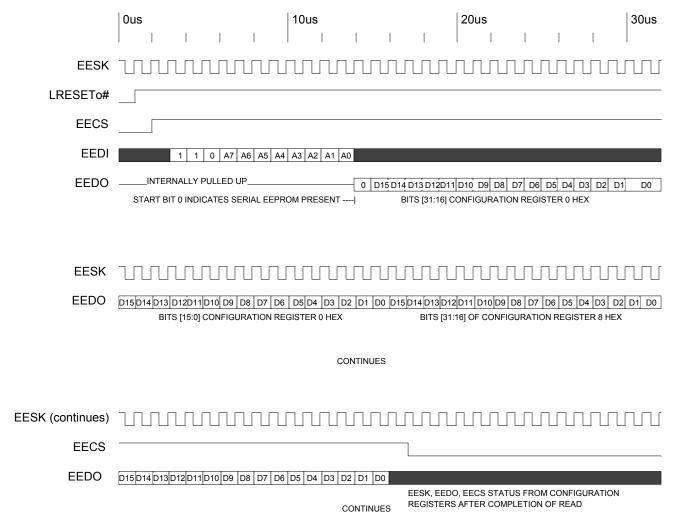

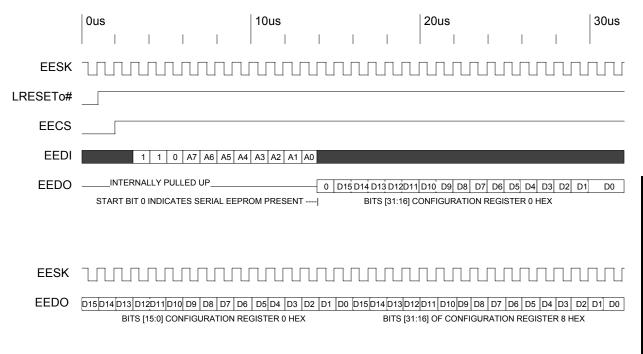

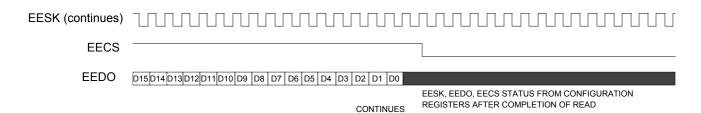

| 3-1 Initialization from Serial EEPROM (2K or 4K Bit)                                                                    | 3-8  |

|-------------------------------------------------------------------------------------------------------------------------|------|

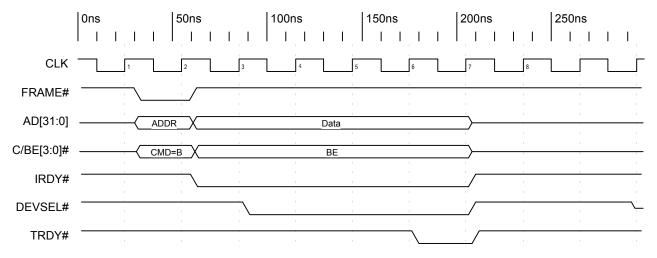

| 3-2 PCI Configuration Write to PCI Configuration Register                                                               | 3-9  |

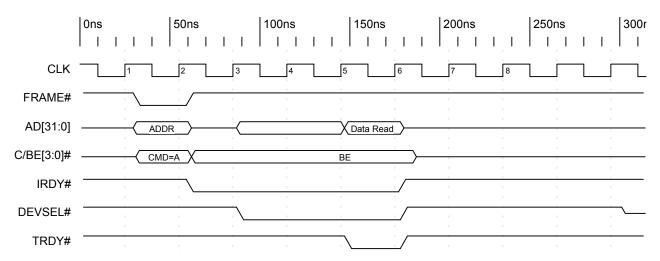

| 3-3 PCI Configuration Read from PCI Configuration Register                                                              | 3-9  |

| 3-4 PCI Memory Write to Local Configuration Register                                                                    | 3-10 |

| 3-5 PCI Memory Read from Local Configuration Register                                                                   | 3-10 |

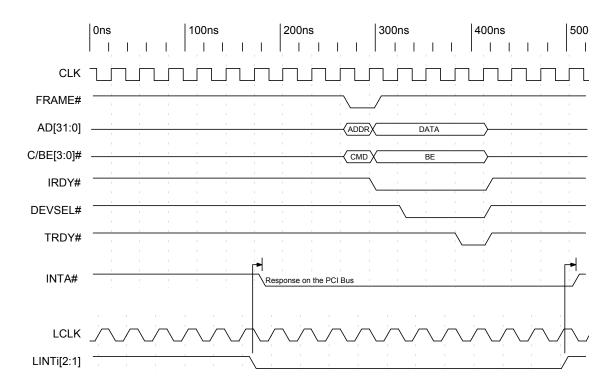

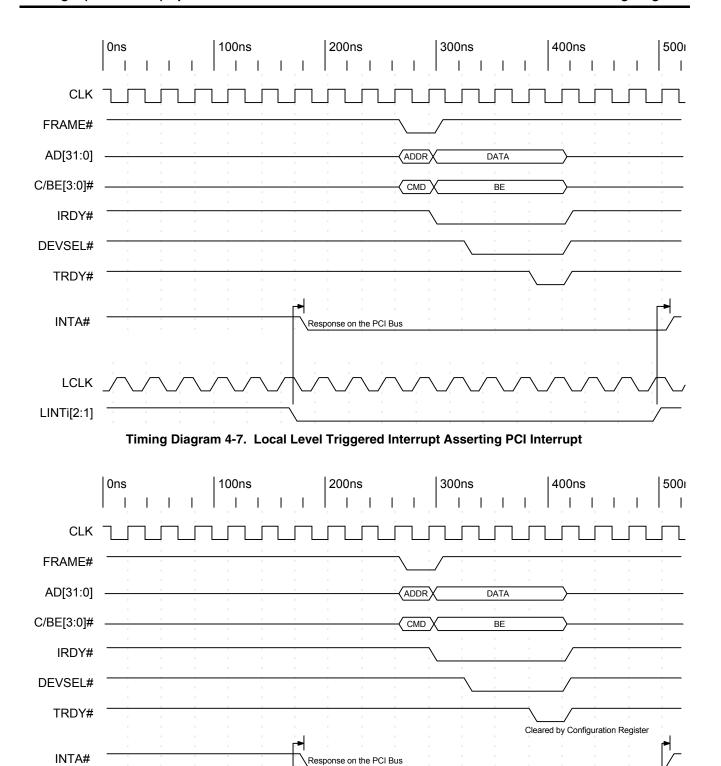

| 3-6 Local Level Triggered Interrupt Asserting PCI Interrupt                                                             | 3-11 |

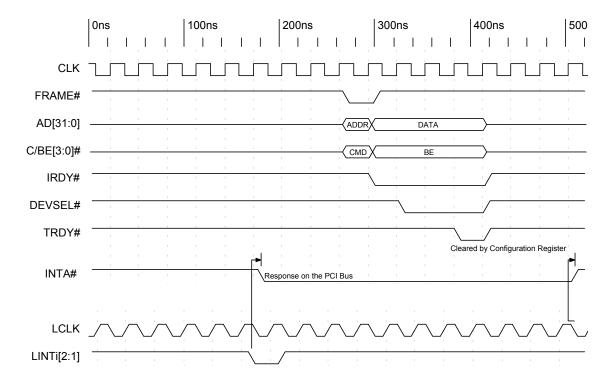

| 3-7 Local Edge Triggered Interrupt Asserting PCI Interrupt                                                              | 3-11 |

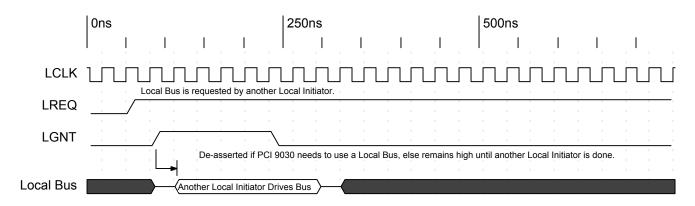

| 4-1 Local Bus Arbitration from the PCI 9030 by Another Local Bus Initiator (LREQ and LGNT)                              | 4-7  |

| 4-2 Initialization from Serial EEPROM (2K or 4K Bit)                                                                    | 4-7  |

| 4-3 PCI Configuration Write to PCI Configuration Register                                                               | 4-8  |

| 4-4 PCI Configuration Read from PCI Configuration Register                                                              | 4-8  |

| 4-5 PCI Memory Write to Local Configuration Register                                                                    | 4-9  |

| 4-6 PCI Memory Read from Local Configuration Register                                                                   | 4-9  |

| 4-7 Local Level Triggered Interrupt Asserting PCI Interrupt                                                             | 4-10 |

| 4-8 Local Edge Triggered Interrupt Asserting PCI Interrupt                                                              | 4-10 |

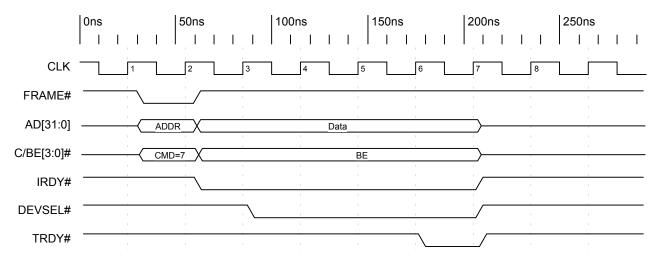

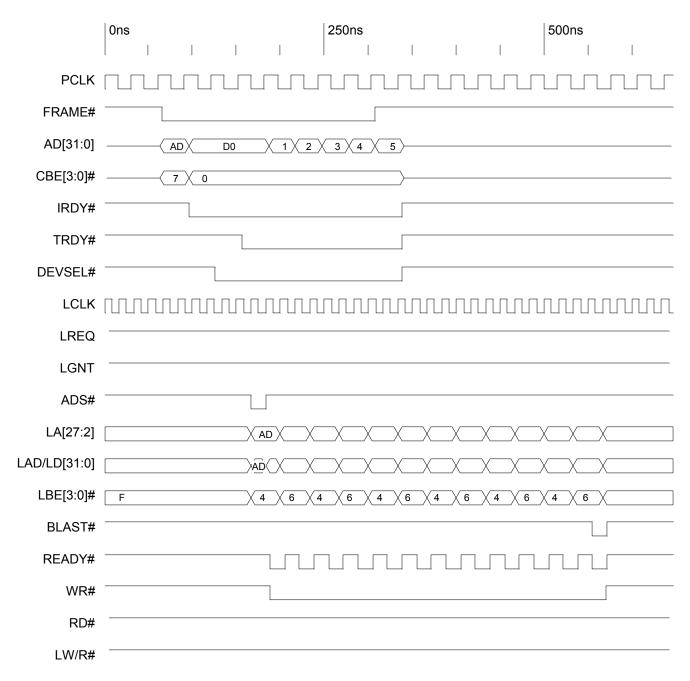

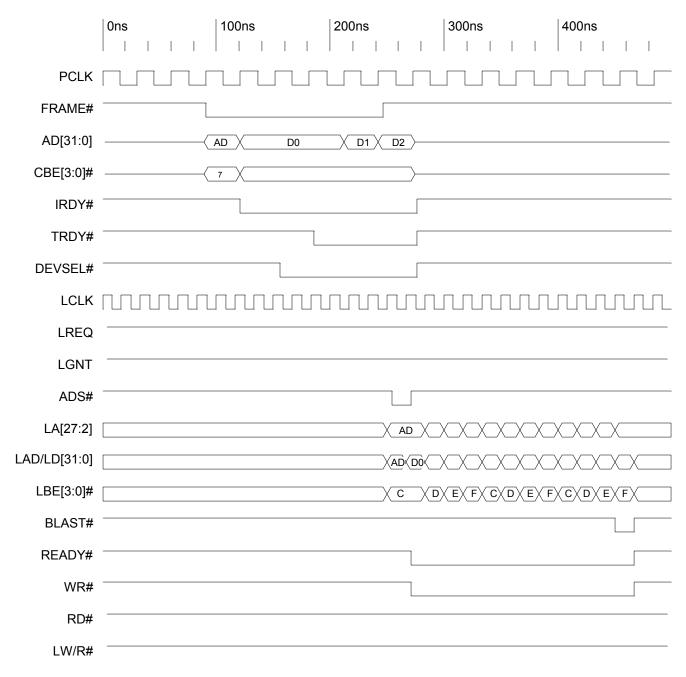

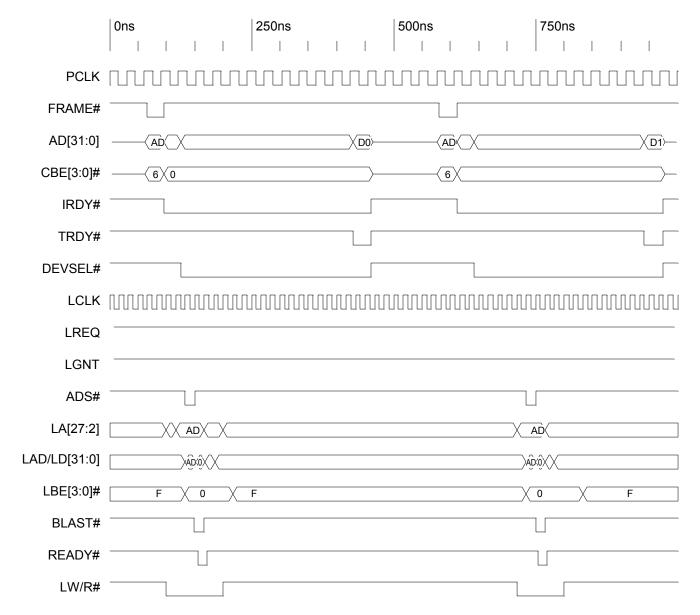

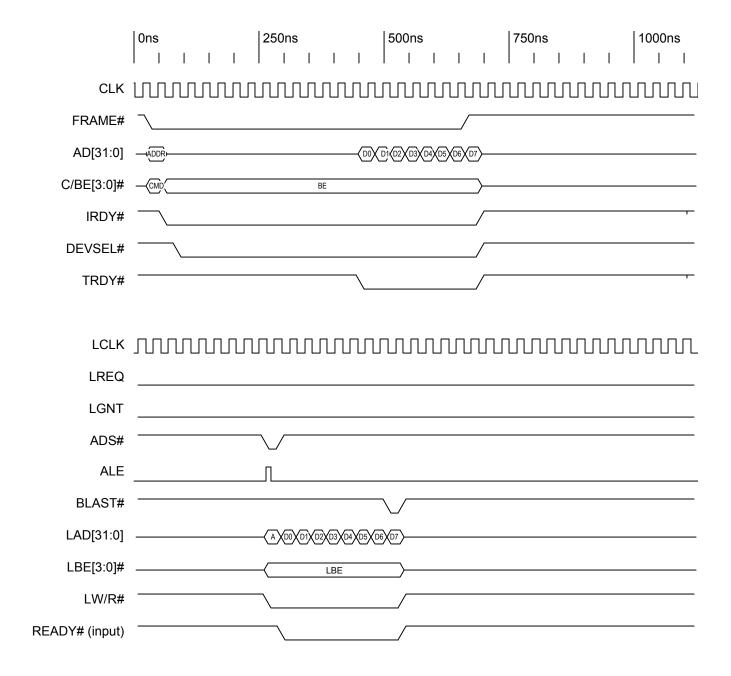

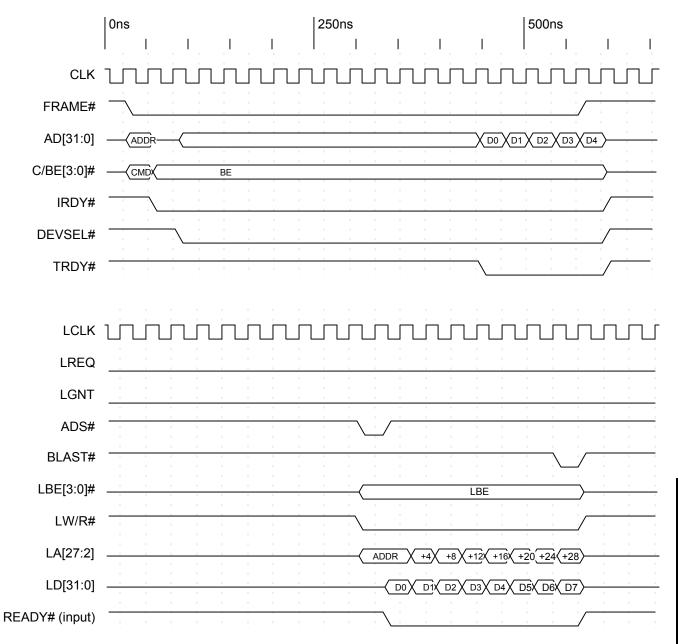

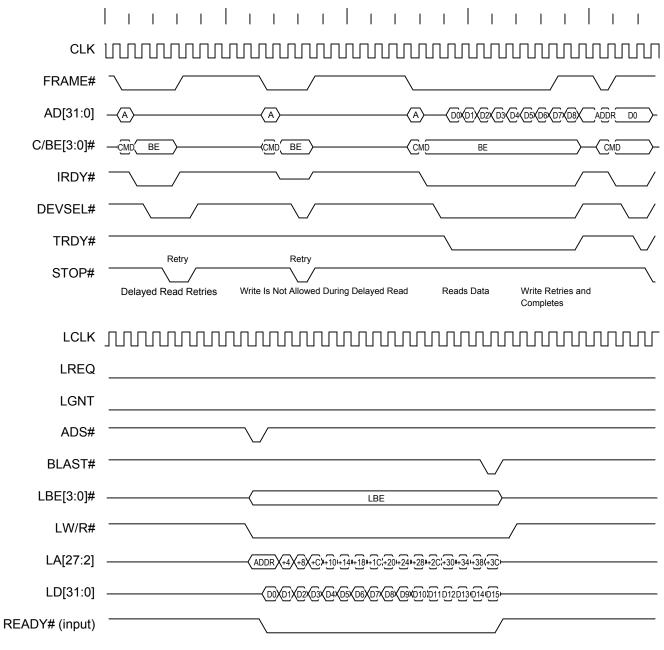

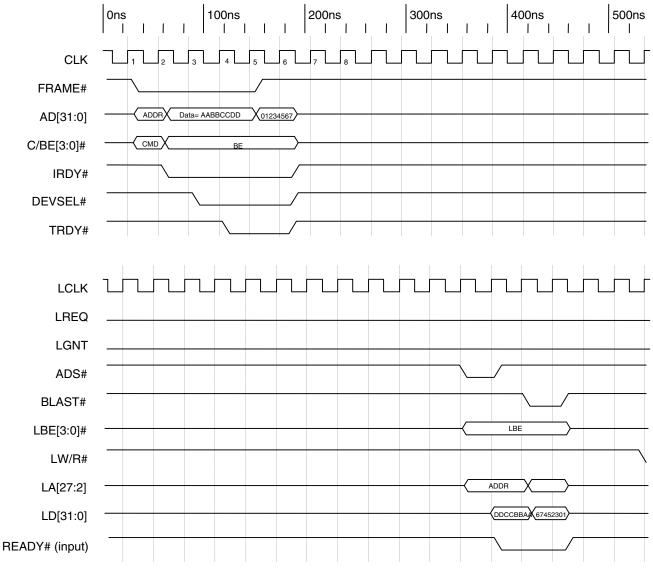

| 4-9 PCI Target Burst Write with Delayed Write and SRAM Chip Select Enabled                                              | 4-11 |

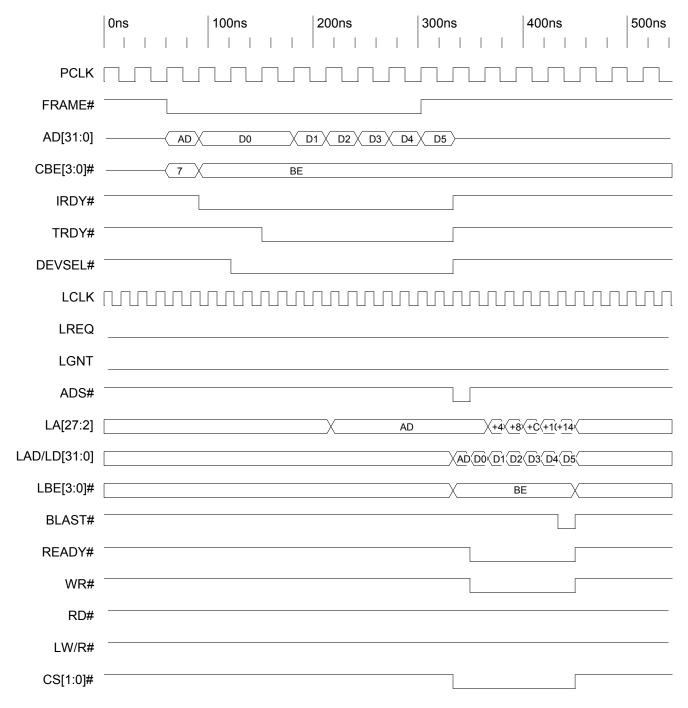

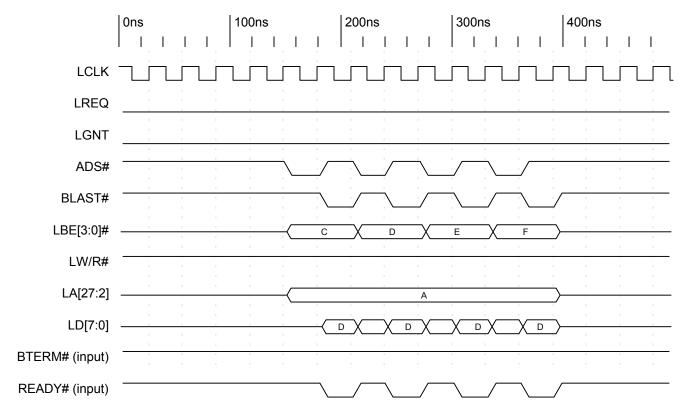

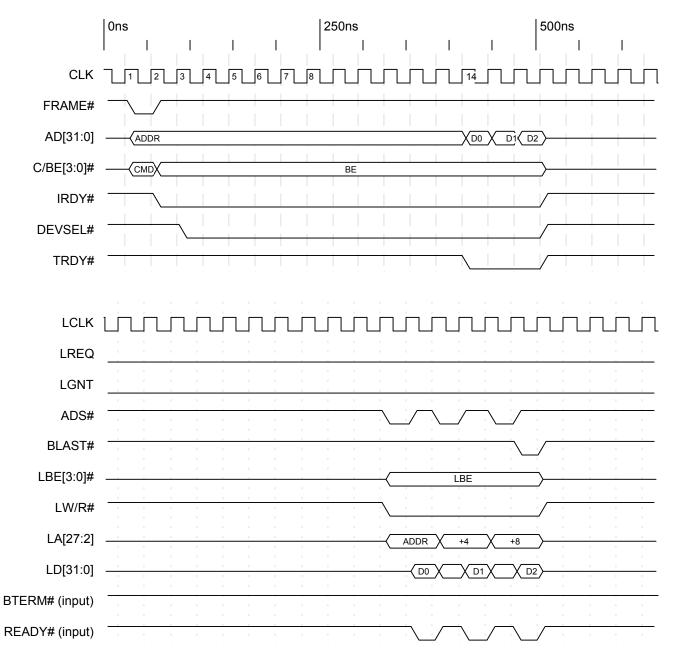

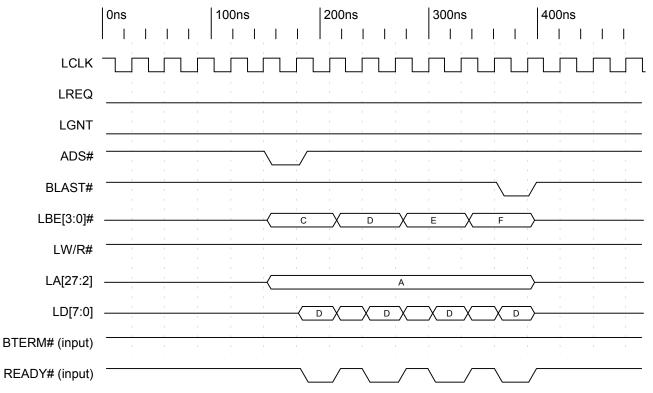

| 4-10 PCI Target Burst Write (32-Bit Local Bus)                                                                          | 4-12 |

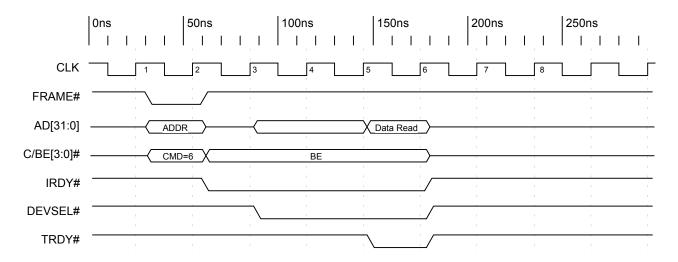

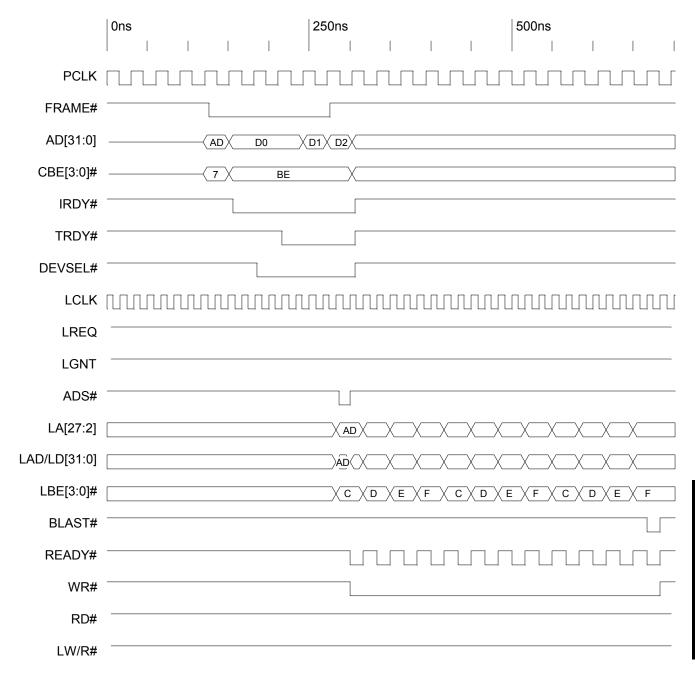

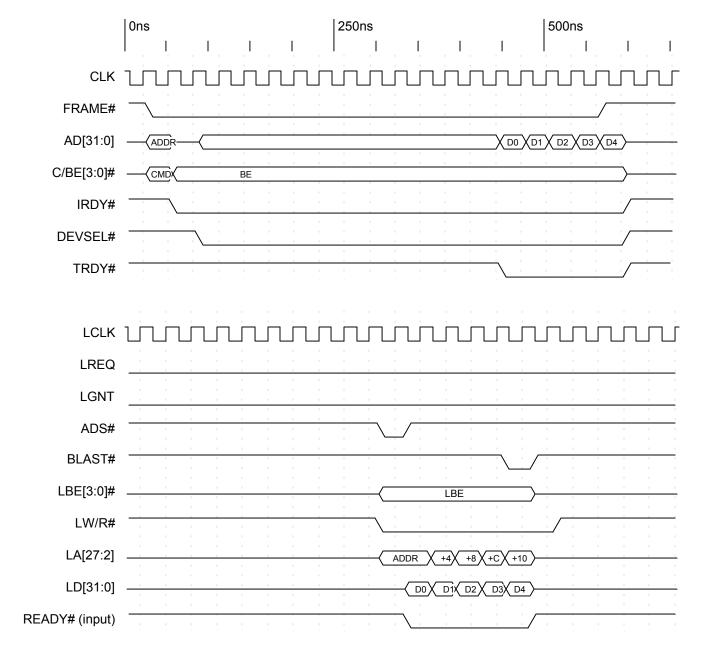

| 4-11 PCI Target Burst Write (16-Bit Local Bus), No Wait States                                                          | 4-13 |

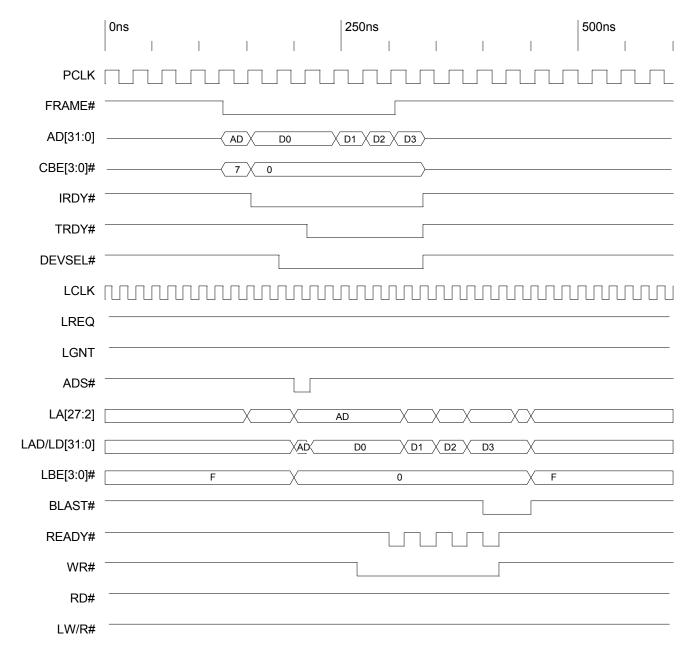

| 4-12 PCI Target Burst Write (16-Bit Local Bus), One Data-to-Data Wait State                                             | 4-14 |

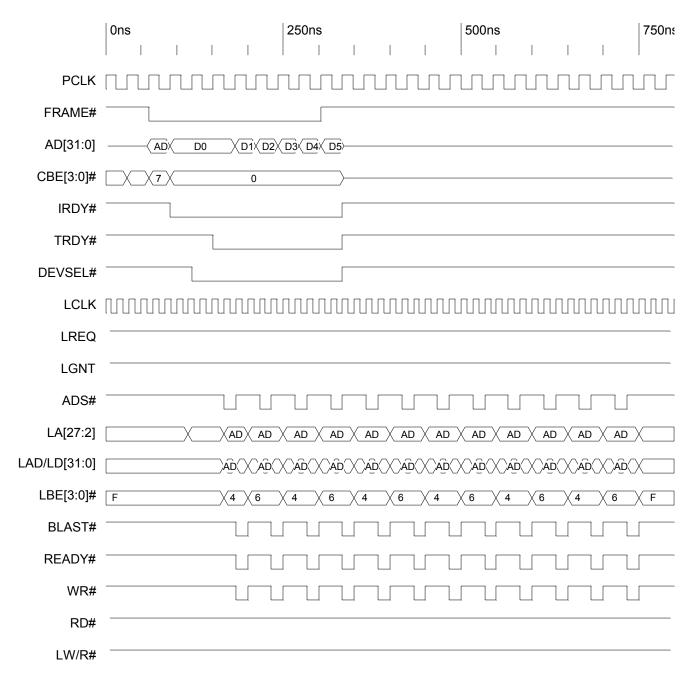

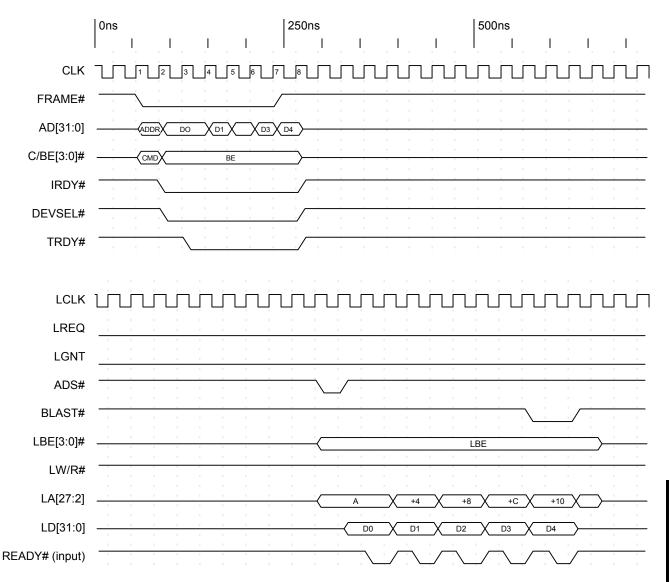

| 4-13 PCI Target Burst Writes (8-Bit Local Bus), One Data-to-Data Wait State                                             | 4-15 |

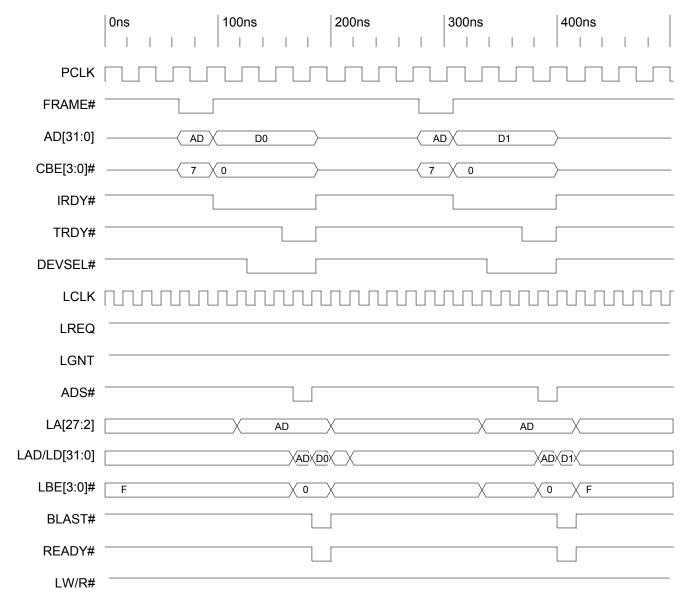

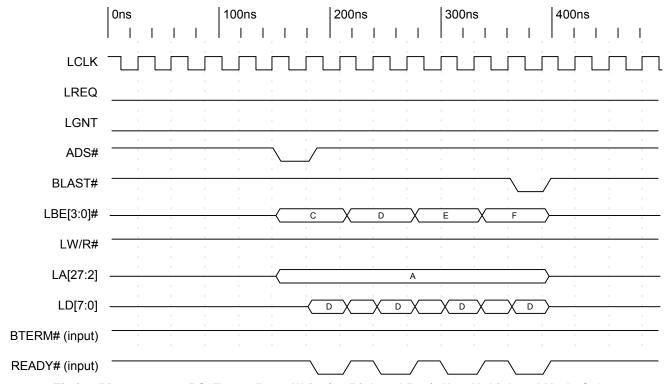

| 4-14 PCI Target Single Writes (16-Bit Local Bus)                                                                        | 4-16 |

| 4-15 PCI Target Single Writes (8-Bit Local Bus)                                                                         | 4-17 |

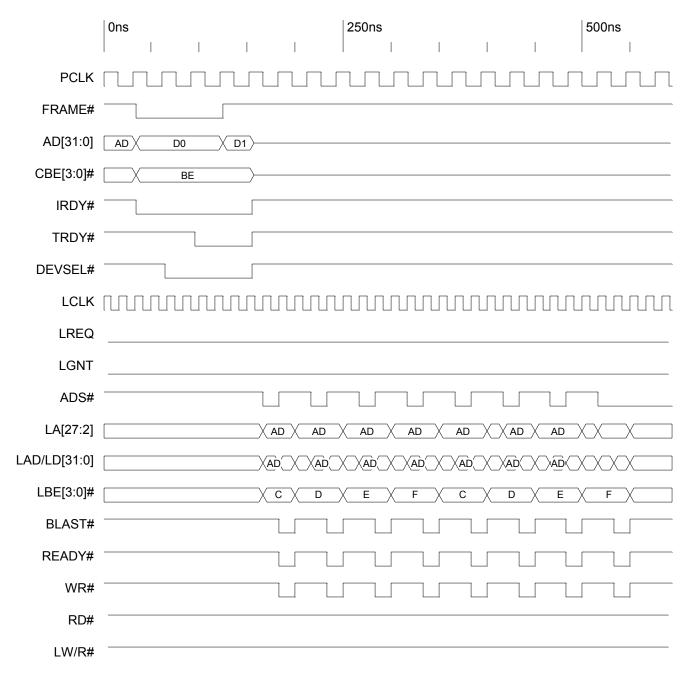

| 4-16 PCI Target Single Writes (8-Bit Local Bus), No Wait States                                                         | 4-18 |

| 4-17 PCI Target Back-to-Back Single Writes                                                                              | 4-19 |

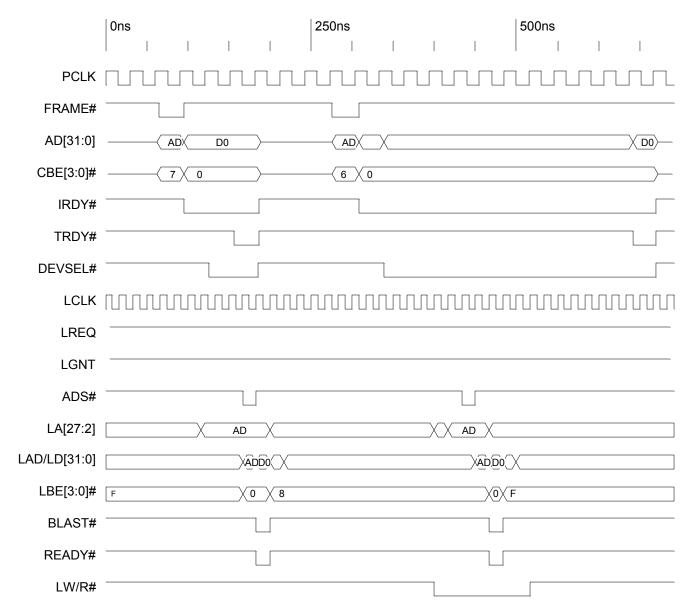

| 4-18 PCI Target Back-to-Back Write Followed by a Read                                                                   | 4-20 |

| 4-19 PCI Target Back-to-Back Read Followed by a Write                                                                   | 4-21 |

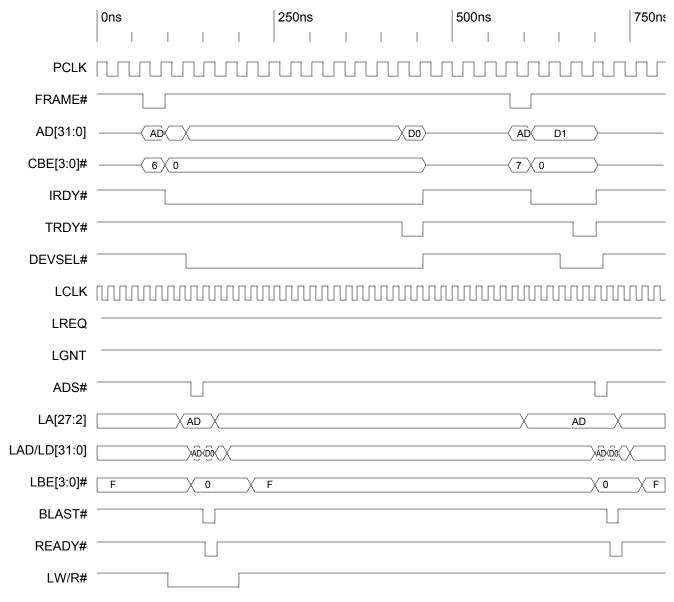

| 4-20 PCI Target Back-to-Back Reads                                                                                      | 4-22 |

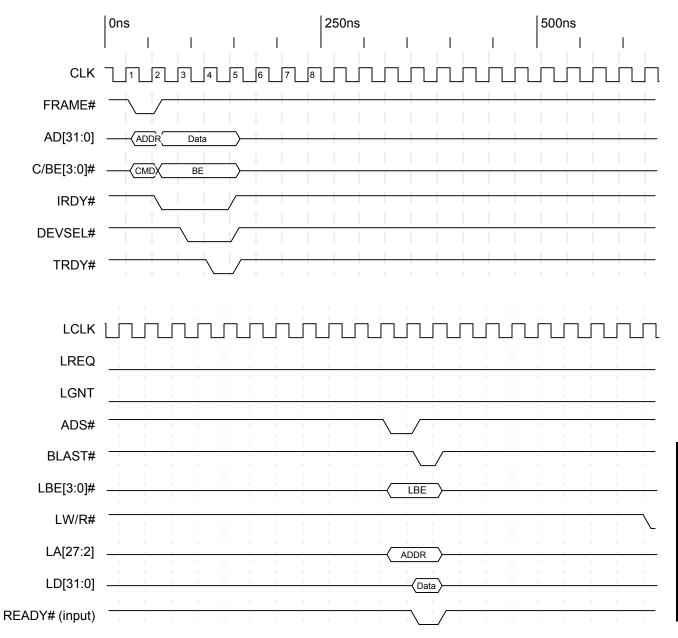

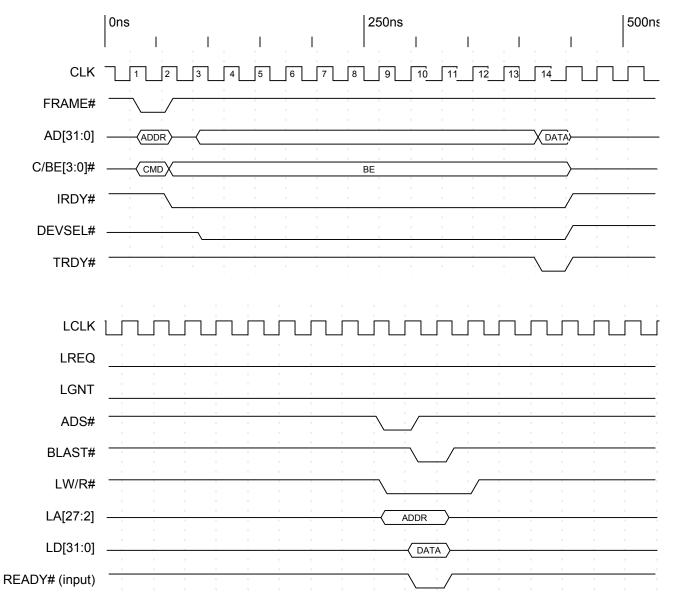

| 4-21 PCI Target Single Write (32-Bit Local Bus), Multiplexed Mode Only                                                  | 4-23 |

| 4-22 PCI Target Single Read (32-Bit Local Bus), Multiplexed Mode Only                                                   | 4-24 |

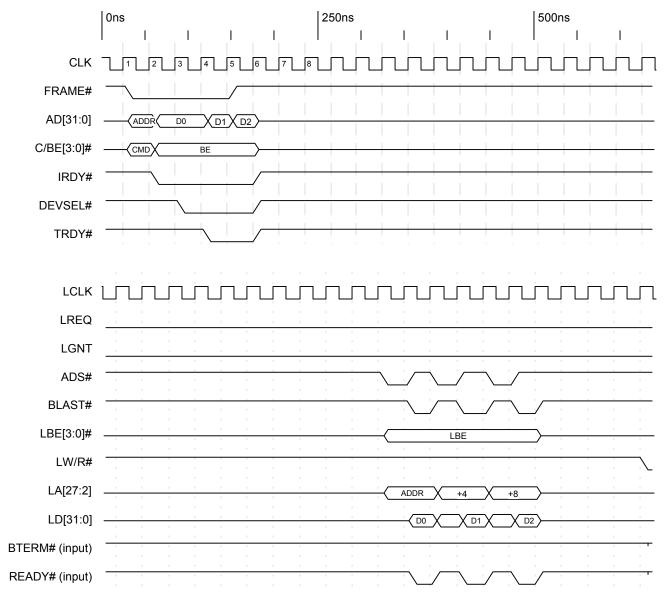

| 4-23 PCI Target Burst Write with Bterm Enabled (32-Bit Local Bus), Multiplexed Mode Only                                | 4-25 |

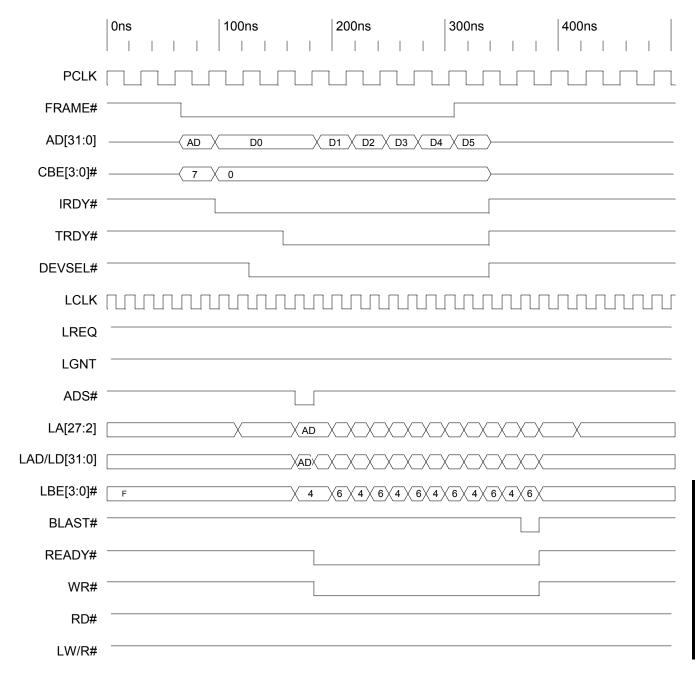

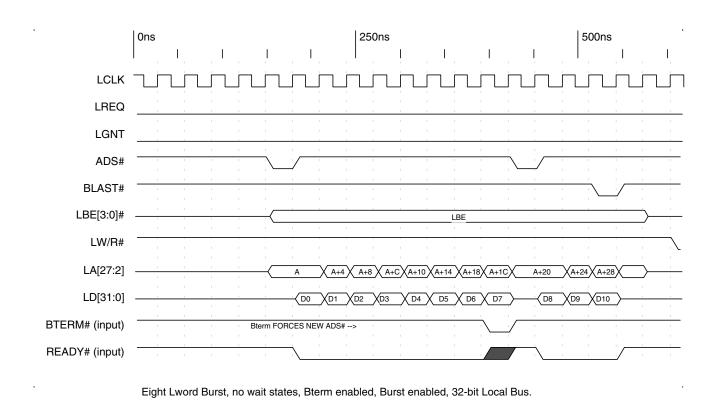

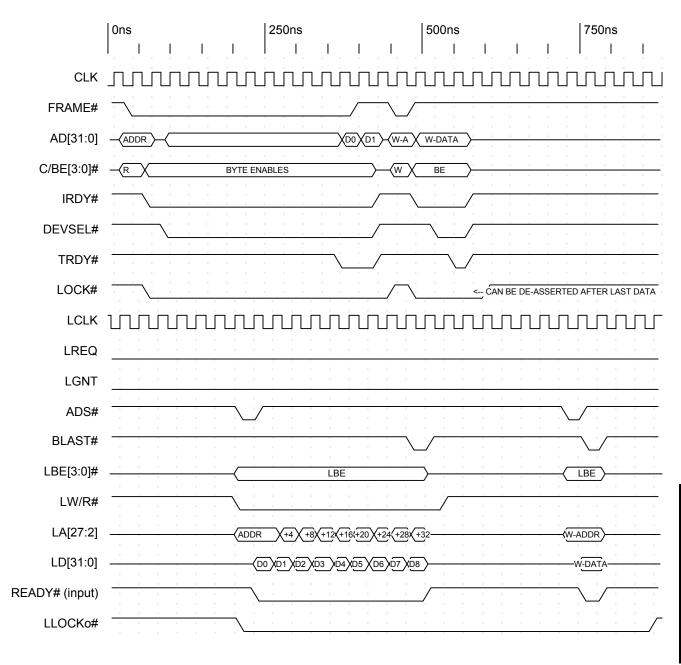

| 4-24 PCI Target Burst Read with Prefetch Enabled (32-Bit Local Bus), Prefetch Counter Set to 8, Multiplexed Mode Only   | 4-26 |

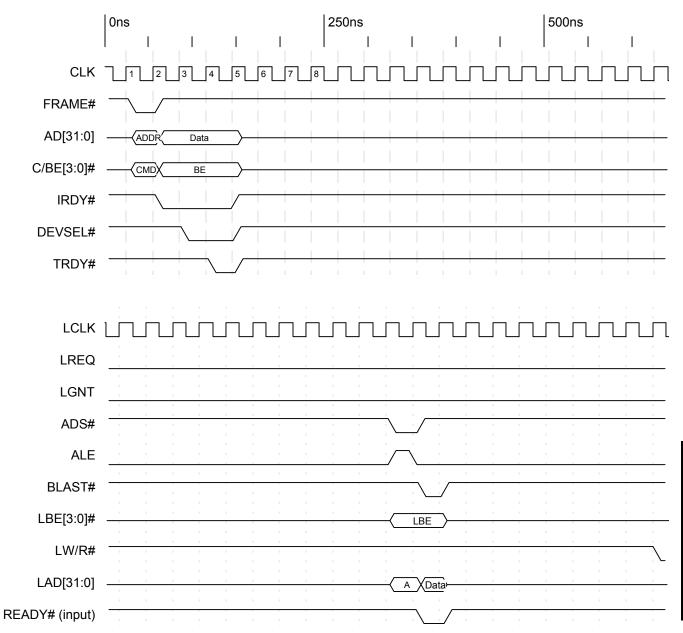

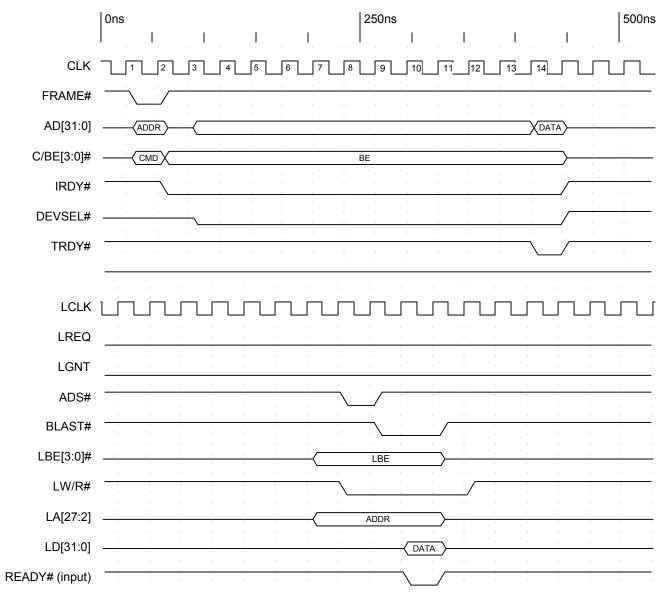

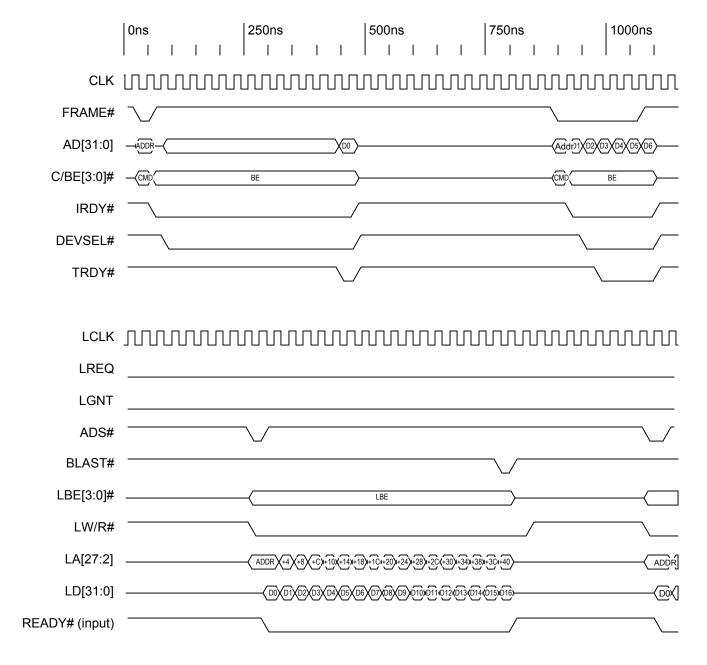

| 4-25 PCI Target Single Write (32-Bit Local Bus), Non-Multiplexed Mode Only                                              | 4-27 |

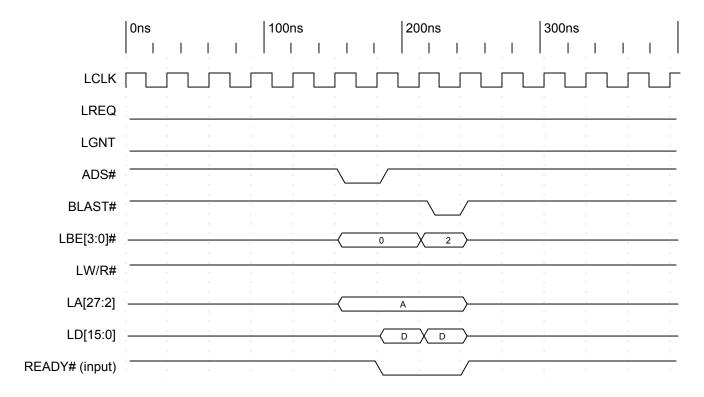

| 4-26 PCI Target Single Write (16-Bit Local Bus), Non-Multiplexed Mode Only                                              | 4-28 |

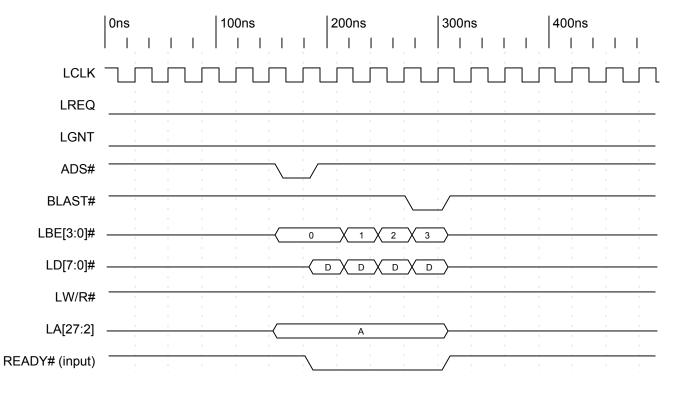

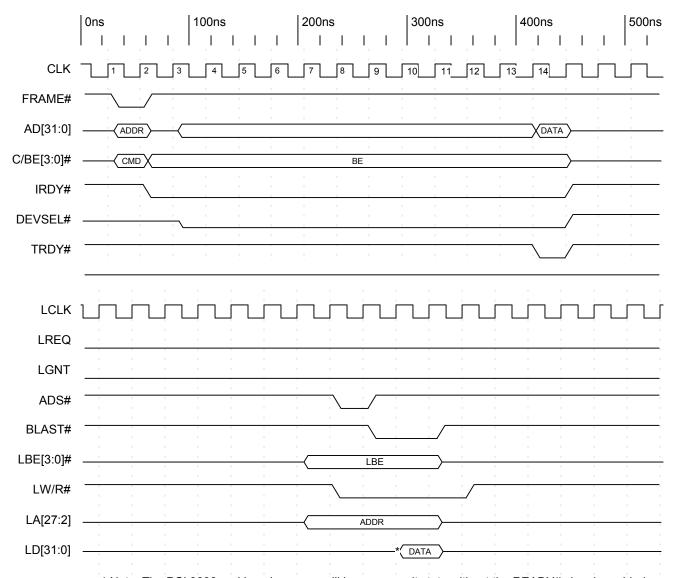

| 4-27 PCI Target Single Write (8-Bit Local Bus), Non-Multiplexed Mode Only                                               | 4-28 |

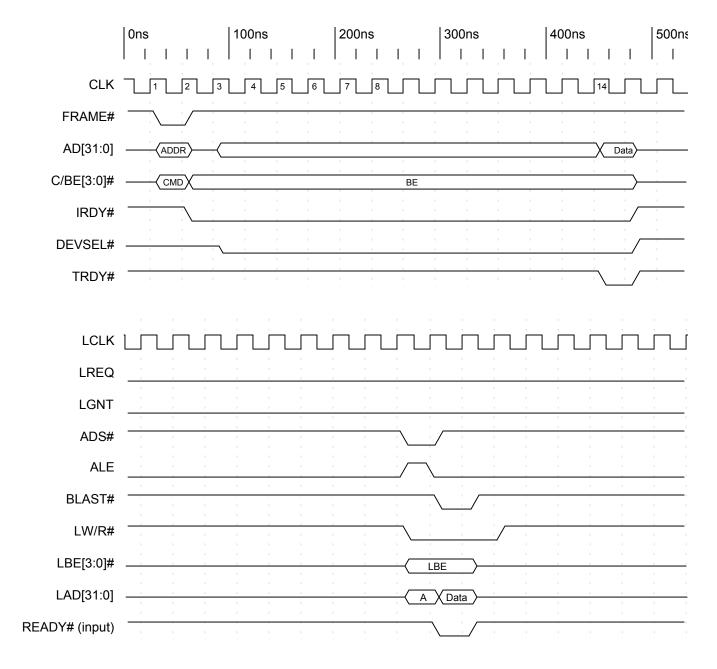

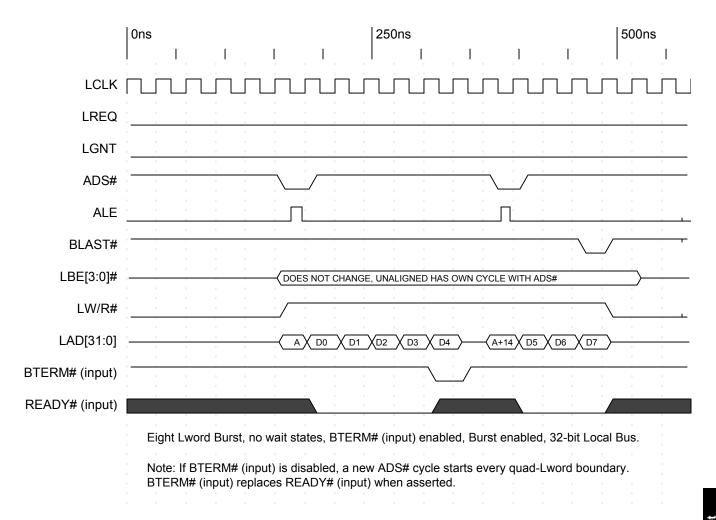

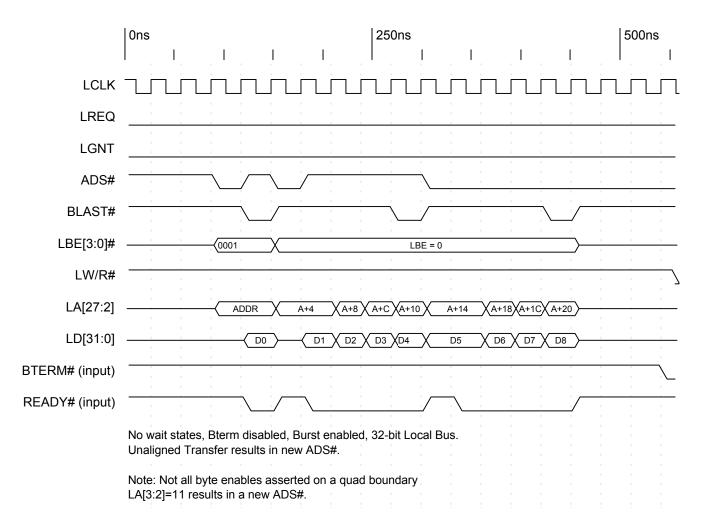

| 4-28 PCI Target Single Read (32-Bit Local Bus), Non-Multiplexed Mode Only                                               | 4-29 |