#### **ADVANCE INFORMATION**

(Subject to change without notice)

May 2, 2000

## ABSOLUTE MAXIMUM RATINGS at $T_A = +25^{\circ}C$

| • •                                              |

|--------------------------------------------------|

| Load Supply Voltage, V <sub>BB</sub> <b>50 V</b> |

| Output Current, I <sub>OUT</sub>                 |

| Transient (<500 ns) ±5 A                         |

| Logic Supply Voltage,                            |

| V <sub>DD</sub> 7.0 V                            |

| Sense Voltage, V <sub>SENSE</sub> <b>0.5 V</b>   |

| Logic Input Voltage Range,                       |

| $V_{IN}$ 0.3 V to $V_{DD}$ + 0.3 V               |

| High-Side Gate Voltage $V_{RR} + 8 V$            |

| Package Power Dissipation,                       |

| P <sub>D</sub> 2.2 W                             |

| Operating Temperature Range,                     |

| $T_A$ 20°C to +85°C                              |

| Junction Temperature, T <sub>1</sub> +150°C      |

| Storage Temperature Range,                       |

| T <sub>s</sub> 55°C to +150°C                    |

| 3                                                |

Output duty cycle, ambient temperature, and heat sinking may limit current rating. Under any set of conditions, do not exceed the specified current rating or a junction temperature of 150 °C.

## DUAL DMOS FULL-BRIDGE DRIVER

Designed to interface between external PWM control logic and inductive loads such as relays, solenoids, dc motors, or stepper motors, each full bridge can operate with output currents to  $\pm 2.5$  A and operating voltages to 50 V.

Low  $r_{DS(on)}$  DMOS output drivers provide low power dissipation during PWM operation. Internal charge pump circuitry is used to create a boosted voltage to fully enhance the high-side DMOS switches.

Three TTL-compatible logic-input terminals per bridge allow flexibility in configuring PWM control.

Internal circuit protection includes thermal shutdown with hysteresis, and crossover-current protection. Special power -up sequencing is not required.

The A3971SLB is supplied in a 24-lead plastic SOIC with a copper batwing tab. The power tab is at ground potential and needs no electrical isolation.

#### **FEATURES**

- ±2.5 A Load Current Capability per Bridge

- Parallel Outputs for 5 A Load-Current Capability

- Low  $r_{DS(on)}$  Outputs

Typically 325 mΩ source, 175 mΩ sink

- Synchronous Rectification via Control Logic

- Internal Undervoltage Monitor

- Crossover-Current Protection

- Source Connections for External Current Sensing

- Thermal Shutdown Circuitry

Always order by complete part number: A3971SLB

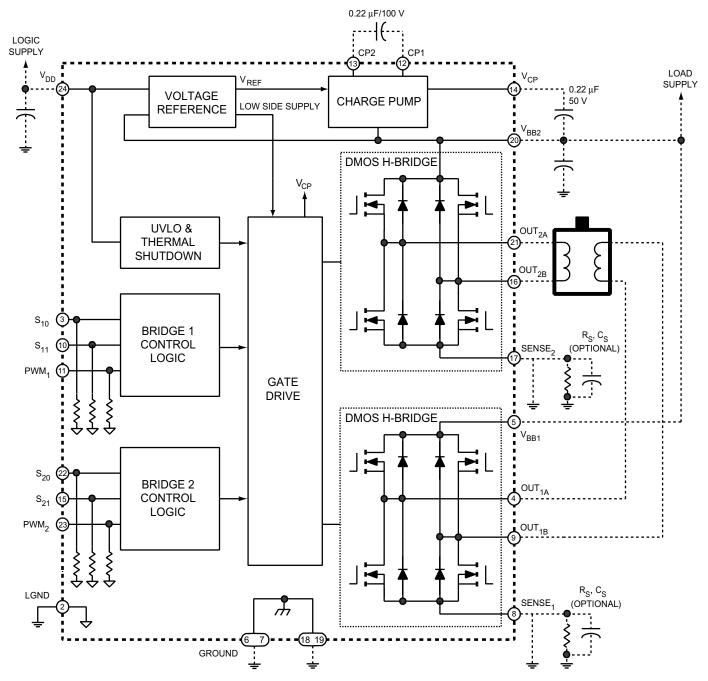

#### **FUNCTIONAL BLOCK DIAGRAM**

## ELECTRICAL CHARACTERISTICS at $T_A$ = +25°C, $V_{BB}$ = 50 V, $V_{DD}$ = 5.0 V (unless otherwise noted).

|                                      |                     |                                             | Limits |       |      |       |  |

|--------------------------------------|---------------------|---------------------------------------------|--------|-------|------|-------|--|

| Characteristic Symbol Test Condition |                     | Test Conditions                             | Min.   | Тур.  | Max. | Units |  |

| Load Supply Voltage Range            | $V_{\mathtt{BB}}$   | Operating                                   | 10     | _     | 50   | V     |  |

| Logic Supply Voltage Range           | $V_{DD}$            | Operating                                   | 4.5    | 5.0   | 5.5  | V     |  |

| Load Supply Current                  | l <sub>BB</sub>     | Operating, each supply, no load             | _      | _     | 3.0  | mA    |  |

| Logic Supply Current                 | I <sub>DD</sub>     | Operating                                   | _      | _     | 5.0  | mA    |  |

| Output Drivers                       |                     |                                             |        |       |      |       |  |

| Output Leakage Current               | I <sub>DSS</sub>    | V <sub>OUT</sub> = V <sub>BB</sub>          | _      | <1.0  | 20   | μΑ    |  |

|                                      |                     | V <sub>OUT</sub> = 0 V                      | _      | <-1.0 | -20  | mA    |  |

| Output ON Resistance                 | r <sub>DS(on)</sub> | High-side switch, I <sub>OUT</sub> = -2.5 A | -      | 325   | 375  | mΩ    |  |

|                                      |                     | Low-side switch, I <sub>OUT</sub> = 2.5 A   | _      | 175   | 200  | mΩ    |  |

| Body Diode Forward Voltage           | $V_{F}$             | Source diode, I <sub>F</sub> = 2.5 A        | _      | 1.2   | _    | V     |  |

|                                      |                     | Sink diode, I <sub>F</sub> = 2.5 A          | _      | 1.0   | _    | V     |  |

| High-Side Gate Voltage               | V <sub>CP</sub>     | C = 0.22 μF, reference V <sub>BB</sub>      | 6.0    | 6.5   | 7.0  | V     |  |

| Control Logic                        |                     |                                             |        |       |      |       |  |

| Logic Input Voltage                  | V <sub>IN(0)</sub>  |                                             | _      | _     | 0.8  | V     |  |

|                                      | V <sub>IN(1)</sub>  |                                             | 2.0    | _     | _    | V     |  |

| Logic Input Current                  | I <sub>IN(0)</sub>  | V <sub>IN</sub> = 0 V                       | _      | <1.0  | -5.0 | μΑ    |  |

|                                      | I <sub>IN(1)</sub>  | V <sub>IN</sub> = 5.0 V                     |        | 20    | 50   | μΑ    |  |

| Propagation Delay Time               | t <sub>PD</sub>     | 50% to 90%:                                 |        |       |      |       |  |

|                                      |                     | PWM change to source off                    | -      | 50    |      | ns    |  |

|                                      |                     | PWM change to sink off                      | _      | 60    |      | ns    |  |

|                                      |                     | PWM change to source on                     | _      | 565   |      | ns    |  |

|                                      |                     | PWM change to sink on                       | _      | 665   |      | ns    |  |

|                                      |                     | Disable to source on                        | —      | 150   |      | ns    |  |

|                                      |                     | Disable to sink on                          | _      | 250   | _    | ns    |  |

| Thermal Shutdown Temperature         | $T_J$               |                                             |        | 165   |      | °C    |  |

| Thermal Shutdown Hysteresis          | $\DeltaT_J$         |                                             |        | 15    |      | °C    |  |

| UVLO Threshold                       | $V_{UVLO}$          | Increasing V <sub>DD</sub>                  | 3.9    | 4.15  | 4.4  | V     |  |

| UVLO Hysteresis                      | $\Delta V_{UVLO}$   |                                             |        | 0.15  |      | V     |  |

NOTES: 1. Typical Data is for design information only.

<sup>2.</sup> Negative current is defined as coming out of (sourcing) the specified device terminal.

## 3971 DUAL DMOS FULL-BRIDGE DRIVER

## **Logic Truth Table**

| PWM <sub>x</sub> | S <sub>x0</sub> | S <sub>x1</sub> | OUT <sub>xA</sub> | OUT <sub>xB</sub> | Function       |  |

|------------------|-----------------|-----------------|-------------------|-------------------|----------------|--|

| Х                | 0               | 0               | Z                 | Z                 | Disable        |  |

| 0                | 0               | 1               | L                 | Н                 | Forward        |  |

| 0                | 1               | 0               | Н                 | L                 | Reverse        |  |

| 0                | 1               | 1               | L                 | L                 | Synchronous    |  |

| 1                | 0               | 1               | L                 | L                 | Rectification/ |  |

| 1                | 1               | 1               | L                 | L                 | Slow Decay     |  |

| 1                | 1               | 0               | L                 | L                 | Chop           |  |

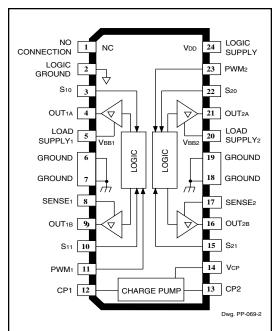

## **Terminal List**

| Terminal | Name                                 | Description                   |  |

|----------|--------------------------------------|-------------------------------|--|

| 1        | NC                                   | No (Internal) connection      |  |

| 2        | LGND                                 | Logic ground                  |  |

| 3        | S <sub>10</sub>                      | Control input, bridge 1       |  |

| 4        | OUT <sub>1A</sub>                    | Output A, bridge 1            |  |

| 5        | V <sub>BB1</sub>                     | Load supply voltage, bridge 1 |  |

| 6, 7     | GND                                  | Ground                        |  |

| 8        | SENSE₁                               | Sense resistor, bridge 1      |  |

| 9        | OUT <sub>1B</sub> Output B, bridge 1 |                               |  |

| 10       | S <sub>11</sub>                      | Control input, bridge 1       |  |

| 11       | PWM₁                                 | Control input, bridge 1       |  |

| 12       | CP1                                  | Charge-pump capacitor         |  |

| 13       | CP2                                  | Charge-pump capacitor         |  |

| 14       | V <sub>CP</sub>                      | Reservoir capacitor           |  |

| 15       | S <sub>21</sub>                      | Control input, bridge 2       |  |

| 16       | OUT <sub>2B</sub>                    | Output B, bridge 2            |  |

| 17       | SENSE <sub>2</sub>                   | Sense resistor, bridge 2      |  |

| 18, 19   | GND                                  | Ground                        |  |

| 20       | $V_{BB2}$                            | Load supply voltage, bridge 2 |  |

| 21       | OUT <sub>2A</sub>                    | Output A, bridge 2            |  |

| 22       | S <sub>20</sub>                      | Control input, bridge 2       |  |

| 23       | PWM <sub>2</sub>                     | Control input, bridge 2       |  |

| 24       | $V_{\scriptscriptstyle DD}$          | Logic supply voltage          |  |

#### **Functional Description**

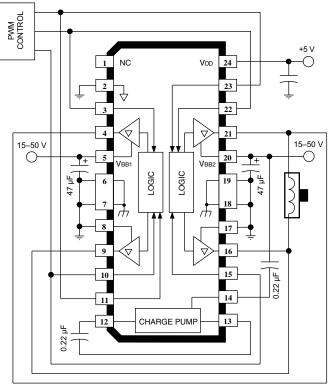

**Charge Pump.** The DMOS output stage requires a charge pump to bring the high-side gate-source voltage approximately 8 V above the  $V_{BB}$  supply. Two external components are required, a pumping capacitor connected between CP1 and CP2 and a reservoir capacitor connected between  $V_{BB}$  and  $V_{CP}$ . Ceramic 0.22  $\mu F$  capacitors are recommended.

**Control Logic.** Each bridge is controlled by three TTL-compatible inputs. The inputs are resistively pulled to ground (via 250 k $\Omega$ ). A crossover-delay circuit protects the outputs from a shoot-thru condition when going from a forward or reverse on state to synchronous rectification/ slow decay chop (both sink drivers on). If the logic is in the DISABLE state and changes to an on state the 415 ns crossover delay does not occur.

**Protection Circuitry.** In the event of a fault due to excessive junction temperature, or low voltage on  $V_{CP}$  or  $V_{DD}$ , the outputs of the device are disabled until the fault condition is removed.

Current Sensing. If external current-sensing circuitry is used, the sense resistor should have an independent ground return to the ground terminal of the device. Due to current transients during switching, a  $0.1~\mu F$  capacitor should be connected from the sense terminal to the batwing tab connection of the package. This capacitor reduces voltage swings at the terminal due to the fast di/dt, which in turn ensures that the sink driver gate-source voltage stays within the safe operating area. Allegro MicroSystems recommends a value of  $R_S$  given by:

$R_S = 0.5/I_{TRIP}$  max.

**Thermal protection.** Circuitry turns off all drivers when the junction temperature reaches 165°C, typically. It is intended only to protect the device from failures due to excessive junction temperatures and should not imply that output short circuits are permitted. Thermal shutdown has a hysteresis of approximately 15°C.

**Layout.** The printed wiring board should use a heavy ground plane. For optimum electrical and thermal performance, the driver should be soldered directly onto the board. If external current sensing is used, the ground side of  $R_S$  should have an individual path to the ground terminal(s) of the device. This path should be as short as is possible physically and should not have any other components connected to it. The load supply terminal should be decoupled with an electrolytic capacitor (>47  $\mu$ F is recommended) placed as close to the device as is possible.

**Parallel Operation.** For high-power applications, the two DMOS full bridges in the A3971 may be connected in parallel as shown below. The current will be shared equally in each full bridge due to the positive temperature coefficient of the DMOS  $r_{DS(on)}$ .

Dwg. EP-069

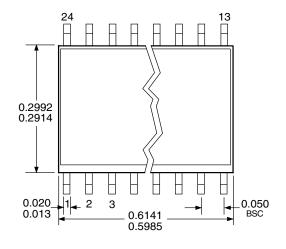

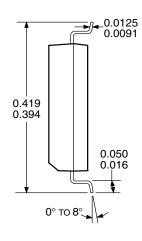

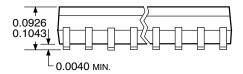

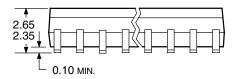

### **Dimensions in Inches**

(for reference only)

Dwg. MA-008-24A in

NOTES:1. Exact body and lead configuration at vendor's option within limits shown.

- 2. Lead spacing tolerance is non-cumulative

- 3. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

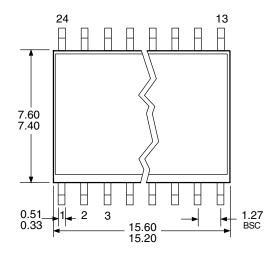

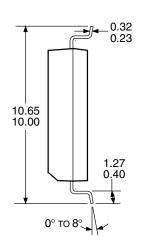

### **Dimensions in Millimeters**

(controlling dimensions)

Dwg. MA-008-24A mm

NOTES:1. Exact body and lead configuration at vendor's option within limits shown.

- 2. Lead spacing tolerance is non-cumulative

- 3. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

# 3971 DUAL DMOS FULL-BRIDGE DRIVER

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.